4 - 2

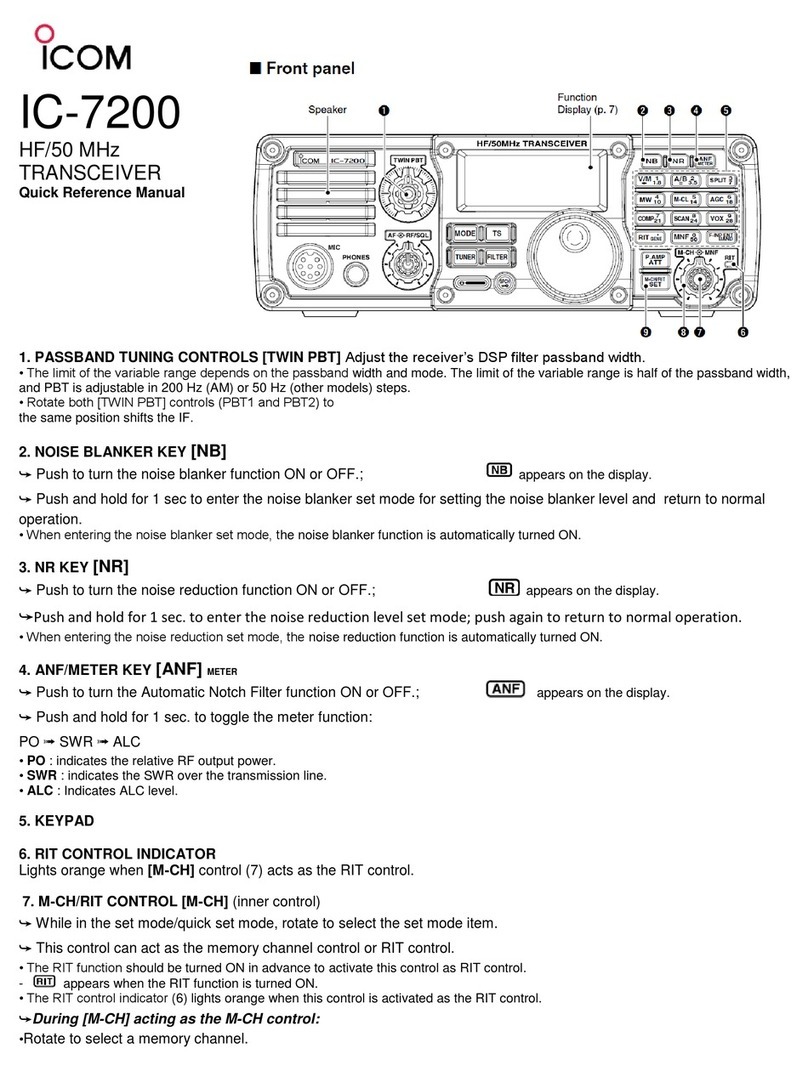

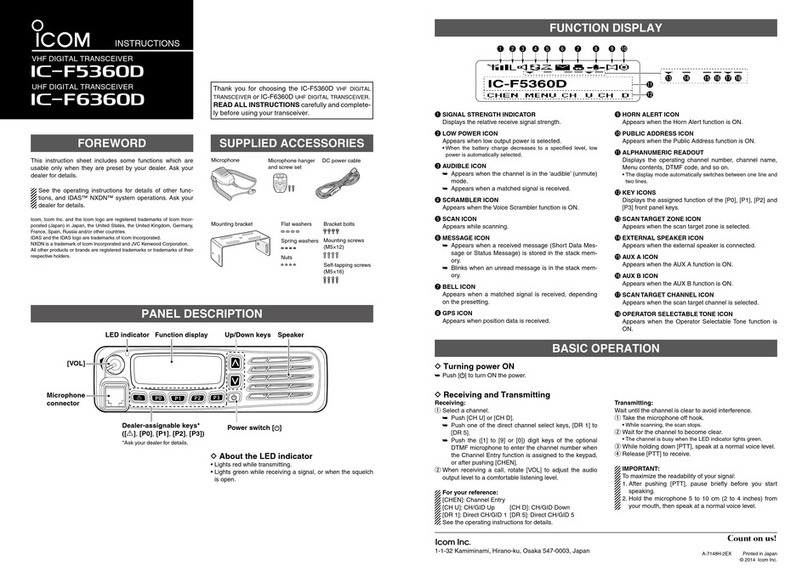

4-1-5 AF AMPLIFIER CIRCUIT

The AF amplifier circuit amplifies the demodulated AF sig-

nals to drive a speaker.

The AF signals from the FM IF IC (IC1, pin 9) pass through

the high-pass filter (IC6, pins 3 and 1) to suppress unwant-

ed harmonic components. The signals pass through the

RX mute switch (Q34) which is controlled by “RMUT” sig-

nal from the CPU (IC13, pin 56), and are then applied to

another high-pass filter (IC6, pins 13 and 14). The filtered

signals pass through the low-pass filter (IC6, pins 6 and 7)

via the analog switch (IC10, pins 1 and 2). The signals are

applied to the analog switch (IC10, pin 10) again, and are

then applied to the AF power amplifier (IC12, pin 4) via the

AF volume (R226). The amplified AF signals are output from

pin 10, and are then applied to the internal speaker which is

connected with J1 via the [SP] jack.

4-1-6 RECEIVE MUTE CIRCUITS

• NOISE SQUELCH

A squelch circuit cuts out AF signals when no RF signals

are received. By detecting noise components in the AF sig-

nals, the squelch circuit switches the AF mute switch.

Some noise components in the AF signals from the FM IF

IC (IC1, pin 9) are applied to the D/A converter (IC8, pin 1)

as “DET” signal, and are then output from pin 2. The signals

are applied to the active filter section in the FM IF IC (IC1,

pin 8). The active filter section filters and amplifies noise

components. The amplified signals are converted into the

pulse-type signals at the noise detector section and output

from pin 13 as “NOIS” signal.

The “NOIS” signal from the FM IF IC is applied to the CPU

(IC13, pin 53). Then the CPU analyzes the noise condition

and outputs the AF mute control signal from the CPU (IC13)

as “RMUT” signal from pin 56. The signal is applied to the

RX mute switch (Q34) to control the AF signal muting.

• CTCSS AND DTCS

The tone squelch circuit detects tone signals and opens the

squelch only when receiving a signal containing a matched

subaudible tone (CTCSS or DTCS). When the tone squelch

is in use, and a signal with a mismatched or no subaudible

tone is received, the tone squelch circuit mutes the AF sig-

nals even when noise squelch is open.

A portion of the “DET” signals from the FM IF IC (IC1,

pin 9) passes through the low-pass filter (IC7, pins 5 and 7)

to remove AF (voice) signals, and are then applied to the

amplifier (IC7, pin 3). The amplified signals are applied to

the CTCSS or DTCS decoder inside of the CPU (IC13,

pin 60) as the “CDEC” signal. The CPU outputs AF mute

control signal from pin 56, and is then applied to the RX

mute switch (Q34) and analog switch (IC10, pins 12 and 13)

to control AF signals muting as “RMUT” signal.

4-2 TRANSMITTER CIRCUITS

4-2-1 MICROPHONE AMPLIFIER CIRCUIT

The microphone amplifier circuit amplifies audio signals

within +6 dB/octave pre-emphasis characteristics from the

microphone to a level needed for the modulation circuit.

The AF signals from the microphone are passed through

the microphone mute switch (Q35), and are then applied

to the amplifier (IC6, pins 9 and 8) via the high-pass filter

(IC6, pins 13 and 14). The amplified signals are applied to

the analog switch (IC10, pin 4), and outputs from pin 3. The

signals pass through the low-pass filter (IC6, pins 6 and 7),

then applied to the analog switch (IC10, pin 9) again and

output from pin 8.

The signals are applied to the D/A converter (IC8, pin 4).

The converted signals output from pin 3, and applied to the

modulation circuit (D18) as “MOD” signal.

Analog SW

(IC10)

"DET" AF signal

from FM IF IC (IC1, pin 9)

8

AF

volume

AF

AMP

MIC

MUTE

IC12

Q35

Speaker

R226

IC8 D18

RX

MUTE

Q34

LPF

IC6 B

HPF

IC6 D

HPF

IC6 A

Microphone

IC6 C

AMP

1

4

3

2

9

10

D/A converter FM mod.

"CTCSS/DTCS" signal from

D/A conveter IC (IC8, pin 10)

"TONE" signal from CPU (IC13) via low-pass

filters (IC5 A / IC5 B pin 7)

to TX VCO circuit

(Q13, D16, D17)

11

• ANALOG SWITCHING CIRCUITS