IDT Tsi572 User manual

IDTTsi572

Serial RapidIO Switch

Hardware Manual

May 18, 2012

Titl

GENERAL DISCLAIMER

Integrated Device Technology, Inc. (“IDT”) reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or

performance.IDTdoesnotassumeresponsibilityforuseofanycircuitrydescribedhereinotherthanthecircuitryembodiedinanIDTproduct.Disclosureoftheinformation

herein does not convey a license or any other right, by implication or otherwise, in any patent, trademark, or other intellectual property right of IDT. IDT products may

contain errata which can affect product performance to a minor or immaterial degree. Current characterized errata will be made available upon request. Items identified

herein as “reserved” or “undefined” are reserved for future definition. IDT does not assume responsibility for conflicts or incompatibilities arising from the future definition

of such items. IDT products have not been designed, tested, or manufactured for use in, and thus are not warranted for, applications where the failure, malfunction, or

any inaccuracy in the application carries a risk of death, serious bodily injury, ordamage to tangible property. Code examples provided herein by IDT are for illustrative

purposes only and should not be relied upon for developing applications. Any use of such code examples shall be at the user's sole risk.

Copyright © 2012 Integrated Device Technology, Inc.

All Rights Reserved.

The IDT logo is registered to Integrated Device Technology, Inc. IDT and CPS are trademarks of Integrated Device Technology, Inc.

Tsi572 Hardware Manual

May 18, 2012

Integrated Device Technology

www.idt.com

3

Contents

1. Signals and Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1.1 Pinlist . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1.2 Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

1.3 Package Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

1.4 Thermal Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

2. Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.1 Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.2 Recommended Operating Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

2.3 Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

2.4 Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

3. Layout Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

3.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

3.2 Impedance Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

3.3 Tracking Topologies. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

3.4 Power Distribution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

3.5 Decoupling Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

3.6 Clocking and Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

3.7 Modeling and Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

3.8 Testing and Debugging Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

3.9 Reflow Profile. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

A. Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

A.1 Line Rate Support. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

A.2 P_CLK Programming. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

B. Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

B.1 Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

B.2 Part Numbering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

4

Tsi572 Hardware Manual

May 18, 2012 Integrated Device Technology

www.idt.com

Tsi572 Hardware Manual

May 18, 2012

Integrated Device Technology

www.idt.com

5

About this Document

This section discusses general document information about the Tsi572. The following topics are

described:

•“Scope” on page 5

•“Document Conventions” on page 5

•“Revision History” on page 6

Scope

The Tsi572 Hardware Manual discusses electrical, physical, and board layout information for

the Tsi572. It is intended for hardware engineers who are designing system interconnect

applications with these devices.

Document Conventions

This document uses a variety of conventions to establish consistency and to help you quickly

locate information of interest. These conventions are briefly discussed in the following sections.

Non-differential Signal Notation

Non-differential signals are either active-low or active-high. An active-low signal has an active

state of logic 0 (or the lower voltage level), and is denoted by a lowercase “b”. An active-high

signal has an active state of logic 1 (or the higher voltage level), and is not denoted by a special

character. The following table illustrates the non-differential signal naming convention.

State Single-line signal Multi-line signal

Active low NAME_b NAMEn[3]

Active high NAME NAME[3]

6

Serial RapidIO Switch

May 18, 2012 Integrated Device Technology

www.idt.com

Differential Signal Notation

Differential signals consist of pairs of complement positive and negative signals that are

measured at the same time to determine a signal’s active or inactive state (they are denoted by

“_p” and “_n”, respectively). The following table illustrates the differential signal naming

convention.

Symbols

Revision History

May 18, 2012, Formal

• Updated the first paragraph in “Power Sequencing” on page 33

• Changed the SP_IO_SPEED setting in Table 21 for 125 MHz / 1.25 Baud rate to 1,1

November 18, 2010, Formal

• Added a note to Table 13

August 2009, Formal

This is the current release of the Serial RapidIO Switch. There have been no technical changes

to the document; the formatting has been updated to reflect IDT.

June 2009, Formal

Changes have been implemented throughout the document.

State Single-line signal Multi-line signal

Inactive NAME_p = 0

NAME_n = 1 NAME_p[3] = 0

NAME_n[3] =1

Active NAME_p = 1

NAME_n = 0 NAME_p[3] is 1

NAME_n[3] is 0

Tip

This symbol indicates a basic design concept or information considered helpful.

This symbol indicates important configuration information or suggestions.

This symbol indicates procedures or operating levels that may result in misuse or

damage to the device.

Tsi572 Hardware Manual

May 18, 2012

Integrated Device Technology

www.idt.com

7

July 2008, Advance

The changes to this documents includes adding industrial variants of the device to “Ordering

Information” on page 87.

June 2008, Advance

This was the first version of the Serial RapidIO Switch.

8

Serial RapidIO Switch

May 18, 2012 Integrated Device Technology

www.idt.com

9

Tsi572 Hardware Manual

May 18, 2012

Integrated Device Technology

www.idt.com

1. Signals and Package

This chapter describes the packaging (mechanical) features for the Tsi572. It includes the

following information:

•“Pinlist” on page 9

•“Signals” on page 10

•“Package Characteristics” on page 24

•“Thermal Characteristics” on page 27

1.1 Pinlist

The pinlist and ballmap information for the Tsi572 are available by visiting www.idt.com. For

more information, see the following documents:

• Tsi572 Pinlist

• Tsi572 Ballmap

10

Tsi572 Hardware Manual

May 18, 2012 Integrated Device Technology

www.idt.com

1.2 Signals

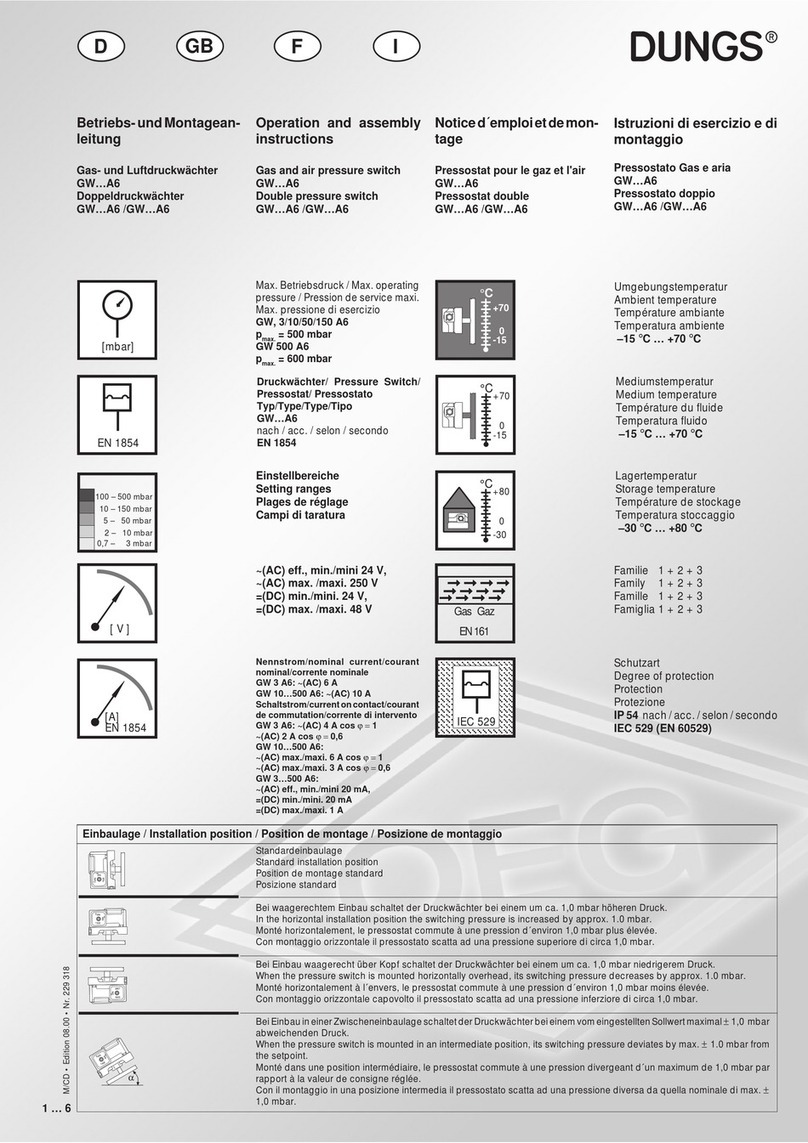

Figure 1: Signal Grouping

1

1

1

1

TRST_b

1

1

1

1

JTAG

TAP

I

2

C

TCK

TDI

TDO

TMS

TRST_b

I2C_SCLK

I2C_SD

1

1

HARD_RST_b

SW_RST_b 1

INT_b

Reset

2RefClks

S_CLK_[p,n] 1

P_CLK

VSS

VDD

Interrupt

VDD_IO

1

I2C_DISABLE

I2C_MA

I2C_SEL 2

I2C_SA[1,0]

1

1

1

BCE

1

MCES Multicast event

Control symbol

2

REF_AVDD

SP_IO_SPEED[1:0]

Port

Configuration 2

Ports{0,2,4,6}

SP_VDD

SP{2,4}_T[A,B]_[p,n]

16

SP_VDD

SP0_T[A,B,C,D]_[p,n]

SP0_R[A,B,C,D]_[p,n]

SP0_REXT

8

8

SP0_MODESEL

1

1

SP1_PWRDN

1

SP{2,4}_R[A,B]_[p,n]

SP{2,4}_REXT

SP{2,4}_PWRDN

4

4

SP{3,5}_PWRDN

4

SP6_T[A,B,C,D]_[p,n]

SP6_R[A,B,C,D]_[p,n]

SP6_REXT

8

8

SP6_MODESEL

1

1

SP7_PWRDN

1SP6_PWRDN

1

Ports{0,2,4,6}

SP_AVDD SP_AVDD

VSS

VDD

VDD_IO

REF_AVDD

4x Mode:0

1x Mode: 0,1

Ports

4x Mode:6

1x Mode: 6,7

Ports

1x Mode: 2,3,4,5

Ports

TX_SWAP

RX_SWAP

1

1

4x Mode Lane Swap

16

11

Tsi572 Hardware Manual

May 18, 2012

Integrated Device Technology

www.idt.com

1.2.1 Conventions

The following conventions are used in the signal description table:

• Signals with the suffix “_p” are the positive half of a differential pair.

• Signals with the suffix “_n” are the negative half of a differential pair.

• Signals with the suffix “_b” are active low.

Signals are classified according to the types defined in Table 1.

1.2.2 Endian Ordering

This document follows the bit-numbering convention adopted by RapidIO Interconnect

Specification (Revision 1.3), where [0:7] is used to represent an 8 bit bus with bit 0 as the

most-significant bit.

Table 1: Signal Types

Pin Type Definition

I Input

O Output

I/O Input/Output

OD Open Drain

SRIO Differential driver/receiver defined by RapidIO

Interconnect Specification (Revision 1.3)

PU Pulled Up internal to the Tsi572

PD Pulled Down internal to the Tsi572

LVTTL CMOS I/O with LVTTL thresholds

Hyst Hysteresis

Core Power Core supply

Core Ground Ground for core logic

I/O Power I/O supply

N/C No connect

These signals must be left unconnected.

12

Tsi572 Hardware Manual

May 18, 2012 Integrated Device Technology

www.idt.com

1.2.3 Port Numbering

The following table shows the mapping between port numbers and the physical ports. These port

numbers are used within the destination ID lookup tables for ingress RapidIO ports and in numerous

register configuration fields.

Table 2: Port Numbering

Port Number RapidIO Port Mode

0 Serial Port 0 (SP0) 1x or 4x

1 Serial Port 1 (SP1) 1x

2 Serial Port 2 (SP2) 1x

3 Serial Port 3 (SP3) 1x

4 Serial Port 4 (SP4) 1x

5 Serial Port 5 (SP5) 1x

6 Serial Port 6 (SP6) 1x or 4x

7 Serial Port 7 (SP7) 1x

13

Tsi572 Hardware Manual

May 18, 2012

Integrated Device Technology

www.idt.com

1.2.4 Signal Grouping

The following table lists the signals by group and their recommended termination.

Table 3: Signal Descriptions and Recommended Termination

Pin Name Type Description Recommended

Terminationa

Signal Port Numbering

n = 0, 2, 4, 6

Serial Port Transmit

SP{n}_TA_p O, SRIO Port n Lane A Differential Non-inverting Transmit

Data output (4x mode)

Port n Lane A Differential Non-inverting Transmit

Data output (1x mode)

No termination required.

SP{n}_TA_n O, SRIO Port n Lane A Differential Inverting Transmit Data

output (4x mode)

Port n Lane A Differential Inverting Transmit Data

output (1x mode)

No termination required.

SP{n}_TB_p O, SRIO Port n Lane B Differential Non-inverting Transmit

Data output (4x mode)

Port n+1 Lane B Differential Non-inverting

Transmit Data output (1x mode)

No termination required.

SP{n}_TB_n O, SRIO Port n Lane B Differential Inverting Transmit Data

output (4x mode)

Port n+1 Lane B Differential Inverting Transmit

Data output (1x mode)

No termination required.

SP[0,6]_TC_p O, SRIO Port n Lane C Differential Non-inverting Transmit

Data output (4x mode) No termination required.

SP[0,6]_TC_n O, SRIO Port n Lane C Differential Inverting Transmit Data

output(4x mode) No termination required.

SP[0,6]_TD_p O, SRIO Port n Lane D Differential Non-inverting Transmit

Data output (4x mode) No termination required.

SP[0,6]__TD_ O, SRIO Port n Lane D Differential Inverting Transmit Data

output (4x mode) No termination required.

14

Tsi572 Hardware Manual

May 18, 2012 Integrated Device Technology

www.idt.com

Serial Port Receive

SP{n}_RA_p I, SRIO Port n Lane A Differential Non-inverting Receive

Data input (4x node)

Port n Lane A Differential Non-inverting Receive

Data input (1x mode)

DC blocking capacitor of

0.1uF in series

SP{n}_RA_n I, SRIO Port n Lane A Differential Inverting Receive Data

input (4x mode)

Port n Lane A Differential Inverting Receive Data

input (1x mode)

DC blocking capacitor of

0.1uF in series

SP{n}_RB_p I, SRIO Port n Lane B Differential Non-inverting Receive

Data input (4x mode)

Port n+1 Lane B Differential Non-inverting

Receive Data input (1x mode)

DC blocking capacitor of

0.1uF in series

SP{n}_RB_n I, SRIO Port n Lane B Differential Inverting Receive Data

input (4x mode)

Port n+1 Lane B Differential Inverting Receive

Data input (1x mode)

DC blocking capacitor of

0.1uF in series

SP[0,6]_RC_p I, SRIO Port n Lane C Differential Non-inverting Receive

Data input(4x mode) DC blocking capacitor of

0.1uF in series

SP[0,6]_RC_n I, SRIO Port n Lane C Differential Inverting Receive Data

input (4x mode) DC blocking capacitor of

0.1uF in series

SP[0,6]_RD_p I, SRIO Port n Lane D Differential Non-inverting Receive

Data input(4x mode) DC blocking capacitor of

0.1uF in series

SP[0,6]_RD_n I, SRIO Port n Lane D Differential Inverting Receive Data

input (4x mode) DC blocking capacitor of

0.1uF in series

Table 3: Signal Descriptions and Recommended Termination

Pin Name Type Description Recommended

Terminationa

15

Tsi572 Hardware Manual

May 18, 2012

Integrated Device Technology

www.idt.com

Serial Port Configuration

SP{n}_REXT Analog Used to connect a resistor to VSS to provide a

reference current for the driver and equalization

circuits.

Must be connected to VSS

with a 191-ohm (1%)

resistor.

SP{n}_MODESEL I/O,

LVTTL,

PD

Selects the serial port operating mode for ports

0and 6

0 = Port 0 or 6 operating in 4x mode

1 = Ports n and n+1 operating in 1x mode

Note: Output capability of this pin is only used in

test mode.

Must remain stable for 10 P_CLK cycles after

HW_RST_b is de-asserted in order to be sampled

correctly.

This signal is ignored after reset.

Pin must be tied off

according to the required

configuration. Either a 10K

pull up to VDD_IO or a

10K pull-down to VSS_IO.

Internal pull-down may be

used for logic 0.

SP{n}_PWRDN I/O,

LVTTL,

PU

Port n Transmit and Receive Power Down control

This signal controls the state of Port n and Port

n+1

The PWRDN controls the state of all four lanes

(A/B/C/D) of SERDES Macro.

0 = Port n Powered Up. Port n+1 controlled by

SP{n+1}_PWRDN.

1 = Port n Powered Down. Port n+1 Powered

Down.

Override SP{n}_PWRDN using PWDN_x1 field in

“SRIO MAC x Clock Selection Register” in the

Tsi572 User Manual.

Output capability of this pin is only used in test

mode.

Must remain stable for 10 P_CLK cycles after

HW_RST_B is de-asserted in order to be sampled

correctly.

This signal is ignored after reset.

Pin must be tied off

according to the required

configuration. Either a 10K

pull up to VDD_IO or a

10K pull-down to VSS_IO.

Internal pull-up may be

used for logic 1.

Table 3: Signal Descriptions and Recommended Termination

Pin Name Type Description Recommended

Terminationa

16

Tsi572 Hardware Manual

May 18, 2012 Integrated Device Technology

www.idt.com

SP{n+1}_PWRDN I/O,

LVTTL,

PU

Port n+1 Transmit and Receive Power Down

control

This signal controls the state of Port n+1. Note

that Port n+1 is never used when 4x mode is

selected for a Serial Rapid IO MAC, and it must

be powered down.

0 = Port n+1 Powered Up

1 = Port n+1 Powered Down

Override SP{n+1}_PWRDN using PWDN_x4 field

SRIO MAC x Clock Selection Register.

Output capability of this pin is only used in test

mode.

Must remain stable for 10 P_CLK cycles after

HW_RST_B is de-asserted in order to be sampled

correctly.

This signal is ignored after reset.

Pin must be tied off

according to the required

configuration. Either a 10K

pull up to VDD_IO or a

10K pull-down to VSS_IO.

Internal pull-up may be

used for logic 1.

Table 3: Signal Descriptions and Recommended Termination

Pin Name Type Description Recommended

Terminationa

17

Tsi572 Hardware Manual

May 18, 2012

Integrated Device Technology

www.idt.com

Serial Port Speed Select

SP_IO_SPEED[1] I/O,

LVTTL,

PU

Serial Port Transmit and Receive operating

frequency select, bit 1. When combined with

SP_IO_SPEED[0], this pin selects the default

serial port frequency for all ports.

00 = 1.25 Gbit/s

01 = 2.5 Gbit/s

10 = 3.125 Gbit/s (default)

11 = Illegal

Selects the speed at which the ports operates

when reset is removed. This could be at either

HARD_RST_b being de-asserted or by the

completion of a self-reset.

These signals must remain stable for 10 P_CLK

cycles after HW_RST_b is de-asserted in order to

be sampled correctly.

These signals are ignored after reset and

software is able to over-ride the port frequency

setting in the SRIO MAC x Digital Loopback and

Clock Selection register.

The SP_IO_SPEED[1:0] setting is equal to the

IO_SPEED field in SRIO MAC x Clock Selection

Register.

Output capability of this pin is only used in test

mode.

Pin must be tied off

according to the required

configuration. Either a 10K

pull-up to VDD_IO or a

10K pull-down to VSS_IO.

Internal pull-down may be

used for logic 0.

SP_IO_SPEED[0] I/O,

LVTTL,

PD

See SP_IO_SPEED[1] Pin must be tied off

according to the required

configuration. Either a 10K

pull-up to VDD_IO or a

10K pull-down to VSS_IO.

Internal pull-up may be

used for logic 1.

Table 3: Signal Descriptions and Recommended Termination

Pin Name Type Description Recommended

Terminationa

18

Tsi572 Hardware Manual

May 18, 2012 Integrated Device Technology

www.idt.com

Serial Port Lane Ordering Select

SP_RX_SWAP I, LVTTL,

PD Configures the order of 4x receive lanes on serial

ports [0,6]

0 = A, B, C, D

1 = D, C, B, A

This signal is ignored in 1X mode.

Must remain stable for 10 P_CLK cycles after

HARD_RST_b is de-asserted in order to be

sampled correctly.

This signal is ignored after reset.

Note: Ports that require the use of lane swapping

for ease of routing will only function as 4x mode

ports. The re-configuration of a swapped port to

dual 1x mode operation results in the inability to

connect to a 1x mode link partner.

No termination required.

Internal pull-down can be

used for logic 0. Pull up to

VDD_IO through 10K if

external pull-up is desired.

Pull down to VSS_IO

through a 10K resistor if an

external pull-down is

desired.

SP_TX_SWAP I, LVTTL,

PD Configures the order of 4x transmit lanes on serial

ports [0,6].

0 = A, B, C, D

1 = D, C, B, A

Must remain stable for 10 P_CLK cycles after

HARD_RST_b is de-asserted in order to be

sampled correctly.

This signal is ignored after reset.

Note: Ports that require the use of lane swapping for

ease of routing only function as 4x mode ports. The

re-configuration of a swapped port to dual 1x mode

operation results in the inability to connect to a 1x

mode link partner.

No termination required.

Internal pull-down can be

used for logic 0. Pull up to

VDD_IO through 10K if

external pull-up is desired.

Pull down to VSS_IO

through 10K resistor if an

external pull-down is

desired.

Clock and Reset

P_CLK I,

LVTTL This clock is used for the register bus clock.

The nominal frequency of this input clock is

100 MHz. For more information on programming

the P_CLK operating frequency, refer to “P_CLK

Programming” on page 75.

No termination required.

Table 3: Signal Descriptions and Recommended Termination

Pin Name Type Description Recommended

Terminationa

19

Tsi572 Hardware Manual

May 18, 2012

Integrated Device Technology

www.idt.com

S_CLK_p I,

CML Differential non-inverting reference clock. The

clock is used for following purposes: SERDES

reference clock, serial port system clock, ISF

clock and test clock.

The maximum frequency of this input clock is

156.25 MHz.

The clock frequency is defined in “Reference

Clock, S_CLK_p/n” on page 35.

For more information on the S_CLK operating

frequency, refer to “Line Rate Support” on

page 71.

AC coupling capacitor of

0.1uF required.

S_CLK_n I,

CML Differential inverting reference clock. The clock is

used for following purposes: SerDes reference

clock, serial port system clock, ISF clock and test

clock.

The maximum frequency of this input clock is

156.25 MHz.

The clock frequency is defined in “Reference

Clock, S_CLK_p/n” on page 35.

For more information on the S_CLK operating

frequency, refer to “Line Rate Support” on

page 71.

AC coupling capacitor of

0.1uF required.

HARD_RST_b I

LVTTL,

Hyst,

PU

Schmidt-triggered hard reset. Asynchronous

active low reset for the entire device.

The Tsi572 does not contain a voltage detector to

generate internal reset.

Connect to a power-up

reset source.

Refer to “Reset

Requirements” on page 64

Interrupts

INT_b O, OD,

LVTTL,

2mA

Interrupt signal (open drain output) External pull-up required.

Pull up to VDD_IO through

a 10K resistor.

Table 3: Signal Descriptions and Recommended Termination

Pin Name Type Description Recommended

Terminationa

20

Tsi572 Hardware Manual

May 18, 2012 Integrated Device Technology

www.idt.com

SW_RST_b O, OD,

LVTTL,

2mA

Software reset (open drain output): This signal is

asserted when a RapidIO port receives a valid

reset request on a RapidIO link. If self-reset is not

selected, this pin remains asserted until the reset

request is cleared from the status registers. If

self-reset is selected, this pin remains asserted

until the self reset is complete. If the Tsi572 is

reset from the HARD_RST_b pin, this pin is

de-asserted and remains de-asserted after

HARD_RST_b is released.

For more information, refer to “Resets” in the

Tsi572 User’s Manual.

External pull-up required.

Pull up to VDD_IO through

a 10K resistor.

Multicast

MCES I/O,

LVTTL,

PD

Multicast Event Symbol pin.

As an input, an edge (rising or falling) will trigger a

Multicast Event Control Symbol will be sent to all

ports;

As an output, this pin will toggle its value every

time an Multicast Event Control Symbol is

received by any port which is enabled for

Multicast even control symbols.

Must remain stable for 10 P_CLK cycles before

and after a transition.

No termination required.

This pin must not be driven

by an external source until

all power supply rails are

stable.

I2C

I2C_SCLK I/O, OD,

LVTTL,

PU

8mA

I2C input/output clock, up to 100 kHz.

If an EEPROM is present on the I2C bus, this

clock signal must be connected to the clock input

of the serial EEPROM on the I2C bus. If an

EEPROM is not present, the recommended

terminations should be used.

No termination required.

Internal pull-up may be

used for logic 1.

Pull up to VDD_IO through

a minimum 470 ohms

resistor if higher edge rate

is required.

I2C_SD I/O, OD,

LVTTL,

PU

8mA

I2C input and output data bus (bidirectional open

drain) No termination required.

Internal pull-up may be

used for logic 1.

Pull up to VDD_IO through

a minimum 470 ohms

resistor if higher edge rate

required.

Table 3: Signal Descriptions and Recommended Termination

Pin Name Type Description Recommended

Terminationa

Table of contents

Other IDT Switch manuals