Infineon BGT24LTR11 User manual

Other manuals for BGT24LTR11

1

Table of contents

Other Infineon Motherboard manuals

Infineon

Infineon TriBoard TC2X3 User manual

Infineon

Infineon Cypress MB2146-270 User manual

Infineon

Infineon TLD5099EP User manual

Infineon

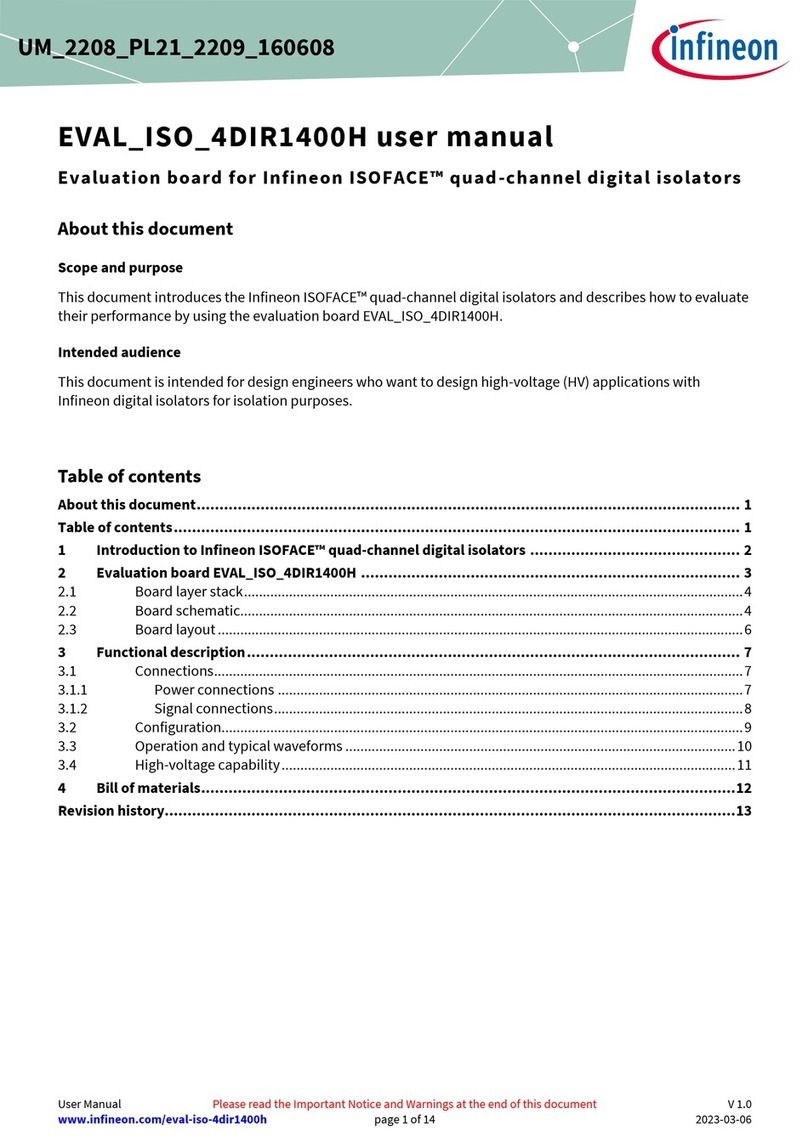

Infineon EVAL ISO 4DIR1400H User manual

Infineon

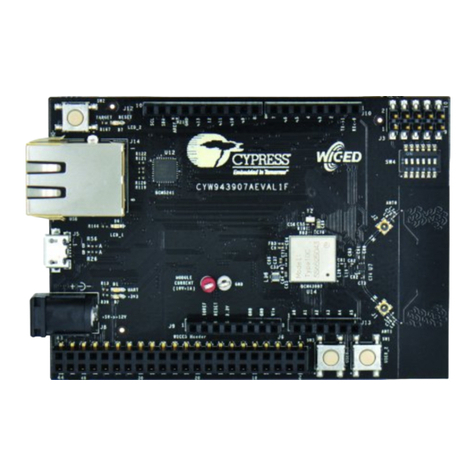

Infineon CYW943907AEVAL1F User manual

Infineon

Infineon OPTIGA Trust E Security Shield2Go User manual

Infineon

Infineon CY3290-CYAT817X User manual

Infineon

Infineon EZ-USB FX3 USB3 Vision solution demo kit User manual

Infineon

Infineon LITIX Power TLD5190-1QV User manual

Infineon

Infineon EiceDRIVER 1EDI302 AS Series User manual

Infineon

Infineon CYW920829M2EVK-02 User manual

Infineon

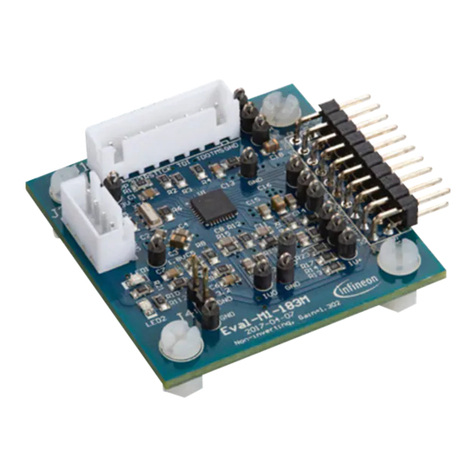

Infineon iMOTION EVAL-M1-183M User manual

Infineon

Infineon TLE8082ES User manual

Infineon

Infineon XMC 2Go User manual

Infineon

Infineon XMC7200 User manual

Infineon

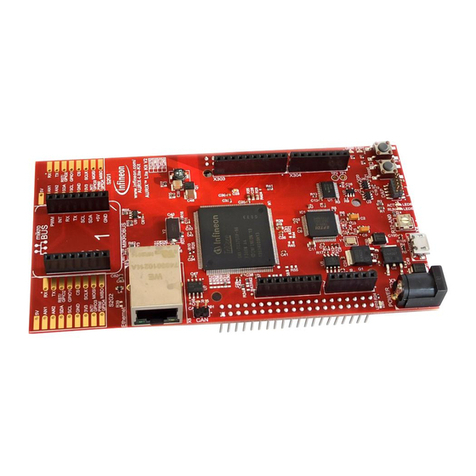

Infineon TriBoard TC3 6 Series User manual

Infineon

Infineon AURIX lite Kit V2 User manual

Infineon

Infineon TriBoard TC3X7 Series User manual

Infineon

Infineon XENSIV DEMO SENSE2GOL User manual

Infineon

Infineon XMC4300 Relax EtherCAT Kit-V1.1 User manual

Popular Motherboard manuals by other brands

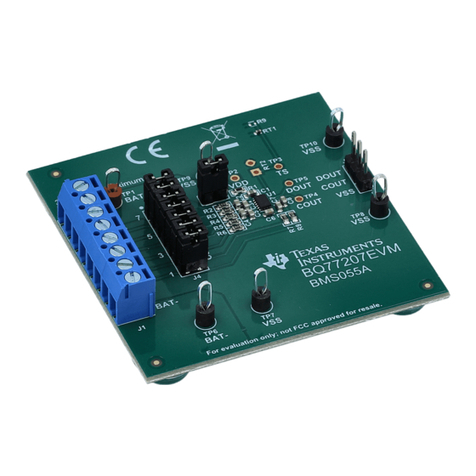

Texas Instruments

Texas Instruments TM4C Series user guide

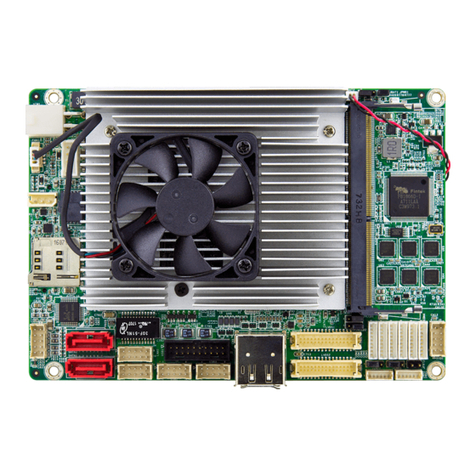

Arbor Technology

Arbor Technology EmCORE-i89M2 user manual

Texas Instruments

Texas Instruments CC112 Series quick start guide

Freescale Semiconductor

Freescale Semiconductor Freedom FRDM-KW24D512 user guide

Asus

Asus P4SE U2 user guide

DFI

DFI CMS101 user manual

Supermicro

Supermicro Supero X7DVL-E user manual

SMART

SMART RTM-ATCA-7360 quick start guide

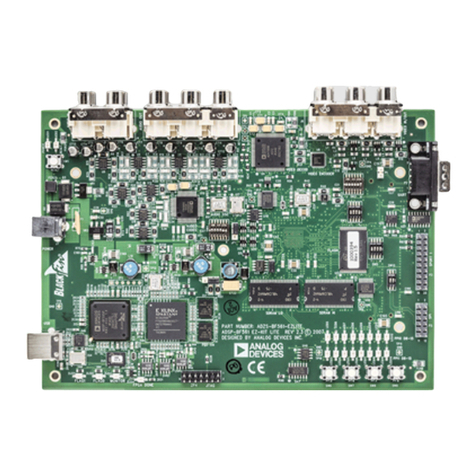

Analog Devices

Analog Devices ADSP-BF561 EZ-KIT Lite System manual

Fujitsu Siemens Computers

Fujitsu Siemens Computers D1691 Technical manual

Asus

Asus MAXIMUS IX EXTREME manual

Azoteq

Azoteq IQ Switch ProxFusion Series user guide