LTC4110

6

4110fb

Note 1: Stresses beyond those listed under Absolute Maximum Ratings

may cause permanent damage to the device. Exposure to any Absolute

Maximum Rating condition for extended periods may affect device

reliability and lifetime. Specific functionality or parametric performance

of the device beyond the limits expressly given in the Electrical

Characteristics table is not implied by these maximum ratings.

Note 2: The LTC4110E is guaranteed to meet performance specifications

from 0°C to 85°C. Specifications over the –40°C to 85°C operating

temperature range are assured by design, characterization and correlation

with statistical process controls.

Note 3: This IC includes overtemperature protection that is intended

to protect the device during momentary overload conditions.

Overtemperature protection will become active at a junction temperature

greater than the maximum operating junction temperature. Continuous

operation above the specified maximum operation temperature may result

in device degradation or failure. Operating junction temperature TJ(in

°C) is calculated from the ambient temperature TAand the average power

dissipation PD(in watts) by the formula TJ= TA+ θJA • PD.

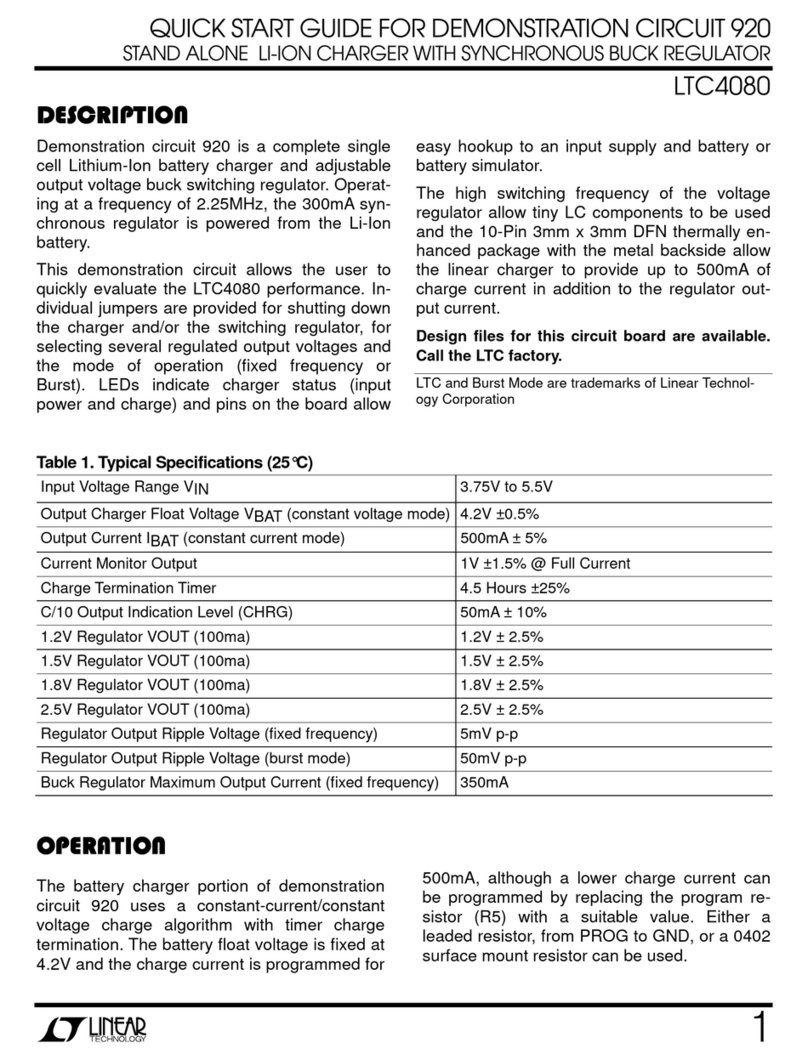

ELECTRICAL CHARACTERISTICS

The ldenotes the specifications which apply over the full operating

temperature range, otherwise specifications are at TA= 25°C. Unless otherwise specified, VDCIN = VDCOUT = VDCDIV = 12V, VBAT = 8.4V,

GND = SGND = CLP = CLN = SHDN = 0V and RVREF = 49.9k. All currents into device pins are positive and all currents out of device pins

are negative. All voltages are referenced to GND, unless otherwise specified.

Note 4: The LTC4110 is idle with no application load. It is not charging

or calibrating the battery and is not in backup or shutdown mode. The

internal clock is running and the SMBus is functional.

Note 5: Combined current of CSP, CSN and BAT pins set to VBAT with no

application load.

Note 6: CTH is defined as the sum of capacitance on THA, THB

SafetySignal.

Note 7: Does not include tolerance of current sense or current

programming resistors.

Note 8: Given as a per cell voltage referred to the BAT pin (VBAT/number of

series cells).

Note 9: Refer to System Management Bus Specification, Revision 1.1,

section 2.1 for Timing Diagrams and section 8.1, for tLOW and tTIMEOUT

requirements.

Note 10: Specifications over the –5°C to 85°C operating ambient

temperature range are assured by design, characterization and correlation

with statistical process controls.

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

VREMH THB Pin Battery Removal Threshold

Hysteresis Voltage

VTHB Decreasing; Lead Acid Only 25 mV

Logic and Status Output Levels

VILS SCL/SDA Input Pins Low Voltage l0.8 V

VIHS SCL/SDA Input Pins High Voltage l2.1 V

VOLS SDA Output Pin Low Voltage IPULL-UP = 350µA l0.4 V

VOLG ACPb, GPIO1,2,3 Output Pins Low Voltage IACPb, IGPIO1, IGPIO2, IGPIO3 = 10mA 1 V

IOHG ACPb, GPIO1,2,3 Output Pins Open

Leakage Current Outputs Open, VACPb, VGPIO1,2,3 = 5V –2 2 µA

VILG GPIO Input Low Voltage l1V

VIHG GPIO Input High Voltage l1.5 V

VILSD SHDN Input Pin Low Voltage 0.5 V

VIHSD SHDN Input Pin High Voltage 2.4 V

IISD SHDN Input Pin Pull-Up Current VSHDN = 2.4V –3.5 –2 –1 µA

TLR Logic Reset Duration After Power-Up

From Zero

VDCIN Transition From 0V to 5V in <1ms;

VBAT = 0

1s

SMBus Timing (Note 9)

tHIGH SCL Serial Clock High Period IPULL-UP = 350µA, CLOAD = 250pF,

RPU = 9.31k

l4µs

tLOW SCL Serial Clock Low Period IPULL-UP = 350µA, CLOAD = 250pF,

RPU = 9.31k

l4.7 µs

tTO Timeout Period l25 ms

tFSDA/SCL Fall Time CLOAD = 250pF, RPU = 9.31k l300 ns

tSU-STA Start Condition Set-Up Time l4.7 µs

tHD-STA Start Condition Hold Time l4µs

tHD-DAT SDA to SCL Falling-Edge Hold Time,

Slave Clocking in Data

l300 ns