KSZ8851SNL-Eval Evaluation Board User’s Guide Rev. 1.1

Micrel, Inc. April 21, 2010

5/11

1.0 Introduction

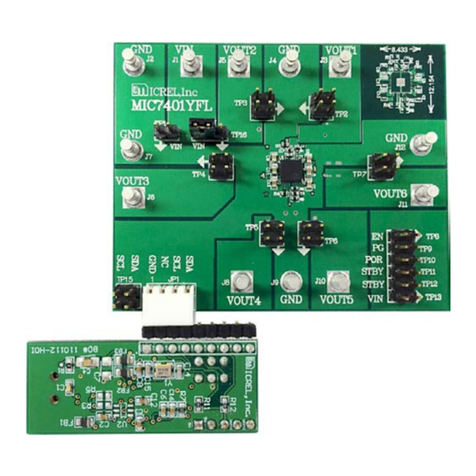

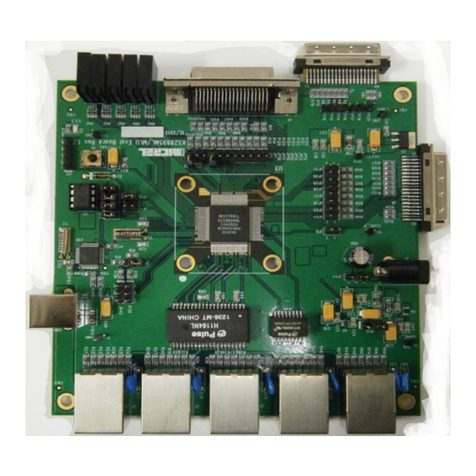

The KSZ8851SNL-Eval Evaluation Board is intended to provide a convenient and fast way to

evaluate or demonstrate the functionality and performance of this new Single-Port Ethernet

Controller KSZ8851SNL device from Micrel.

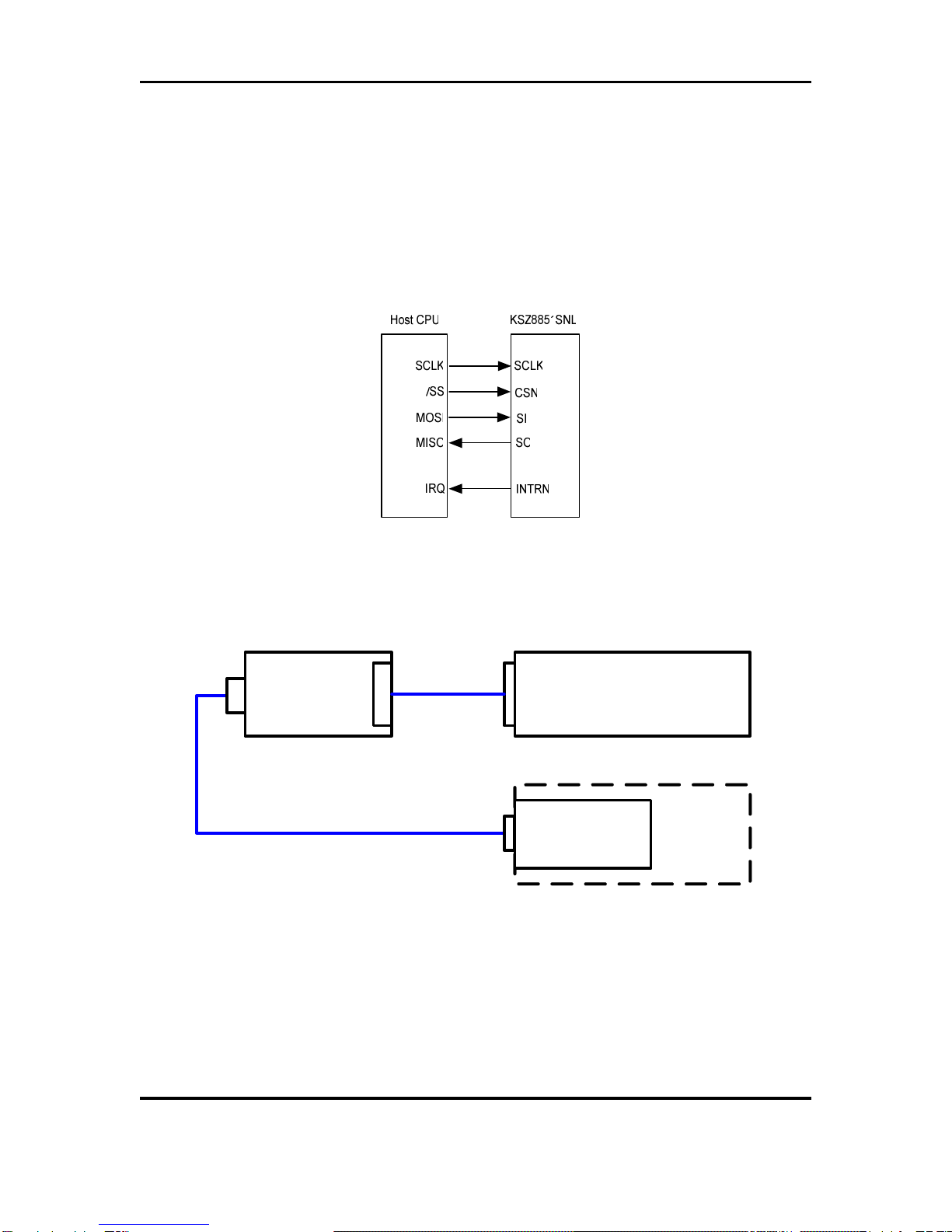

The KSZ8851SNL comes with a 32-pin, lead-free QFN (5mm x 5mm) package and provides an

ideal solution for applications requiring Serial Peripheral Interface (SPI) between single-port

Ethernet Controller and Host microcontroller.

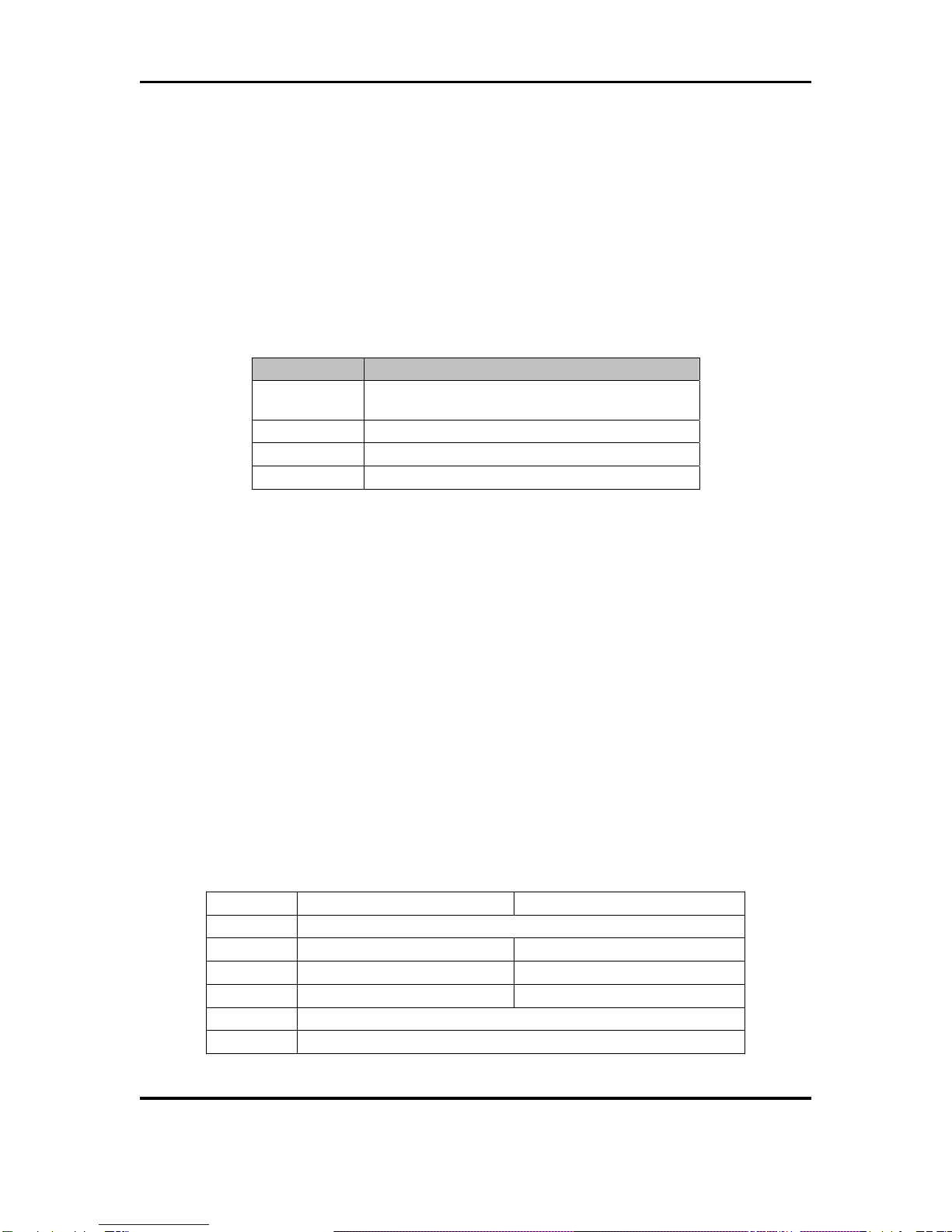

This evaluation board is designed as a stand alone without microcontroller on board. By default

the KSZ8851SNL-Eval board comes with an operation of no EEPROM for KSZ8851SNL device.

Customer can directly wire the board for SPI interface. The purpose is to provide a simple tool

that can be used to evaluate the KSZ8851SNL device by connecting via headers to customer

provided Microcontroller or Non-PCI hardware platform.

Micrel provides a basic software driver based on SPI Interface solution and different operating

system platforms to evaluate the KSZ8851SNL functionality and performance. The software

includes a configuration utility to allow quick and easy device setup, initialization and

transmit/receive packet. All KSZ8851SNL configuration pins, control signals and SPI interface are

accessible either by jumpers, test points or headers.

2.0 Board Features

•One KSZ8851SNL 32-pin Single-Port Ethernet Controller with SPI for host interface

•Single +5V/GND power input from headers

•RJ-45 Jack for Fast Ethernet cable interface

•HP Auto-MDIX for automatic detection and correction for straight-through and crossover

cables

•Two on board LDO voltage regulators, one for VDD_IO and the other for 3.3VA

•One AT93C46 for external EEPROM interface

•Two LED indicators for port status and activity

•One LED indicator for 3.3V output ready

•One LED indicator for Power Management Event (PME) output status

•Jumpers to configure strapping pin and VDD_IO voltage option

•Headers to wire the SPI interface from external hardware platform

•Manual reset button for quick reboot device after re-configuration of strapping pin

3.0 Evaluation Kit Contents

The KSZ8851SNL Evaluation Kit includes the following hardware:

•KSZ8851SNL Evaluation Board

The KSZ8851SNL Data Sheet and Hardware Design Package with the following collaterals that

can be downloaded from Micrel’s website at http://www.micrel.com

•KSZ8851SNL Eval Board Schematic (PDF and OrCAD DSN file)

•KSZ8851SNL Eval Board Gerber File (PDF version included)

•KSZ8851SNL Eval Board User’s Guide (this document and included BOM)

•KSZ8851SNL IBIS Model