iCE40 UltraPlus 8:1 Mic Aggregation Demo

User Guide

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

2 FPGA-UG-02035-1.2

Contents

1. Introduction ..................................................................................................................................................................3

1.1. Demo Design Overview .......................................................................................................................................3

2. Functional Description ..................................................................................................................................................4

3. Demo Package ..............................................................................................................................................................5

4. iCE40 UltraPlus MDP and Resources ............................................................................................................................6

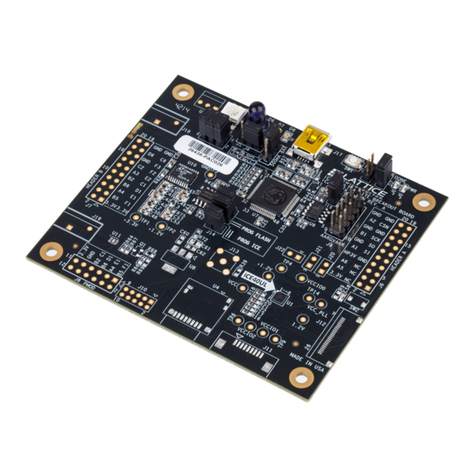

4.1. Configuring the iCE40 UltraPlus MDP .................................................................................................................7

5. Programming the Bitstreams to the iCE40 UltraPlus MDP ...........................................................................................8

6. Running the Demo ......................................................................................................................................................10

6.1. Using Headphones ............................................................................................................................................10

6.2. Oscilloscope Connection Points ........................................................................................................................11

6.3. I2S Aggregation Signal Format ...........................................................................................................................12

6.4. Measured Oscilloscope I2S Aggregation Signals ................................................................................................13

Appendix A. Schematic Diagram.........................................................................................................................................14

Appendix B. Bill of Materials...............................................................................................................................................15

Technical Support Assistance .............................................................................................................................................16

Revision History ..................................................................................................................................................................16

Figures

Figure 1.1. 8:1 Mic Aggregation Demo Overview .................................................................................................................3

Figure 2.1. 8:1 Mic Aggregation Demo Block Diagram .........................................................................................................4

Figure 3.1. Directory Structure .............................................................................................................................................5

Figure 4.1. iCE40 UltraPlus MDP Configuration ....................................................................................................................6

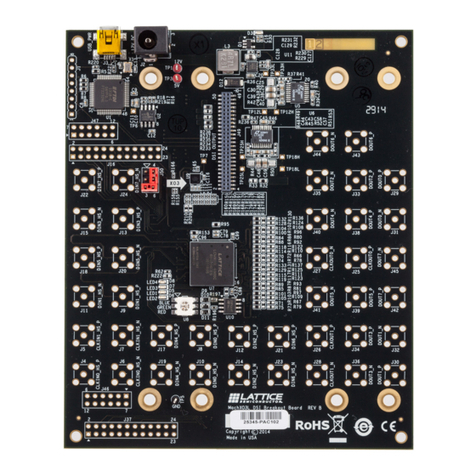

Figure 4.2. iCE40 UltraPlus MDP and 8 to 1 Mic Aggregator Board......................................................................................7

Figure 5.1. Device Properties................................................................................................................................................8

Figure 5.2. Program Device Button.......................................................................................................................................9

Figure 6.1. Mode Push Button Control Sequences Selected Microphone..........................................................................10

Figure 6.2. 8 to 1 Mic Aggregator Board (Daughter Board) ................................................................................................10

Figure 6.3. J30 Section on MDP Board................................................................................................................................11

Figure 6.4. Header to Connect to the Oscilloscope ............................................................................................................11

Figure 6.5. Aggregation TDM Format for 8 Channels .........................................................................................................12

Figure 6.6. I2S Aggregation for Channel 1 ...........................................................................................................................12

Figure 6.7. I2S Aggregation for Channel 8 ...........................................................................................................................12

Figure 6.8. Measured I2S Aggregation Signals for 8 Channels ............................................................................................13

Figure 6.9. Measured I2S Aggregation Signals for Channel 1 ..............................................................................................13

Downloaded from Arrow.com.Downloaded from Arrow.com.