Quick Start Guide: LPC1768-Xplorer

8www.ngxtechnologies.com

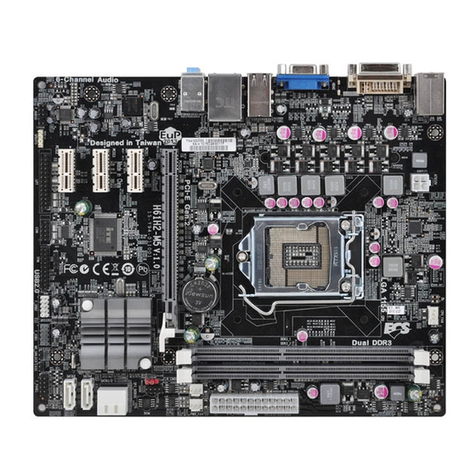

Up to 512 kB on-chip flash program memory with In-System Programming (ISP) and

In-Application Programming (IAP) capabilities.

Up to 64 kB on-chip SRAM includes

–Up to 32 kB of SRAM on the CPU with local code/data bus for high-performance CPU access.

–Up to two 16 kB SRAM blocks with separate access paths for higher throughput. Two 32 kB

SRAM blocks with separate bus access.

Eight channel General Purpose DMA controller (GPDMA).

Ethernet MAC with RMII interface and dedicated DMA controller.

USB 2.0 full-speed controller that can be configured for either device, Host, or OTG operation

with an on-chip PHY for device and Host functions and a dedicated DMA controller.

Four UARTs with fractional baud rate generation, internal FIFO, IrDA, and DMA support. One

UART has modem control I/O and RS-485/EIA-485 support.

Two-channel CAN controller.

Two SSP controllers with FIFO and multi-protocol capabilities. The SSP interfaces can be used

with the GPDMA controller.

SPI controller with synchronous, serial, full duplex communication and programmable data

length.

Three enhanced I2C-bus interfaces, one with an open-drain output supporting the full I2C

specification and Fast mode plus with data rates of 1Mbit/s, two with standard port pins.

Enhancements include multiple address recognition and monitor mode.

I2S (Inter-IC Sound) interface for digital audio input or output, with fractional rate control.

12-bit Analog-to-Digital Converter (ADC) with input multiplexing among eight pins, conversion

rates up to 200 kHz, and multiple result registers.

10-bit Digital-to-Analog Converter (DAC) with dedicated conversion timer and DMA support.

70 (100 pin package) General Purpose I/O (GPIO) pins with configurable pull-up/down resistors,

open drain mode, and repeater mode.

Real-Time Clock (RTC) with a separate power domain.

Watchdog Timer (WDT). The WDT can be clocked from the internal RC oscillator, the RTC

oscillator, or the APB clock.

Cortex-M3 system tick timer, including an external clock input option.

Repetitive interrupt timer provides programmable and repeating timed interrupts.

The Wakeup Interrupt Controller (WIC) allows the CPU to automatically wake up from

any priority interrupt that can occur while the clocks are stopped in deep sleep,

Power-down, and Deep power-down modes.

Four reduced power modes: Sleep, Deep-sleep, Power-down, and Deep power-down.

Single 3.3 V power supply (2.4 V to 3.6 V). Temperature range of -40 °C to 85 °C.

Four external interrupt inputs configurable as edge/level sensitive. All pins on PORT0 and

PORT2 can be used as edge sensitive interrupt sources.

On-chip Power-On Reset (POR).

On-chip crystal oscillator with an operating range of 1 MHz to 25 MHz.

4 MHz internal RC oscillator trimmed to 1% accuracy that can optionally be used as a system

clock.

An on-chip PLL allows CPU operation up to the maximum CPU rate without the need for a

high-frequency crystal.

A second, dedicated PLL may be used for the USB interface in order to allow added flexibility

for the Main PLL settings.

Versatile pin function selection feature allows many possibilities for using on-chip peripheral

functions.

Available as 100-pin LQFP (14 x 14 x 1.4 mm) and 80-pin LQFP (12 x 12 x 1.4 mm) packages.

For the most updated information on the MCU please refer to NXP's website.