PGA26E07BA-SWEVB008 Ver. 1.2

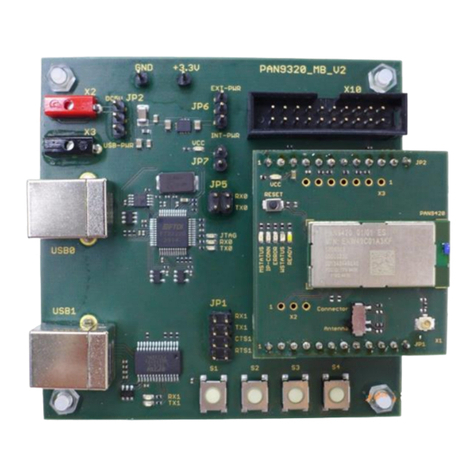

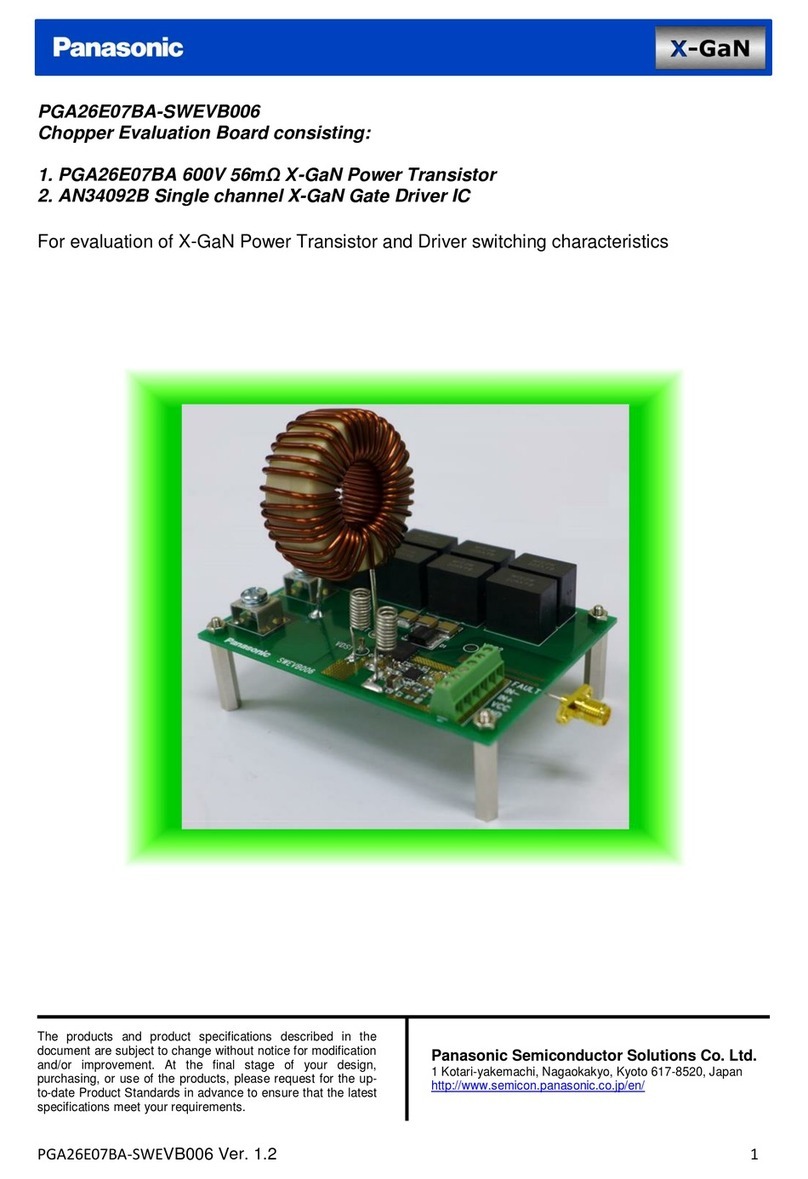

PGA26E07BA-SWEVB008

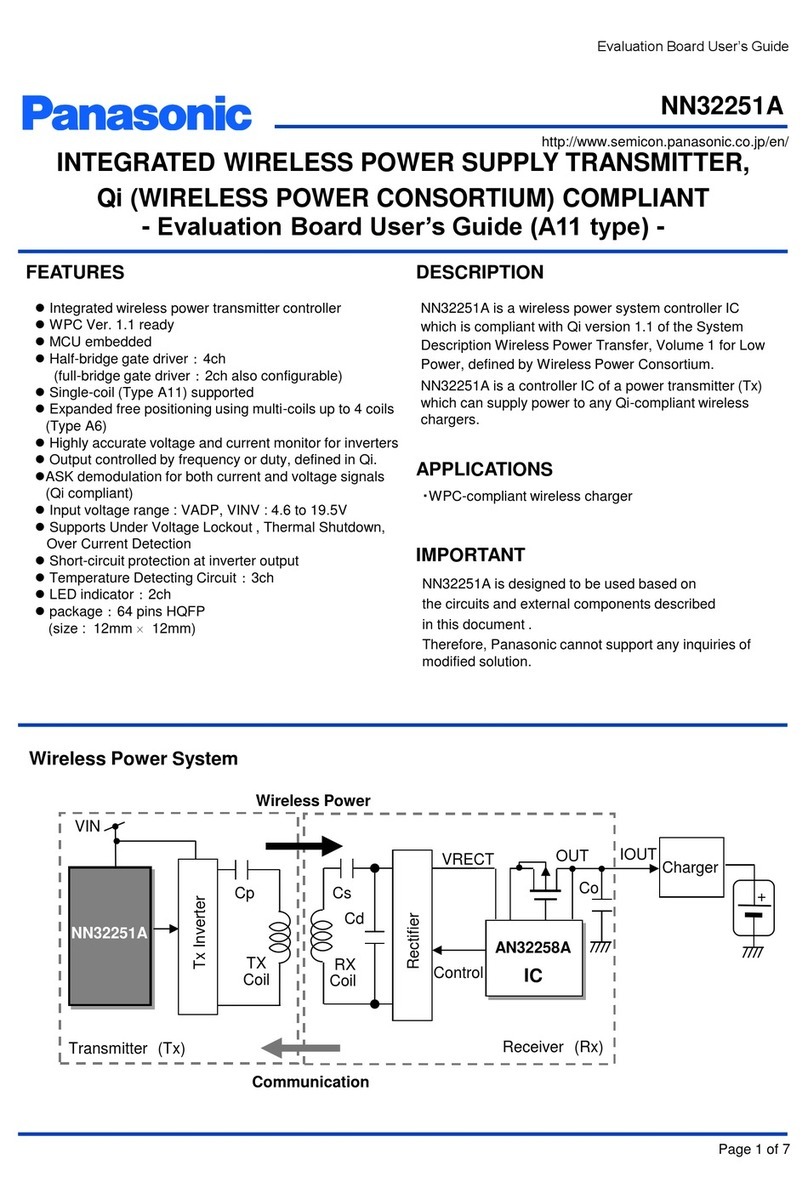

Half Bridge Evaluation Board consisting:

1. PGA26E07BA 600V 70mΩX-GaN Power Transistor

2. AN34092B Single channel X-GaN Gate Driver IC

3. General Purpose Half Bridge Isolator

The products and product specifications described in the

document are subject to change without notice for modification

and/or improvement. At the final stage of your design,

purchasing, or use of the products, please request for the up-to-

date Product Standards in advance to ensure that the latest

specifications meet your requirements.

Panasonic Semiconductor Solutions Co. Ltd.

1 Kotari-yakemachi, Nagaokakyo, Kyoto 617-8520, Japan

http://www.semicon.panasonic.co.jp/en/

The products and product specifications described in

the document are subject to change without notice for modification

and/or improvement. At the final stage of your design, purchasing,

or use of the products, therefore, ask for the most up-to-date

Product Standards in advance to make sure that the latest

specifications satisfy your requirements.

As of March, 2017

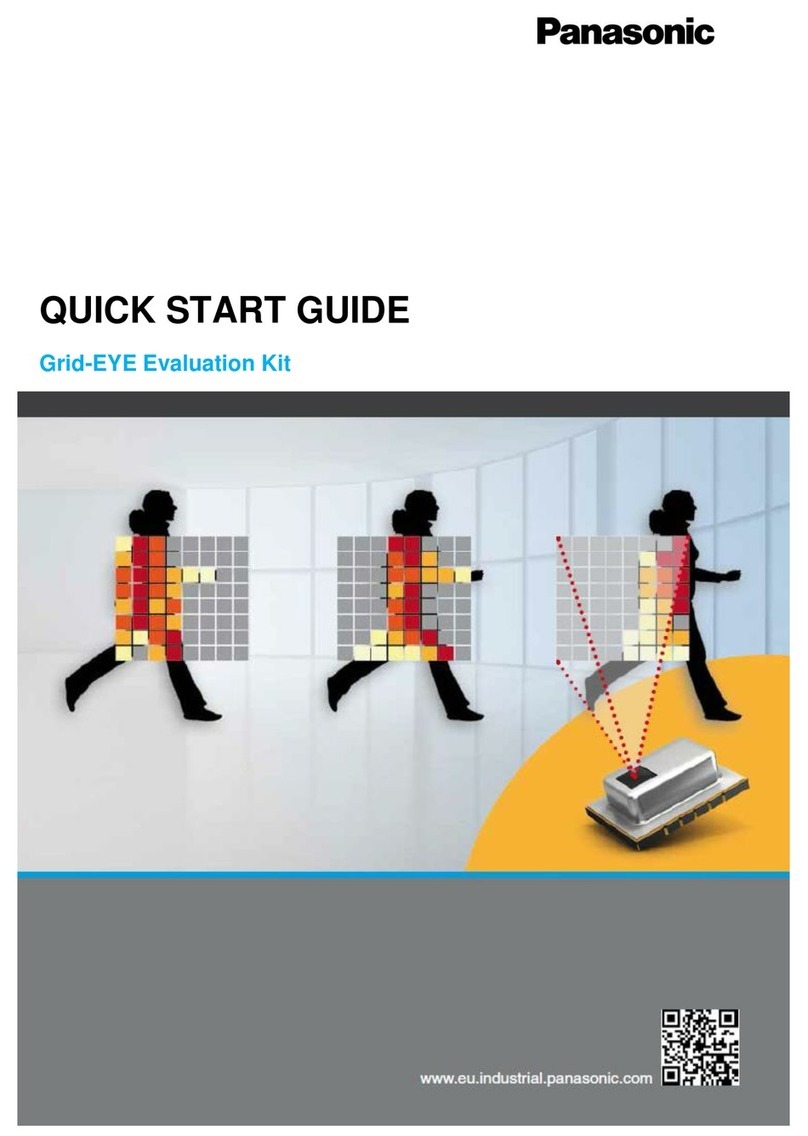

Panasonic Industrial Devices

Sales Company of America

Two Riverfront Plaza, 7th Floor

Newark, NJ, 07102, United States

800-344-2112

na.industrial.panasonic.com

Panasonic

Semiconductor Solutions Co., Ltd.

1 Kotari-yakemachi, Nagaokakyo,

Kyoto 617-8520, Japan

Tel. +81-75-951-8151

http://www.semicon.panasonic.co.jp/en