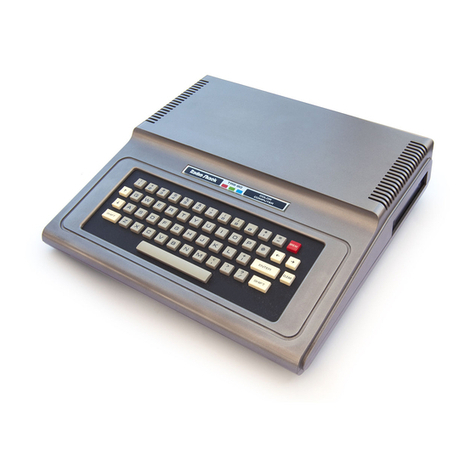

Radio Shack 26-1061 User manual

Other Radio Shack Desktop manuals

Radio Shack

Radio Shack 4 User manual

Radio Shack

Radio Shack TRS-80 User manual

Radio Shack

Radio Shack 32K InvestoGraph User manual

Radio Shack

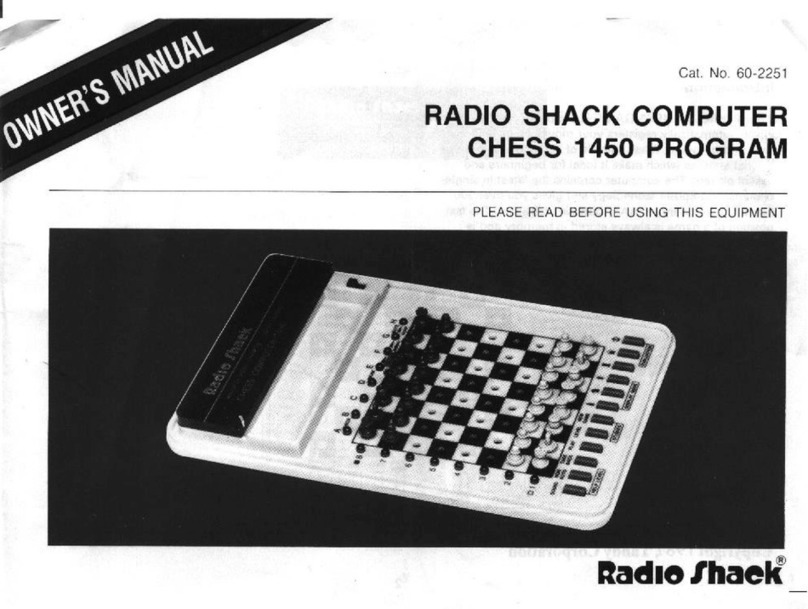

Radio Shack CHESS COMPUTER 1450 User manual

Radio Shack

Radio Shack TRS-80 User manual

Radio Shack

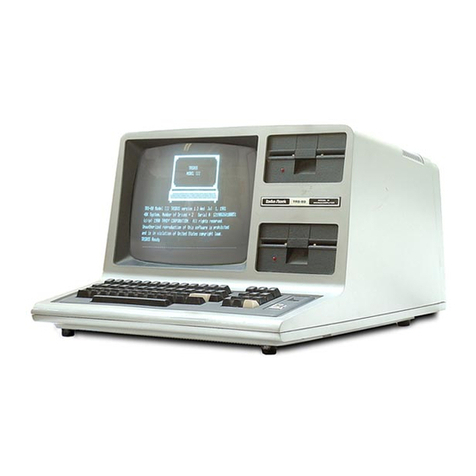

Radio Shack TRS-80 Model 4 Product manual

Radio Shack

Radio Shack TRS-80 Model 4 User manual

Radio Shack

Radio Shack TRS-80 III User manual

Radio Shack

Radio Shack TRS-80 Model 12 User manual

Radio Shack

Radio Shack TRS-80 Model-4 User manual

Radio Shack

Radio Shack TRS-80 Model 16B User manual

Radio Shack

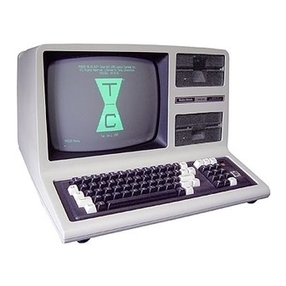

Radio Shack TRS-80 DT-1 User manual

Radio Shack

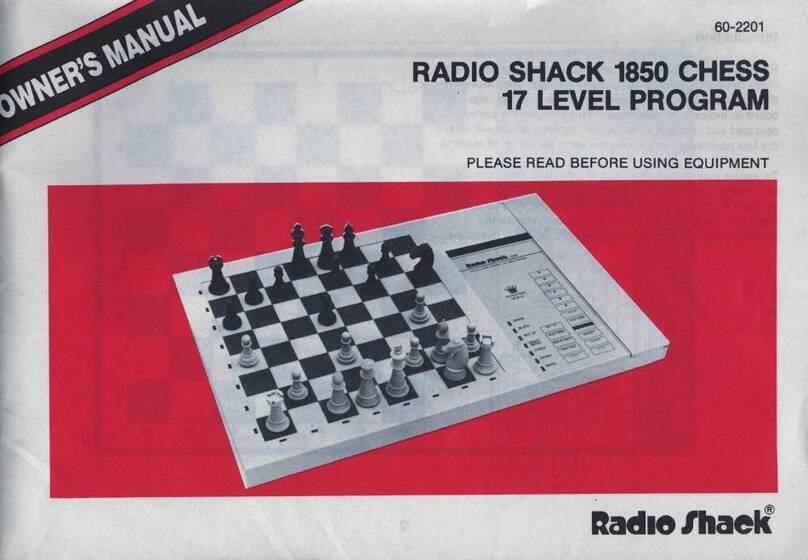

Radio Shack 1850 User manual

Radio Shack

Radio Shack TRS-80 III User manual

Radio Shack

Radio Shack TRS-80 Model 16 User manual

Radio Shack

Radio Shack Tandy 1000 User manual

Radio Shack

Radio Shack 16B User guide

Radio Shack

Radio Shack TRS-80 User manual

Radio Shack

Radio Shack TRS-80 User manual

Radio Shack

Radio Shack TRS-80 User manual