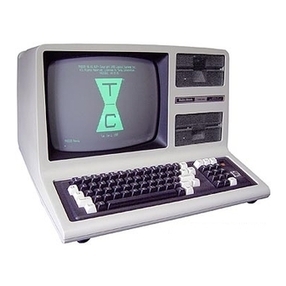

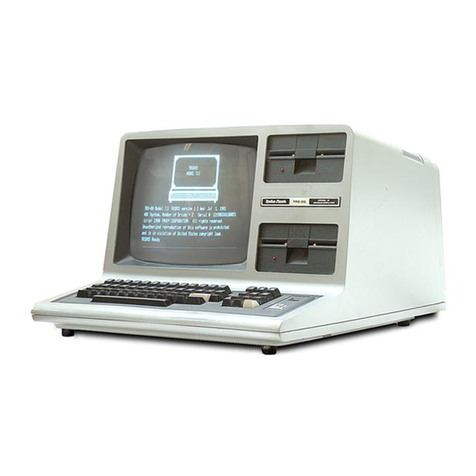

SYSTEM DESCRIPTION

The primary functions of the Color Computer are performed

by five 40-pin Large Scale Integration (LSI) chips plus

Random Access Memory (RAM) and Read Only Memory

(ROM). These five chips are indicated on the Block Diagram

(Figure 1) by CPU, SAM, VDG, and two PIA's. With only

these five chips plus RAM, ROM, and apower supply, the

Color Computer would operate and provide acomposite video

output. However, to allow communication with the outside

world, I/O interfaces must be added.

The main component of any computer system is the Central

Processor Unit (CPU). It is the duty of the CPU to provide or

request data and select the proper address for this data. In

addition, the CPU is capable of performing alimited set of

mathematical and logical operations on the data.

ROM has the duty of providing the CPU with apredefined set

of instructions. Without ROM, the CPU would run wild and

randomly execute instructions. In normal operation, the CPU

jumps to the start address in ROM after the reset switch has

been pressed, and then performs the reset program to set up

all of the programmable devices. Following this, the BASIC

instruction set residing in ROM is in control of the CPU.

RAM provides storage for the programs and/or data currently

being executed. In addition, this same RAM is used to generate

the video display. Normally, no conflict will be observed

because the program will use one portion of RAM and the

display will use another. During normal usage, the BASIC

interpreter located in ROM will control the execution of

programs located in RAM.

Acentral component in the Color Computer is the dynamic

RAM controller chip (SAM). This chip provides refresh and

address multiplexing for the RAM. It also provides all of the

system timing and device selection.

The video display generator (VDG) provides virtually the

entire video interface on one chip, and allows several different

alphanumeric and graphic modes. This mode of operation of

the VDG is controlled by one of two peripheral interface

adapters (PIA's) used in the Color Computer. With this

information and RAM data, the VDG generates composite

video and color information for the modulator circuitry.

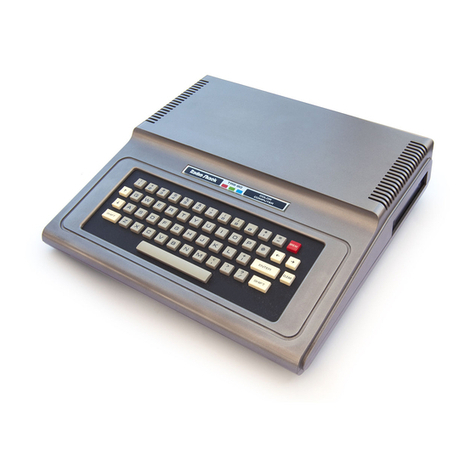

The remaining circuitry in the Color Computer is devoted to

Input/Output (I/O) communication. The most important part

of this circuitry is the keyboard which allows the operator to

enter information. Other I/O circuits are provided to allow

joystick inputs, cassette input and output, and RS232 input

and output.