Silicon Laboratories Si4430 User manual

Preliminary Rev. 0.4 5/09 Copyright © 2009 by Silicon Laboratories Si4430

This information applies to a product under development. Its characteristics and specifications are subject to change without notice.

Si4430

Si4430 ISM TRANSCEIVER

Features

Applications

Description

Silicon Laboratories’ Si4430 highly integrated, single chip wireless ISM

transceiver is part of the EZRadioPRO™ family. The EZRadioPRO family includes

a complete line of transmitters, receivers, and transceivers allowing the RF

system designer to choose the optimal wireless part for their application.

The Si4430 offers advanced radio features including continuous frequency

coverage from 900–960 MHz The Si4430’s high level of integration offers reduced

BOM cost while simplifying the overall system design. The extremely low receive

sensitivity (–118 dBm) coupled with industry leading +20 dBm output power

ensures extended range and improved link performance. Built-in antenna diversity

and support for frequency hopping can be used to further extend range and

enhance performance.

Additional system features such as an automatic wake-up timer, low battery

detector, 64 byte TX/RX FIFOs, automatic packet handling, and preamble

detection reduce overall current consumption and allow the use of lower-cost

system MCUs. An integrated temperature sensor, general purpose ADC, power-

on-reset (POR), and GPIOs further reduce overall system cost and size.

The Si4430’s digital receive architecture features a high-performance ADC and

DSP based modem which performs demodulation, filtering, and packet handling

for increased flexibility and performance. This digital architecture simplifies

system design while allowing for the use of lower-end MCUs. The direct digital

transmit modulation and automatic PA power ramping ensure precise transmit

modulation and reduced spectral spreading ensuring compliance with ARIB

regulations.

Frequency Range = 900–960 MHz

Sensitivity = –118 dBm

+13 dBm Max Output Power

Configurable –8 to +13 dBm

Low Power Consumption

18.5 mA receive

28 mA @ +13 dBm transmit

Data Rate = 1 to 128 kbps

Power Supply = 1.8 to 3.6 V

Ultra low power shutdown mode

Digital RSSI

Wake-on-radio

Auto-frequency calibration (AFC)

Antenna diversity and TR switch

control

Configurable packet structure

Preamble detector

TX and RX 64 byte FIFOs

Low battery detector

Temperature sensor and 8-bit ADC

–40 to +85 °C temperature range

Integrated voltage regulators

Frequency hopping capability

On-chip crystal tuning

20-Pin QFN package

FSK, GFSK, and OOK modulation

Low BOM

Power-on-reset (POR)

Remote control

Home security & alarm

Teleme tr y

Personal data logging

Toy control

Tire pressure monitoring

Wireless PC peripherals

Remote meter reading

Remote keyless entry

Home automation

Industrial control

Sensor networks

Health monitors

Tag readers

Patents pending

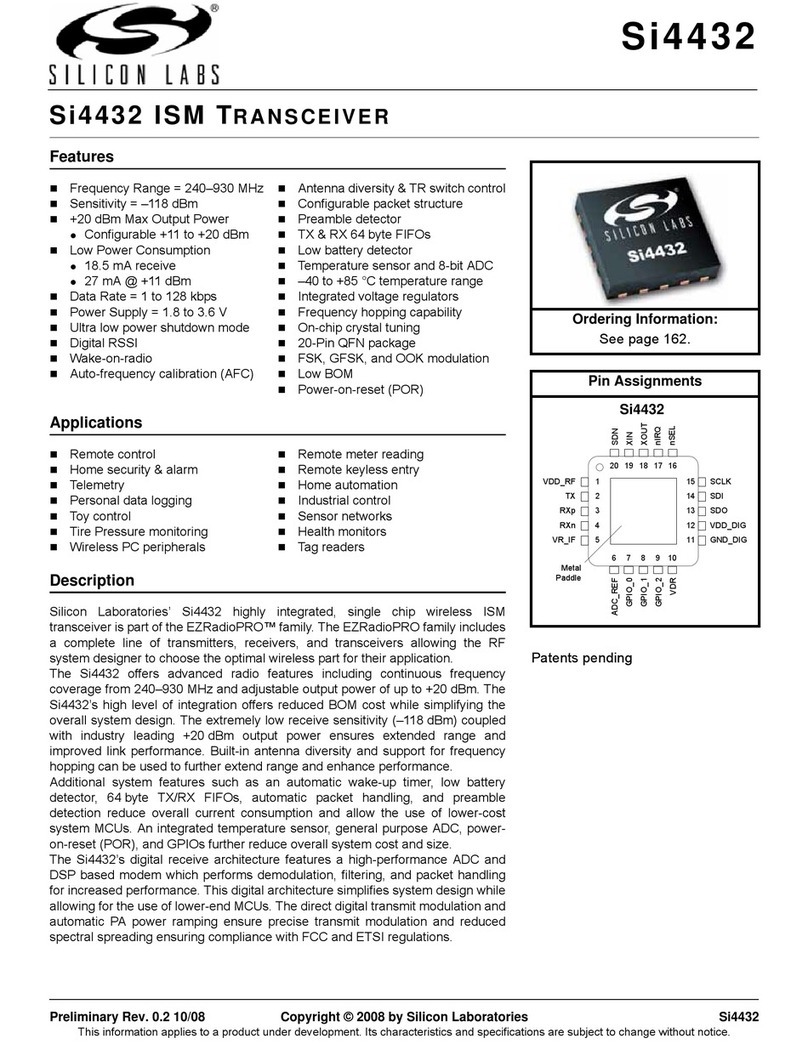

Ordering Information:

See page 150.

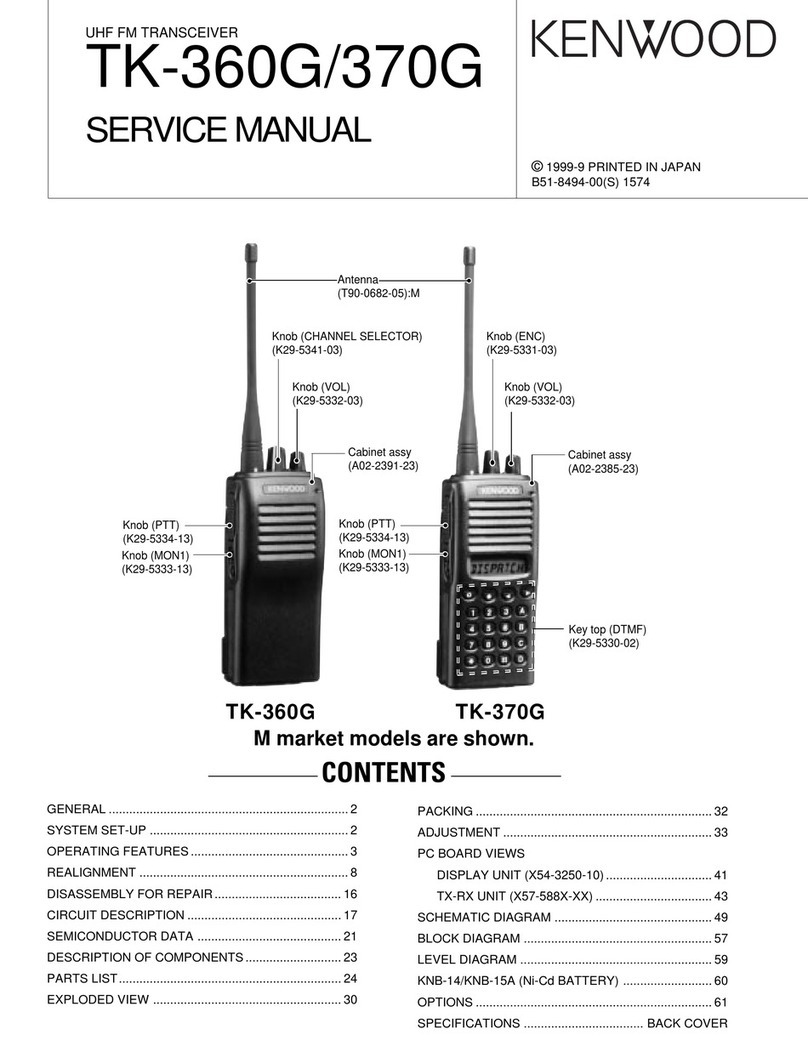

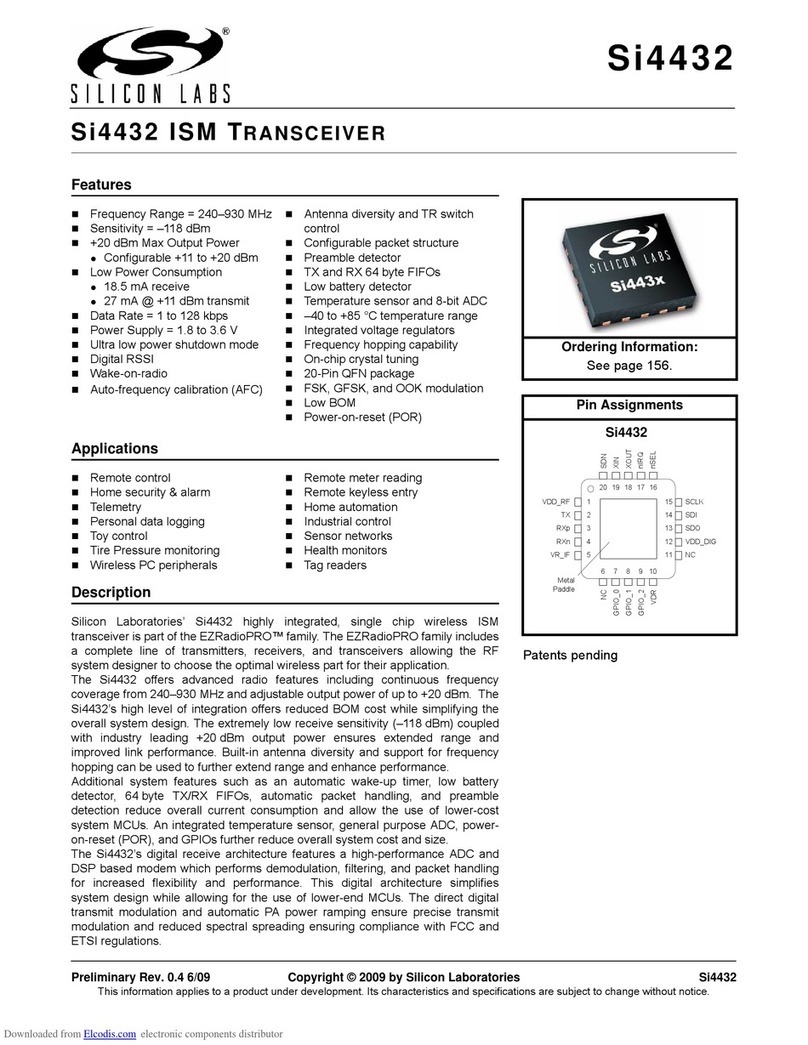

Pin Assignments

VDD_RF 1

2

3

4

15

14

13

12

6789

19 18 1720

TX

RXp

RXn

SCLK

SDI

SDO

VDD_DIG

NC

GPIO_0

GPIO_1

GPIO_2

XIN

XOUT

SDN

nIRQ

Metal

Paddle

511VR_IF NC

10

16

VDR nSEL

Si4430

Si4430

2 Preliminary Rev. 0.4

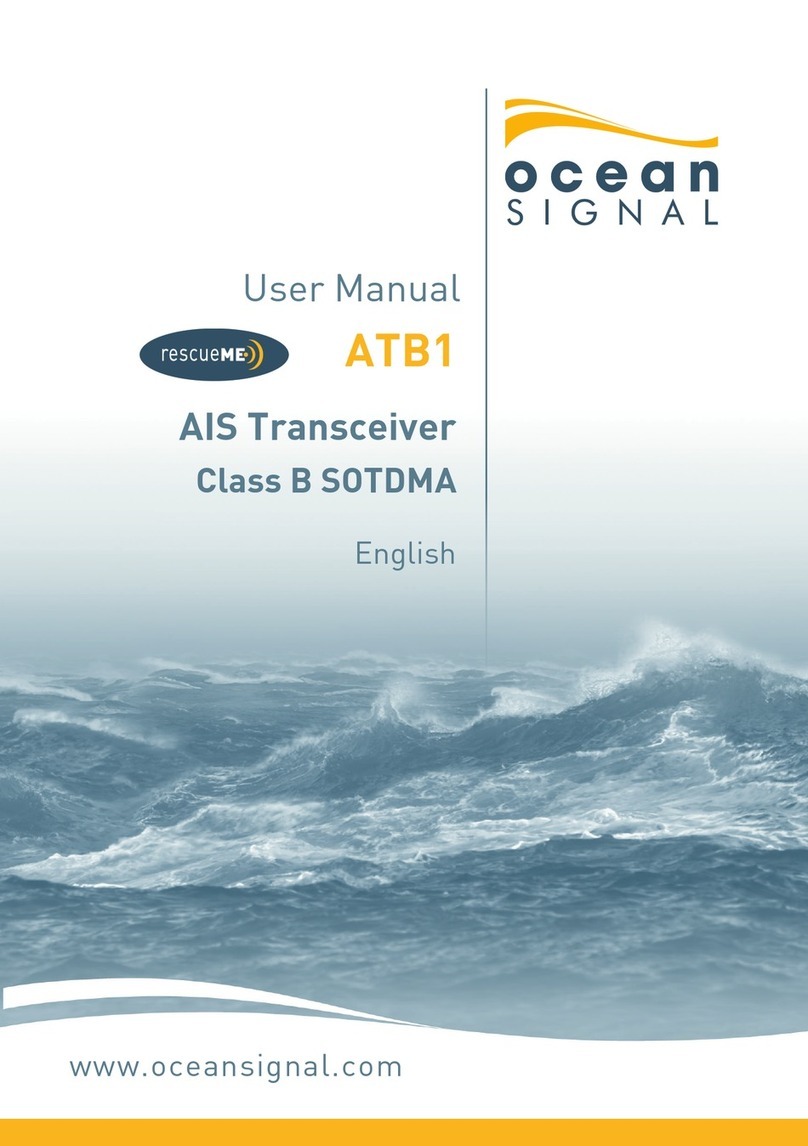

Functional Block Diagram

LPF CP

Delta Sigma

Modulator

N

LNA

Mixers PGA

AGC Control

PA

VCO

SPI, & Controller

Digital Logic

PFD

PWR_CTRL

TX

RFn

PA_RAMP

PWR_CTRL

PA_RAMP

GPIO_2

GPIO_1

TXMOD

Xout

Xin

Digital Modem

Digital LDO

RC 32K OSC

30M XTAL

OSC

RF LDO

IF LDO

VCO LDO PLL LDO

BIAS

SDN

TXRXSW

ANTDIV

Low Power

Digital LDO

POR

Temp

Sensor

VR_DIG

GPIO_0

nIRQ

SDO

SDI

SCLK

VDD_DIG

VR_IF

LBD

nSEL

VDD_RF

8Bit

ADC

RFp ADC

Si4430

Preliminary Rev. 0.4 3

TABLE OF CONTENTS

Section Page

1. Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

1.1. Definition of Test Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

2. Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

2.1. Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

3. Controller Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

3.1. Serial Peripheral Interface (SPI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

3.2. Operating Mode Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

3.3. Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

3.4. Device Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

3.5. System Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

3.6. Frequency Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

4. Modulation Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

4.1. Modulation Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

4.2. Modulation Data Source . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

4.3. FIFO Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

4.4. Direct Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

4.5. PN9 Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

4.6. Synchronous vs. Asynchronous . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

5. Internal Functional Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

5.1. RX LNA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

5.2. RX I-Q Mixer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

5.3. Programmable Gain Amplifier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

5.4. ADC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

5.5. Digital Modem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

5.6. Synthesizer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

5.7. Power Amplifier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

5.8. Crystal Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

5.9. Regulators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

6. Data Handling and Packet Handler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

6.1. RX and TX FIFOs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

6.2. Packet Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

6.3. Packet Handler TX Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

6.4. Packet Handler RX Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

6.5. Data Whitening, Manchester Encoding, and CRC . . . . . . . . . . . . . . . . . . . . . . . . . .45

6.6. Preamble Detector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

6.7. Preamble Length . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

6.8. Invalid Preamble Detector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

6.9. TX Retransmission and Auto TX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

7. RX Modem Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

Si4430

4 Preliminary Rev. 0.4

7.1. Modem Settings for FSK and GFSK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

7.2. Modem Settings for OOK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

8. Auxiliary Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

8.1. Smart Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

8.2. Microcontroller Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

8.3. General Purpose ADC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

8.4. Temperature Sensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

8.5. Low Battery Detector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

8.6. Wake-Up Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

8.7. Low Duty Cycle Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

8.8. GPIO Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

8.9. Antenna-Diversity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

8.10. RSSI and Clear Channel Assessment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

9. Reference Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

10. Measurement Results . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .69

11. Application Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

11.1. Crystal Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

11.2. Layout Practice . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

12. Reference Material . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

12.1. Complete Register Table and Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

13. Pin Descriptions: Si4430 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .149

14. Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .150

15. Package Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .151

Contact Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .152

Si4430

Preliminary Rev. 0.4 5

LIST OF FIGURES

Figure 1. Si4430 RX/TX Direct-Tie Application Example ..........................................................16

Figure 2. SPI Timing..................................................................................................................18

Figure 3. SPI Timing—READ Mode ..........................................................................................19

Figure 4. SPI Timing—Burst Write Mode ..................................................................................19

Figure 5. SPI Timing—Burst Read Mode ..................................................................................19

Figure 6. State Machine Diagram..............................................................................................20

Figure 7. TX Timing...................................................................................................................24

Figure 8. RX Timing ..................................................................................................................25

Figure 9. Frequency Deviation ..................................................................................................28

Figure 10. Sensitivity at 1% PER vs. Carrier Frequency Offset ................................................29

Figure 11. FSK vs GFSK Spectrums.........................................................................................32

Figure 12. Direct Synchronous Mode Example.........................................................................34

Figure 13. Direct Asynchronous Mode Example .......................................................................34

Figure 14. FIFO Mode Example ................................................................................................35

Figure 15. PLL Synthesizer Block Diagram...............................................................................37

Figure 16. FIFO Thresholds ......................................................................................................40

Figure 17. Packet Structure.......................................................................................................41

Figure 18. Multiple Packets in TX Packet Handler ....................................................................42

Figure 19. Required RX Packet Structure with Packet Handler Disabled .................................42

Figure 20. Multiple Packets in RX Packet Handler....................................................................42

Figure 21. Multiple Packets in RX with CRC or Header Error ...................................................43

Figure 22. Operation of Data Whitening, Manchester Encoding, and CRC ..............................45

Figure 23. POR Glitch Parameters............................................................................................53

Figure 24. General Purpose ADC Architecture .........................................................................55

Figure 25. ADC Differential Input Example—Bridge Sensor .....................................................56

Figure 26. ADC Differential Input Offset for Sensor Offset Coarse Compensation...................57

Figure 27. Temperature Ranges using ADC8 ...........................................................................59

Figure 28. WUT Interrupt and WUT Operation..........................................................................62

Figure 29. Low Duty Cycle Mode ..............................................................................................63

Figure 30. RSSI Value vs. Input Power.....................................................................................66

Figure 31. Split RF I/Os with Separated TX and RX Connectors—Schematic .........................67

Figure 32. Split RF I/Os with Separated TX and RX Connectors—Top ....................................69

Figure 33. Split RF I/Os with Separated TX and RX Connectors—Top Silkscreen ..................69

Figure 34. Split RF I/Os with Separated TX and RX Connectors—Bottom...............................70

Figure 35. Sensitivity vs. Data Rate ..........................................................................................71

Figure 36. Receiver Selectivity..................................................................................................72

Figure 37. TX Modulation (40 kbps, 20 kHz Deviation).............................................................73

Figure 38. TX Unmodulated Spectrum (917 MHz) ....................................................................73

Figure 39. TX Modulated Spectrum (917 MHz, 40 kbps, 20 kHz Deviation, GFSK) .................74

Figure 40. Synthesizer Settling Time for 1 MHz Jump Settled within 10 kHz ...........................74

Figure 41. Synthesizer Phase Noise (VCOCURR = 11) ...........................................................75

Figure 42. QFN-20 Package Dimensions................................................................................153

Figure 43. QFN-20 Landing Pattern Dimensions ....................................................................153

Si4430

6 Preliminary Rev. 0.4

LIST OF TABLES

Table 1. DC Characteristics .......................................................................................................7

Table 2. Synthesizer AC Electrical Characteristics1 ...................................................................8

Table 3. Receiver AC Electrical Characteristics1.......................................................................9

Table 4. Transmitter AC Electrical Characteristics1 .................................................................10

Table 5. Auxiliary Block Specifications1 ...................................................................................11

Table 6. Digital IO Specifications (SDO, SDI, SCLK, nSEL, and nIRQ) ...................................12

Table 7. GPIO Specifications (GPIO_0, GPIO_1, and GPIO_2) ..............................................12

Table 8. Absolute Maximum Ratings ........................................................................................13

Table 9. Operating Modes ........................................................................................................17

Table 10. Serial Interface Timing Parameters ..........................................................................18

Table 11. Operating Modes ......................................................................................................20

Table 12. Frequency Band Selection .......................................................................................27

Table 13. RX Packet Handler Configuration ............................................................................43

Table 14. Packet Handler Registers .........................................................................................44

Table 15. Minimum Receiver Settling Time ..............................................................................46

Table 16. RX Modem Configurations for FSK and GFSK ........................................................47

Table 17. Filter Bandwidth Parameters ....................................................................................49

Table 18. Channel Filter Bandwidth Settings ...........................................................................50

Table 19. ndec[2:0] Settings .....................................................................................................51

Table 20. RX Modem Configuration for OOK with Manchester Disabled .................................52

Table 21. RX Modem Configuration for OOK with Manchester Enabled .................................52

Table 22. POR Parameters ......................................................................................................53

Table 23. Temperature Sensor Range .....................................................................................58

Table 24. Antenna Diversity Control .........................................................................................65

Table 25. Split RF I/Os Bill of Materials ....................................................................................68

Table 26. Recommended Crystal Parameters .........................................................................76

Table 27. Register Descriptions ...............................................................................................77

Table 28. Interrupt or Status 1 Bit Set/Clear Description .........................................................82

Table 29. When are Individual Status Bits Set/Cleared if not Enabled as Interrupts? .............82

Table 30. Interrupt or Status 2 Bit Set/Clear Description ........................................................84

Table 31. Detailed Description of Status Registers when not Enabled as Interrupts ...............84

Table 32. Internal Analog Signals Available on the Analog Test Bus ....................................124

Table 33. Internal Digital Signals Available on the Digital Test Bus .......................................125

Si4430

Preliminary Rev. 0.4 7

1. Electrical Specifications

Table 1. DC Characteristics

Parameter Symbol Conditions Min Typ —Units

Supply Voltage Range Vdd 1.8 3.0 — V

Power Saving Modes IShutdown RC Oscillator, Main Digital Regulator,

and Low Power Digital Regulator OFF2—10—nA

IStandby Low Power Digital Regulator ON (Register values retained)

and Main Digital Regulator, and RC Oscillator OFF1—400— nA

ISleep RC Oscillator and Low Power Digital Regulator ON

(Register values retained) and Main Digital Regulator OFF1—800— nA

ISensor-LBD Main Digital Regulator and Low Battery Detector ON,

Crystal Oscillator and all other blocks OFF2—1—µA

ISensor-TS Main Digital Regulator and Temperature Sensor ON,

Crystal Oscillator and all other blocks OFF2—1—µA

IReady Crystal Oscillator and Main Digital Regulator ON,

all other blocks OFF. Crystal Oscillator buffer disabled1—600— µA

TUNE Mode Current ITune Synthesizer and regulators enabled — 9.5 — mA

RX Mode Current IRX —18.5— mA

TX Mode Current ITX_+13 txpow[2:0] = 11 (+13 dBm), VDD = 3.3 V — 28 — mA

ITX_+1 txpow[2:0] = 00 (+1 dBm), VDD = 3.3 V — 18 — mA

Notes:

1. All specification guaranteed by production test unless otherwise noted.

2. Guaranteed by qualification.

Si4430

8 Preliminary Rev. 0.4

Table 2. Synthesizer AC Electrical Characteristics1

Parameter Symbol Conditions Min Typ Max Units

Synthesizer Frequency

Range

FSYNTH 900 — 960 MHz

Synthesizer Frequency

Resolution2

FRES —312.5— Hz

Reference Frequency fREF fcrystal /3 — 10 — MHz

Reference Frequency

Input Level2

fREF_LV When using reference frequency instead

of crystal. Measured peak-to-peak (VPP)

0.7 — 1.6 V

Synthesizer Settling Time2tLOCK Measured from leaving Ready mode with

XOSC running to any frequency includ-

ing VCO Calibration

—200— µs

Residual FM2FRMS Integrated over 250 kHz bandwidth

(500 Hz lower bound of integration)

—2 4kHz

RMS

Phase Noise2L(fM)F = 10 kHz — –80 — dBc/Hz

F = 100 kHz — –90 — dBc/Hz

F = 1 MHz — –115 — dBc/Hz

F = 10 MHz — –130 — dBc/Hz

Notes:

1. All specification guaranteed by production test unless otherwise noted.

2. Guaranteed by qualification.

Si4430

Preliminary Rev. 0.4 9

Table 3. Receiver AC Electrical Characteristics1

Parameter Symbol Conditions Min Typ Max Units

RX Frequency

Range

FSYNTH 900 — 960 MHz

RX Sensitivity PRX_2 (BER < 0.1%)

(2 kbps, GFSK, BT = 0.5,

f = 5kHz)

2

—–118—dBm

PRX_40 (BER < 0.1%)

(40 kbps, GFSK, BT = 0.5,

f = 20 kHz)2

— –107 —dBm

PRX_100 (BER < 0.1%)

(100 kbps, GFSK, BT = 0.5,

f = 50 kHz)2

— –103 —dBm

PRX_125 (BER < 0.1%)

(125 kbps, GFSK, BT = 0.5,

f = 62.5 kHz)1

— –101 —dBm

PRX_OOK (BER < 0.1%)

(4.8 kbps, 350 kHz BW, OOK)2

—–110—dBm

(BER < 0.1%)

(40kbps,400kHzBW,OOK)

1

— –102 —dBm

RX Bandwidth2BW 2.6 — 620 kHz

Residual BER

Performance2

PRX_RES Up to +5 dBm Input Level — 0 0.1 ppm

Input Intercept Point,

3rd Order2

IIP3RX f1= 915 MHz, f2= 915 MHz,

P1= P2= –40 dBm

—–20—dBm

LNA Input Impedance2

(Unmatched, measured

differentially across RX

input pins)

RIN-RX 915 MHz — 40–55 —

RSSI Resolution RESRSSI — ±0.5 — dB

1-Ch Offset Selectivity2

(BER < 0.1%)

C/I1-CH Desired Ref Signal 3 dB above sensitivity.

Interferer and desired modulated with

40 kbps F = 20 kHz GFSK with BT = 0.5,

channel spacing = 150 kHz

—–31—dB

2-Ch Offset Selectivity2

(BER < 0.1%)

C/I2-CH —–35—dB

3-Ch Offset Selectivity2

(BER < 0.1%)

C/I3-CH —–40—dB

Blocking at 1 MHz21MBLOCK Desired Ref Signal 3 dB above sensitivity.

Interferer and desired modulated with

40 kbps F = 20 kHz GFSK with BT = 0.5

—–52—dB

Blocking at 4 MHz24MBLOCK —–56—dB

Blocking at 8 MHz28MBLOCK —–63—dB

Image Rejection2ImREJ IF=937 kHz — –30 — dB

Spurious Emissions2POB_RX1 Measured at RX pins

(LO feed through)

— — –54 dBm

Notes:

1. All specification guaranteed by production test unless otherwise noted.

2. Guaranteed by qualification.

Si4430

10 Preliminary Rev. 0.4

Table 4. Transmitter AC Electrical Characteristics1

Parameter Symbol Conditions Min Typ Max Units

TX Frequency

Range1

FSYNTH 900 — 960 MHz

FSK Modulation Data Rate2DRFSK 1—128kbps

OOK Modulation Data

Rate2

DROOK 1.2 — 40 kbps

Modulation Deviation1Δf Production tests maximum

limit of 320 kHz

±0.625 ±320 kHz

Modulation Deviation

Resolution

ΔfRES —0.625— kHz

Output Power Range1PTX Power control by txpow[2:0] Register

Production test at txpow[2:0] = 111

Tested at 915 MHz

–8 — +13 dBm

TX RF Output Steps2PRF_OUT controlled by txpow[2:0] Register — 3 — dB

TX RF Output Level

Variation vs. Voltage2

PRF_V Measured from VDD=3.6 V to

VDD=1.8 V

—2—dB

TX RF Output Level2

Variation vs. Temperature

PRF_TEMP –40 to +85 C—2—dB

TX RF Output Level

Variation vs. Frequency2

PRF_FREQ Measured across any one

frequency band

—1—dB

Transmit Modulation

Filtering2

B*T Gaussian Filtering Bandwith Time

Product

—0.5—

Spurious Emissions2POB-TX1 POUT =11dBm,

Frequencies <1 GHz

——–54dBm

POB-TX2 1–12.75 GHz, excluding harmonics — — –54 dBm

Harmonics2P2HARM Using Reference Design TX Matching

Network and Filter with Max Output Power

(+13 dBm). Harmonics reduce linearly with out-

put power

——–42dBm

P3HARM ——–42dBm

Notes:

1. All specification guaranteed by production test unless otherwise noted.

2. Guaranteed by qualification.

Si4430

Preliminary Rev. 0.4 11

Table 5. Auxiliary Block Specifications1

Parameter Symbol Conditions Min Typ Max Units

Temperature Sensor

Accuracy2

TSAWhen calibrated using temp

sensor offset register

—0.5—°C

Temperature Sensor

Sensitivity2

TSS—5—mV/°C

Low Battery Detector

Resolution2

LBDRES —50—mV

Low Battery Detector

Conversion Time2

LBDCT —250—µs

Microcontroller Clock

Output Frequency

MC Configurable to 30 MHz,

15 MHz, 10 MHz, 4 MHz,

3MHz,2MHz,1MHz,or

32.768 kHz

32.768K — 30M Hz

General Purpose ADC

Accuracy2

ADCENB —8—bit

General Purpose ADC

Resolution2

ADCRES —4—mV

Temp Sensor & General

Purpose ADC Conversion

Time2

ADCCT — 305 — µsec

30 MHz XTAL Start-Up time t30M —1—ms

30 MHz XTAL Cap

Resolution2

30MRES —97—fF

32 kHz XTAL Start-Up Time2t32k —6—sec

32 kHz XTAL Accuracy232KRES —100—ppm

32 kHz RC OSC Accuracy232KRCRES —2500—ppm

POR Reset Time tPOR —16—ms

Software Reset Time2tsoft —100—µs

Notes:

1. All specification guaranteed by production test unless otherwise noted.

2. Guaranteed by qualification.

Si4430

12 Preliminary Rev. 0.4

Table 6. Digital IO Specifications (SDO, SDI, SCLK, nSEL, and nIRQ)

Parameter Symbol Conditions Min Typ Max Units

Rise Time TRISE 0.1 x VDD to 0.9 x VDD, CL= 5 pF — — 8 ns

Fall Time TFALL 0.9 x VDD to 0.1 x VDD, CL= 5 pF — — 8 ns

Input Capacitance CIN ——1pF

Logic High Level Input Voltage VIH VDD –0.6 — — V

Logic Low Level Input Voltage VIL —0.6 V

Input Current IIN 0<VIN< VDD –100 — 100 nA

Logic High Level Output

Voltage

VOH IOH<1 mA source, VDD=1.8 V VDD –0.6 — — V

Logic Low Level Output Voltage VOL IOL<1 mA sink, VDD=1.8 V — — 0.6 V

Note: All specification guaranteed by production test unless otherwise noted.

Table 7. GPIO Specifications (GPIO_0, GPIO_1, and GPIO_2)

Parameter Symbol Conditions Min Typ Max Units

Rise Time TRISE 0.1 x VDD to 0.9 x VDD,

CL= 10 pF, DRV<1:0>=HH

——8ns

Fall Time TFALL 0.9 x VDD to 0.1 x VDD,

CL= 10 pF, DRV<1:0>=HH

——8ns

Input Capacitance CIN ——1pF

Logic High Level Input Voltage VIH VDD –0.6 — V

Logic Low Level Input Voltage VIL ——0.6V

Input Current IIN 0<VIN< VDD –100 — 100 nA

Input Current If Pullup is Activated IINP VIL=0 V 5 — 25 µA

Maximum Output Current IOmaxLL DRV<1:0>=LL 0.1 0.5 0.8 mA

IOmaxLH DRV<1:0>=LH 0.9 2.3 3.5 mA

IOmaxHL DRV<1:0>=HL 1.5 3.1 4.8 mA

IOmaxHH DRV<1:0>=HH 1.8 3.6 5.4 mA

Logic High Level Output Voltage VOH IOH< IOmax source,

VDD=1.8 V

VDD –0.6 — — V

Logic Low Level Output Voltage VOL IOL< IOmax sink,

VDD=1.8 V

——0.6V

Note: All specification guaranteed by production test unless otherwise noted.

Si4430

Preliminary Rev. 0.4 13

Table 8. Absolute Maximum Ratings

Parameter Value Unit

VDD to GND –0.3, +3.6 V

VDD to GND on TX Output Pin –0.3, +8.0 V

Voltage on Digital Control Inputs –0.3, VDD + 0.3 V

Voltage on Analog Inputs –0.3, VDD + 0.3 V

RX Input Power +10 dBm

Operating Ambient Temperature Range TA–40 to +85 C

Thermal Impedance JA 30 C/W

Junction Temperature TJ+125 C

Storage Temperature Range TSTG –55 to +125 C

Note: Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These

are stress ratings only and functional operation of the device at or beyond these ratings in the operational sections of

the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect

device reliability. Caution: ESD sensitive device.

Power Amplifier may be damaged if switched on without proper load or termination connected.

Si4430

14 Preliminary Rev. 0.4

1.1. Definition of Test Conditions

Production Test Conditions:

TA=+25°C

VDD =+3.3VDC

External reference signal (XOUT) = 1.0 VPP at 30 MHz, centered around 0.8 VDC

Production test schematic (unless noted otherwise)

All RF input and output levels referred to the pins of the Si4430 (not the RF module)

Extreme Test Conditions:

TA= –40 to +85 °C

VDD = +1.8 to +3.6 VDC

External reference signal (XOUT) = 0.7 to 1.6 VPP at 30 MHz centered around 0.8 VDC

Production test schematic (unless noted otherwise)

All RF input and output levels referred to the pins of the Si4430 (not the RF module)

Test Notes:

All electrical parameters with Min/Max values are guaranteed by one (or more) of the following test methods.

Electrical parameters shown with only Typical values are not guaranteed.

Guaranteed by design and/or simulation but not tested.

Guaranteed by Engineering Qualification testing at Extreme Test Conditions.

Guaranteed by 100% Production Test Screening at Production Test Conditions.

Si4430

Preliminary Rev. 0.4 15

2. Functional Description

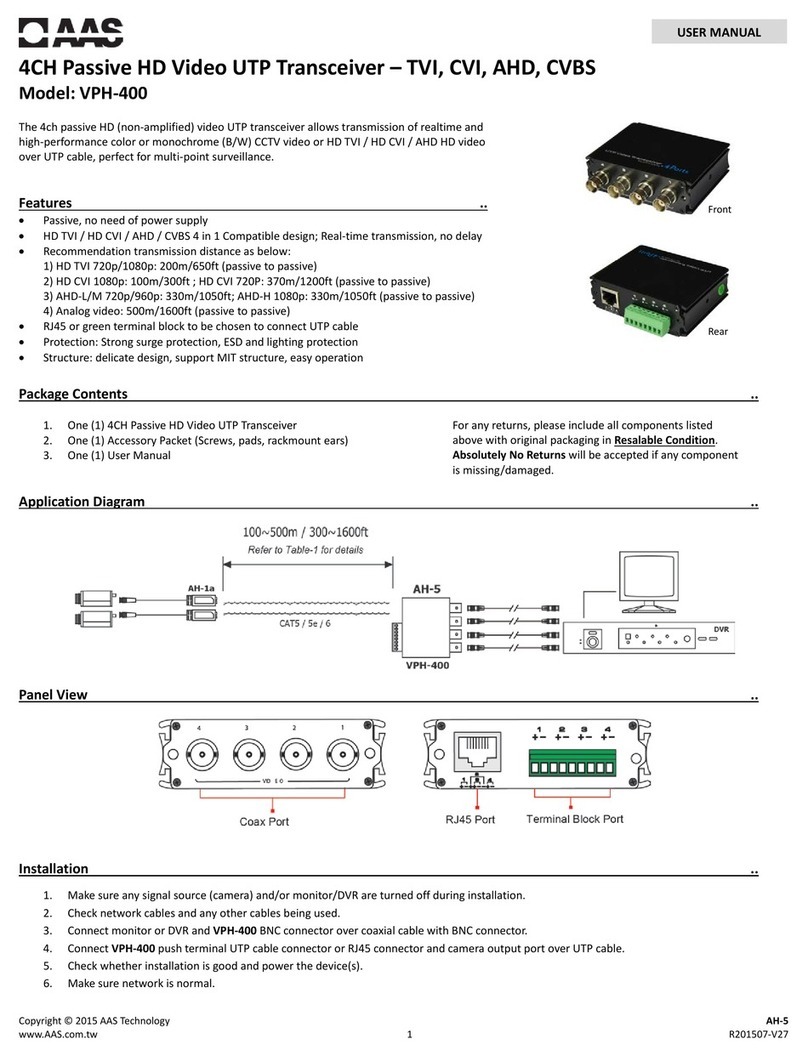

The Si4430 is a 100% CMOS ISM wireless transceiver

with continuous frequency tuning over the complete

900–960 MHz band. The wide operating voltage range

of 1.8–3.6 V and low current consumption makes the

Si4430 and ideal solution for battery powered

applications.

The Si4430 operates as a time division duplexing (TDD)

transceiver where the device alternately transmits and

receives data packets. The device uses a single-

conversion, image-reject mixer to downconvert the 2-

level FSK/GFSK/OOK modulated receive signal to a low

IF frequency. Following a programmable gain amplifier

(PGA) the signal is converted to the digital domain by a

high performance ADC allowing filtering,

demodulation, slicing, error correction, and packet

handling to be performed in the built-in DSP increasing

the receiver’s performance and flexibility versus analog

based architectures. The demodulated signal is then

output to the system MCU through a programmable

GPIO or via the standard SPI bus by reading the 64-

byte RX FIFO.

A single high precision local oscillator (LO) is used for

both transmit and receive modes since the transmitter

and receiver do not operate at the same time. The LO is

generated by an integrated VCO and Fractional-N

PLL synthesizer. The synthesizer is designed to support

configurable data rates, output frequency, frequency

deviation, and Gaussian filtering at any frequency

between 900–960 MHz. The transmit FSK data is

modulated directly into the data stream and can be

shaped by a Gaussian low-pass filter to reduce

unwanted spectral content.

The PA output power can be configured between –8

and +13 dBm in 3 dB steps. The PA is single-ended to

allow for easy antenna matching and low BOM cost.

The PA incorporates automatic ramp-up and ramp-

down control to reduce unwanted spectral spreading.

The Si4430 supports frequency hopping, TX/RX switch

control, and antenna diversity switch control to extend

the link range and improve performance. Antenna

diversity is completely integrated into the Si4430 and

can improve the system link budget by 8–10 dB,

resulting in substantial range increases depending on

the environmental conditions.

The Si4430 is designed to work with a microcontroller,

crystal, and a few passives to create a very low cost

system as shown Figure 1. Voltage regulators are

integrated on-chip which allow for a wide range of

operating supply voltage conditions from +1.8 to +3.6 V.

A standard 4-pin SPI bus is used to communicate with

the microcontroller. Three configurable general purpose

I/Os are available for use to tailor towards the needs of

the system. A more complete list of the available GPIO

functions is shown in "8. Auxiliary Functions" on page

53 but just to name a few, microcontroller clock output,

Antenna Diversity, POR, and specific interrupts. A

limited number of passive components are needed to

match the LNA and PA.

The application shown in Figure 1 is designed for a

system with an TX/RX direct-tie configuration without

the use of a TX/RX switch. Most lower power

applications will use this configuration. A direct-tie

reference design is available from Silicon Laboratories

applications support.

For applications seeking improved performance in the

presence of multipath fading antenna diversity can be

used. Antenna diversity includes a switch to select the

optimal antenna between a pair of antennas for

improved performance. The Antenna Diversity Control

Algorithm is completely integrated into the chip and is

discussed further in Figure 24 on page 55. A complete

Antenna Diversity reference design is available from

Silicon Laboratories applications support.

An application example with a separate RX and TX

antenna is shown in Figure 31, “Split RF I/Os with

Separated TX and RX Connectors—Schematic,” on

page 67. This example is used for testing of the TX and

RX paths in a lab environment and shows, conceptually,

the matching of the TX and RX antennas.

Si4430

16 Preliminary Rev. 0.4

Figure 1. Si4430 RX/TX Direct-Tie Application Example

X1

30MHz

supply voltage

microcontroller

VDD

VSS

GP1

GP2

GP3

GP4

100n

C7

100p

C8

C1

L1

L3 L2

C6

C3 C2

1u

R1, L1-L5 and C1-C4 values depend on frequency band,

antenna impedance, output power and supply voltage range.

Programmable load capacitors for X1 are integrated.

VDD_RF SCLK

19

18

17

16

1

2

3

4

15

14

13

7

8

9

10

SDI

SDO

VDD_D

RXn

TX

RFp

GPIO0

GPIO1

VDR

nIRQ

SDN

XOUT

nSEL

GPIO2

5

VR_IF

6

NC

NC

20

XIN

11

12

C10

GP5

1u

C9

1u

L4

C4

C5

Si4430

Si4430

Preliminary Rev. 0.4 17

2.1. Operating Modes

The Si4430 provides several modes of operation which can be used to optimize the power consumption of the

device application. Depending upon the system communication protocol, the optimal trade-off between the radio

wake time and power consumption can be achieved.

Table 9 summarizes the modes of operation of the Si4430. In general, any given mode of operation may be

classified as an Active mode or a Power Saving mode. The table indicates which block(s) are enabled (active) in

each corresponding mode. With the exception the Shutdown mode, all can be dynamically selected by sending the

appropriate commands over the SPI in order to optimize the average current consumption. An “X” in any cell

means that, in the given mode of operation, that block can be independently programmed to be either ON or OFF,

without noticeably affecting the current consumption. The SPI circuit block includes the SPI interface and the

register space. The 32 kHz OSC circuit block includes the 32.768 kHz RC oscillator or 32.768 kHz crystal

oscillator, and wake-up timer. AUX (Auxiliary Blocks) includes the temperature sensor, general purpose ADC, and

low-battery detector.

Table 9. Operating Modes

Mode

Name Circuit Blocks

Digital LDO SPI 32 kHz OSC AUX 30 MHz

XTAL PLL PA RX IVDD

Shutdown OFF (Register

contents lost)

OFF OFF OFF OFF OFF OFF OFF 10 nA

Standby ON (Register

contents

retained)

ON OFF OFF OFF OFF OFF OFF 400 nA

Sleep ON ON X OFF OFF OFF OFF 800 nA

Sensor ON X ON OFF OFF OFF OFF 1 µA

Ready ON X X ON OFF OFF OFF 600 µA

Tuning ON X X ON ON OFF OFF 9.5 mA

Transmit ON X X ON ON ON OFF 28 mA*

Receive ON X X ON ON OFF ON 18.5 mA

*Note: 28 mA at +13 dBm.

Si4430

18 Preliminary Rev. 0.4

3. Controller Interface

3.1. Serial Peripheral Interface (SPI)

The Si4430 communicates with the host MCU over a 3 wire SPI interface: SCLK, SDI, and nSEL. The host MCU

can also read data from internal registers on the SDO output pin. A SPI transaction is a 16-bit sequence which

consists of a Read-Write (R/W) select bit, followed by a 7-bit address field (ADDR), and an 8-bit data field (DATA),

as demonstrated in Figure 2. The 7-bit address field supports reading from or writing to one of the 128, 8-bit control

registers. The R/W select bit determines whether the SPI transaction is a write or read transaction. If R/W = 1, it

signifies a WRITE transaction, while R/W = 0 signifies a READ transaction. The contents (ADDR or DATA) are

latched into the Si4430 every eight clock cycles. The timing parameters for the SPI interface are shown in Table 10.

The SCLK rate is flexible with a maximum rate of 10 MHz.

Figure 2. SPI Timing

To read back data from the Si4430, the R/W bit must be set to 0 followed by the 7-bit address of the register from

which to read. The 8 bit DATA field following the 7-bit ADDR field is ignored when R/W = 0. The next eight negative

edge transitions of the SCLK signal will clock out the contents of the selected register. The data read from the

selected register will be available on the SDO output pin. The READ function is shown in Figure 3. After the READ

function is completed the SDO pin will remain at either a logic 1 or logic 0 state depending on the last data bit

clocked out (D0). When nSEL goes high the SDO output pin will be pulled high by internal pullup.

Table 10. Serial Interface Timing Parameters

Symbol Parameter Min (nsec) Diagram

tCH Clock high time 40

tCL Clock low time 40

tDS Data setup time 20

tDH Data hold time 20

tDD Output data delay time 20

tEN Output enable time 20

tDE Output disable time 50

tSS Select setup time 20

tSH Select hold time 50

tSW Select high period 80

nSEL

SCLK

SDI

MSB

LSB

A2 A1 A0 D7 D6 D5 D4 D3 D2 D1

D0

A4

xx

xx

A3 RW A7A6

A5

RW

Data

Address

SDI

SCLK

SDO

nSEL

tCL tCH

t

DS tDH tDD

tSS

t

E

N

tSH

t

DE

t

SW

Si4430

Preliminary Rev. 0.4 19

Figure 3. SPI Timing—READ Mode

The SPI interface contains a burst read/write mode which will allows for reading/writing sequential registers without

having to re-send the SPI address. When the nSEL bit is held low while continuing to send SCLK pulses, the SPI

interface will automatically increment the ADDR and read from/write to the next address. An SPI burst write

transaction is demonstrated in Figure 4 and burst read in Figure 3. As long as nSEL is held low, input data will be

latched into the Si4430 every eight SCLK cycles. A burst read transaction is also demonstrated in Figure 5.

Figure 4. SPI Timing—Burst Write Mode

Figure 5. SPI Timing—Burst Read Mode

nSEL

SCLK

SDI

First Bit

Last Bit

A0

D7

=X

SDO D7

A1A2

First Bit

Last Bit

A3

D6

=X

D5

=X

D4

=X

D3

=X

D2

=X

D1

=X

D0

=X

D6 D5 D4 D3 D2 D1 D0

A4

A5

A6

RW

=0

nSEL

SCLK

SDI

First Bit

A0

D7

=X

A1

A2

A3

D6

=X

D5

=X

D4

=X

D3

=X

D2

=X

D1

=X

D0

=X

A4

A5

A6

RW

=1

Last Bit

D7

=X

D6

=X

D5

=X

D4

=X

D3

=X

D2

=X

D1

=X

D0

=X

nSEL

SCLK

SDI

First Bit

Last Bit

A0

D7

=X

SDO D7

A1

A2

First Bit

A3

D6

=X

D

5

=X

D

4

=X

D3

=X

D2

=X

D1

=X

D0

=X

D6 D5 D4 D3 D2 D1 D0

A4

A5

A6

RW

=0

D7 D6 D5 D4

D3

D2

D1 D0

Si4430

20 Preliminary Rev. 0.4

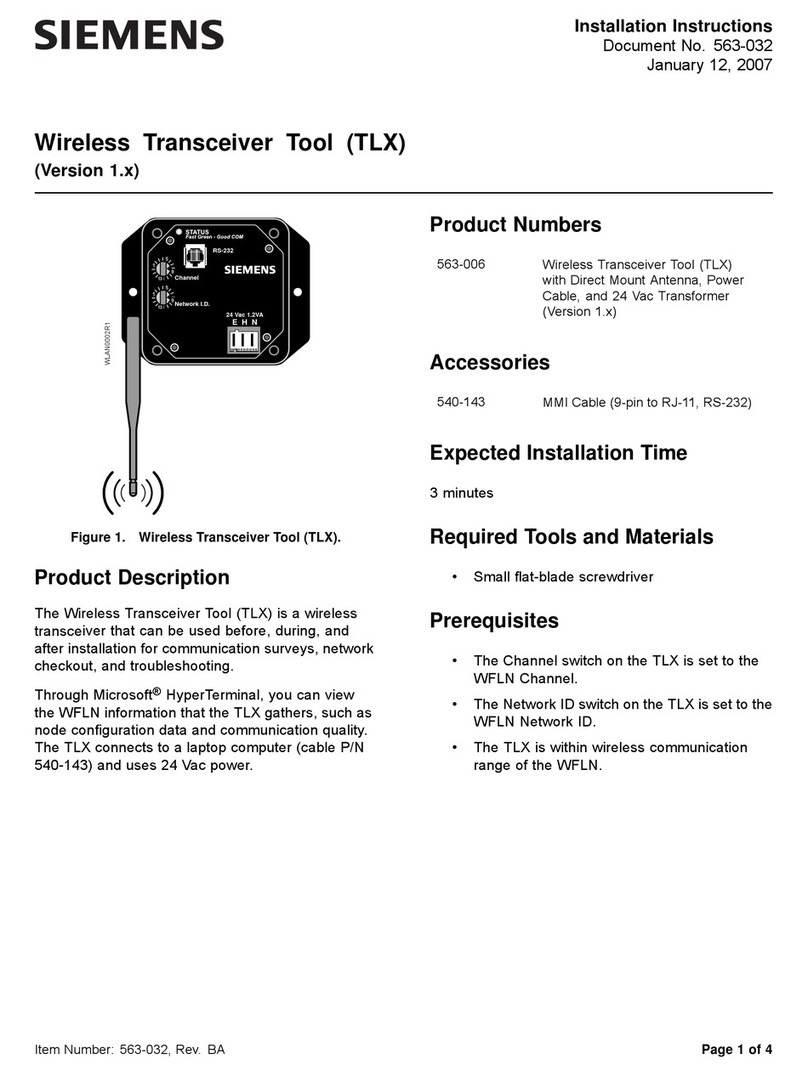

3.2. Operating Mode Control

There are four primary states in the Si4430 radio state machine: SHUTDOWN, IDLE, TX, and RX (see Figure 6).

The SHUTDOWN state completely shuts down the radio to minimize current consumption. There are five different

configurations/options for the IDLE state which can be selected to optimize the chip to the applications needs.

"Register 07h. Operating Mode and Function Control 1" controls which operating mode/state is selected. The TX

and RX state may be reached automatically from any of the IDLE states by setting the txon/rxon bits in "Register

07h. Operating Mode and Function Control 1". Table 11 shows each of the operating modes with the time required

to reach either RX or TX mode as well as the current consumption of each mode.

The output of the LPLDO is internally connected in parallel to the output of the main digital regulator (and is

available externally at the VR_DIG pin); this common digital supply voltage is connected to all digital circuit blocks,

including the digital modem, crystal oscillator, and SPI and register space. The LPLDO has extremely low

quiescent current consumption but limited current supply capability; it is used only in the IDLE-STANDBY and

IDLE-SLEEP modes.

Figure 6. State Machine Diagram

Table 11. Operating Modes

State/Mode xtal pll wt LBDor

TS Response Time to Current in State /Mode

[µA]

TX RX

Shut Down State X X X X 16.21 ms 16.21 ms 10 nA

Idle States:

Standby Mode

Sleep Mode

Sensor Mode

Ready Mode

Tune Mode

0

0

0

1

1

0

0

0

0

1

0

1

X

X

X

0

0

1

X

X

1.21 ms

210 µs

200 µs

1.21 ms

210 µs

200 µs

400 nA

800 nA

1µA

600 µA

9.5 mA

TX State 1 1 X X NA 200 µs 28 mA @ +13 dBm

RX State 1 1 X X 200 µs NA 18.5 mA

SHUT DWN

IDLE*

TX RX

*Five Different Options for IDLE

Table of contents

Other Silicon Laboratories Transceiver manuals

Silicon Laboratories

Silicon Laboratories Si4432 User manual

Silicon Laboratories

Silicon Laboratories Si4355 Operating instructions

Silicon Laboratories

Silicon Laboratories EZRADIOPRO Si4438 User manual

Silicon Laboratories

Silicon Laboratories Si4438-C User manual

Silicon Laboratories

Silicon Laboratories Si4455 Series User manual

Silicon Laboratories

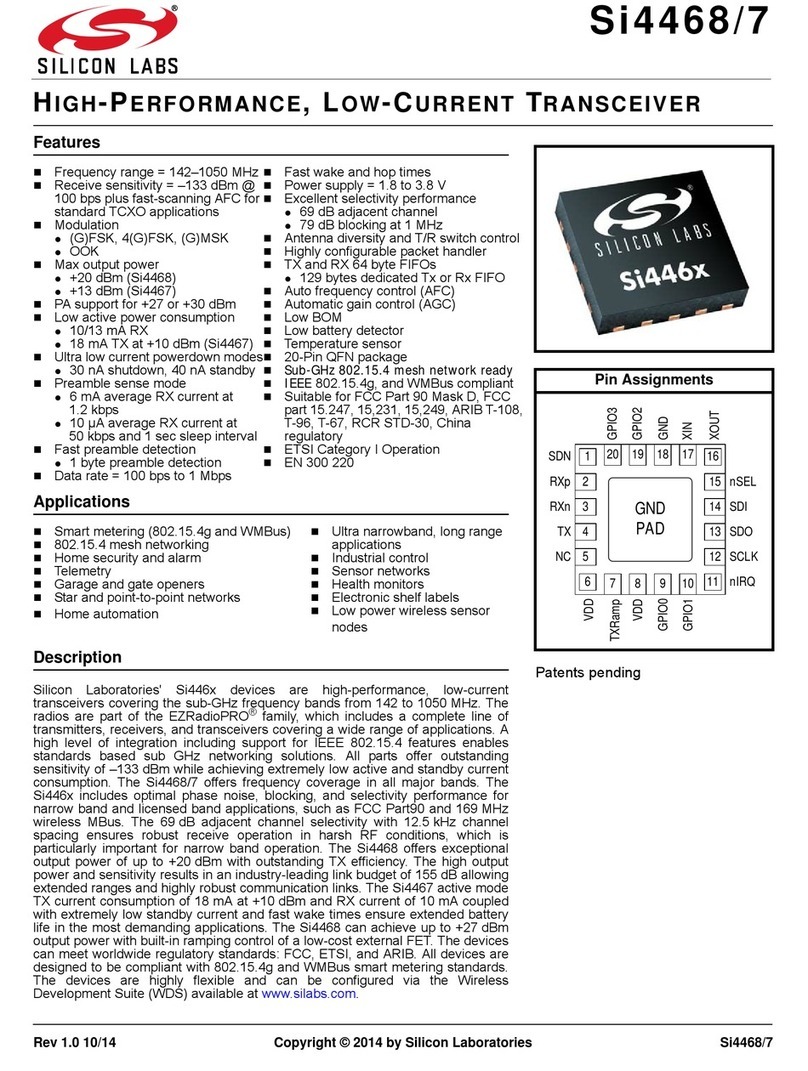

Silicon Laboratories Si4468/7 User manual

Silicon Laboratories

Silicon Laboratories Si4432 User manual

Silicon Laboratories

Silicon Laboratories SI4421 User manual