– 2 –

TABLE OF CONTENTS

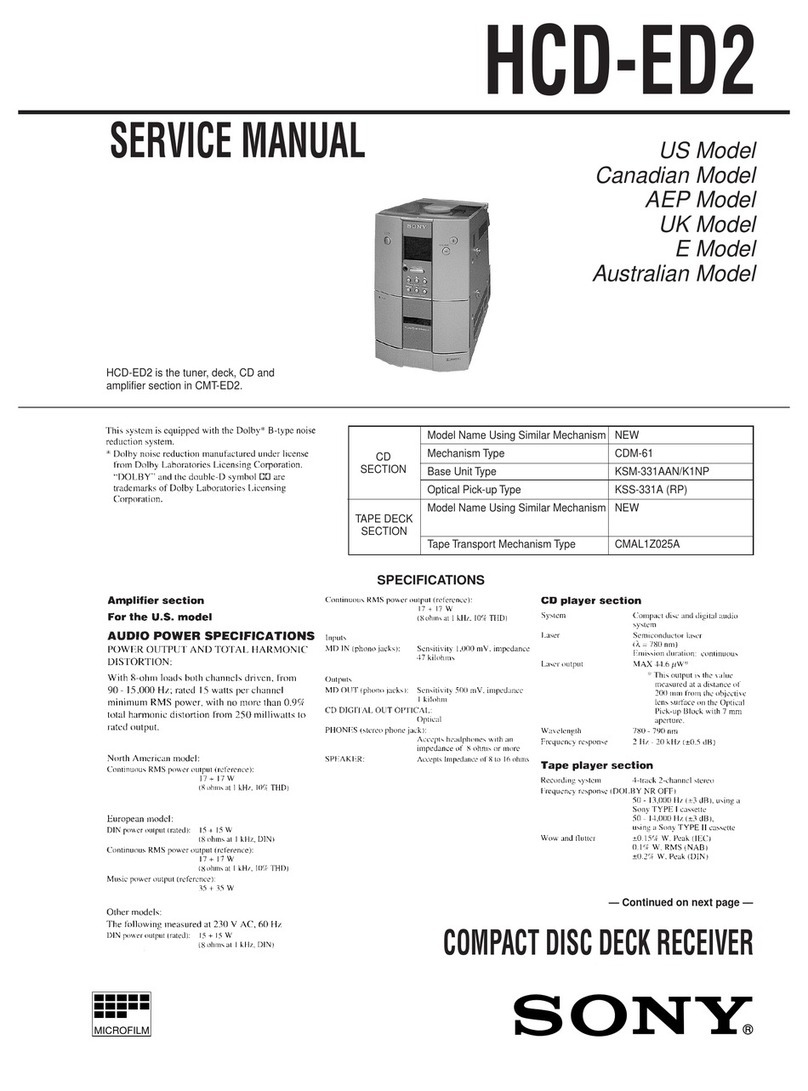

1. GENERAL

Listening to the Sound of a Connected Component ............... 3

2. DISASSEMBLY

2-1. Cover Assy .......................................................................... 5

2-2. Panel Assy, Front................................................................. 5

2-3. Panel Assy, Sub ................................................................... 6

2-4. TX Board ............................................................................ 6

3. SERVICE MODE

3-1. General ................................................................................ 7

3-2. Setting the Test Mode.......................................................... 7

3-3. Releasing the Test Mode ..................................................... 7

3-4. Test Mode ............................................................................ 7

4. ELECTRICAL ADJUSTMENTS................................... 8

5. DIAGRAMS

5-1. Block Diagram –Processor Section–...................................9

5-2. Block Diagram –Transmitter Section–.............................. 11

5-3. Printed Wiring Board

–Processor, Transmitter Section– ...................................... 14

5-4. Schematic Diagram –Processor Section– ......................... 17

5-5. Schematic Diagram –Transmitter Section– ...................... 20

5-6. Printed Wiring Board –LED Section– .............................. 22

5-7. Schematic Diagram –LED Section– ................................. 23

5-8. Printed Wiring Board –Amplifier Section–....................... 25

5-9. Schematic Diagram –Amplifier Section– ......................... 26

5-10. IC Pin Descriptions ........................................................... 29

6. EXPLODEDVIEW........................................................... 34

7. ELECTRICAL PARTS LIST......................................... 35