1

CONTENTS

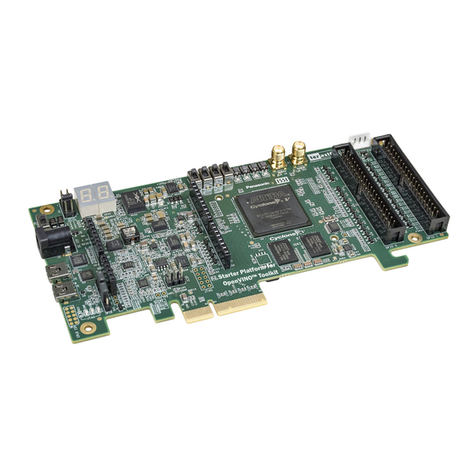

CHAPTER 1 DE1-SOC DEVELOPMENT KIT ........................................................................................................3

1.1 PACKAGE CONTENTS.................................................................................................................................................3

1.2 DE1-SOCSYSTEM CD..............................................................................................................................................4

1.3 GETTING HELP..........................................................................................................................................................4

CHAPTER 2 INTRODUCTION OF THE DE1-SOC BOARD .................................................................................5

2.1 LAYOUTAND COMPONENTS......................................................................................................................................5

2.2 BLOCK DIAGRAM OF THE DE1-SOCBOARD.............................................................................................................7

CHAPTER 3 USING THE DE1-SOC BOARD........................................................................................................10

3.1 BOARD SETUP.........................................................................................................................................................10

3.1.1 FPGACONFIGURATION MODE SETTING ..............................................................................................................10

3.1.2 HPS BOOTSELAND CLKSELSETTING ............................................................................................................. 11

3.2 CONFIGURING THE CYCLONE VSOCFPGA ...........................................................................................................13

3.3 BOARD STATUS ELEMENTS .....................................................................................................................................18

3.4 BOARD RESET ELEMENTS.......................................................................................................................................19

3.5 CLOCK CIRCUITRY ..................................................................................................................................................20

3.6 INTERFACE ON FPGA..............................................................................................................................................21

3.6.1 USER PUSH-BUTTONS,SWITCHES AND LEDS ON FPGA ......................................................................................22

3.6.2 USING THE 7-SEGMENT DISPLAYS ........................................................................................................................25

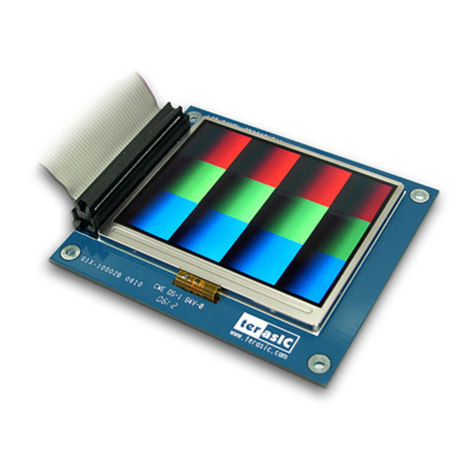

3.6.3 USING THE 2X20 GPIO EXPANSION HEADERS .....................................................................................................27

3.6.4 USING THE 24-BIT AUDIO CODEC.......................................................................................................................29

3.6.5 I2C MULTIPLEXER ...............................................................................................................................................30

3.6.6 VGA....................................................................................................................................................................31

3.6.7 TVDECODER.......................................................................................................................................................34

3.6.8 IR RECEIVER........................................................................................................................................................36

3.6.9 IR EMITTER LED.................................................................................................................................................36

3.6.10 SDRAM MEMORY ON FPGA.............................................................................................................................37

3.6.11 PS/2 SERIAL PORT..............................................................................................................................................39

3.6.12 A/D CONVERTER AND 2X5HEADER...................................................................................................................41

3.7 INTERFACE ON HARD PROCESSOR SYSTEM (HPS) ..................................................................................................42

3.7.1 USER PUSH-BUTTON AND LED ON HPS...............................................................................................................42

3.7.2 GIGABIT ETHERNET .............................................................................................................................................43

3.7.3 UART..................................................................................................................................................................44

3.7.4 DDR3 MEMORY ON HPS .....................................................................................................................................45

3.7.5 QSPI FLASH.........................................................................................................................................................47