Table of Contents

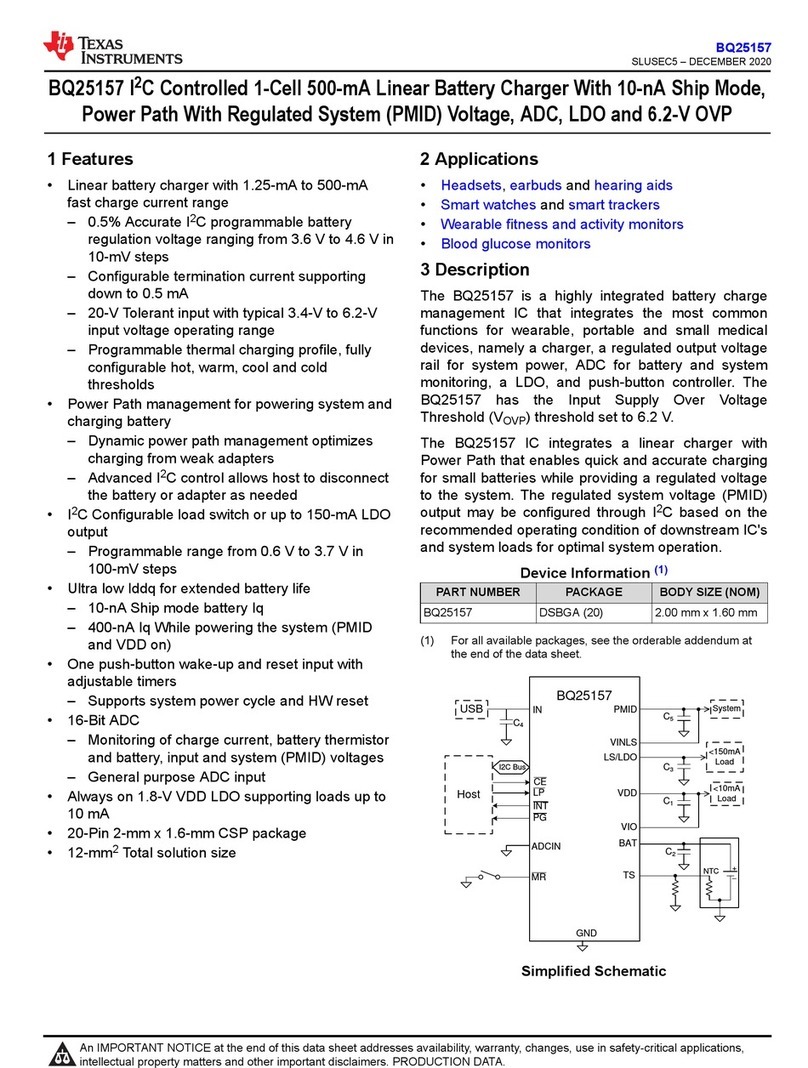

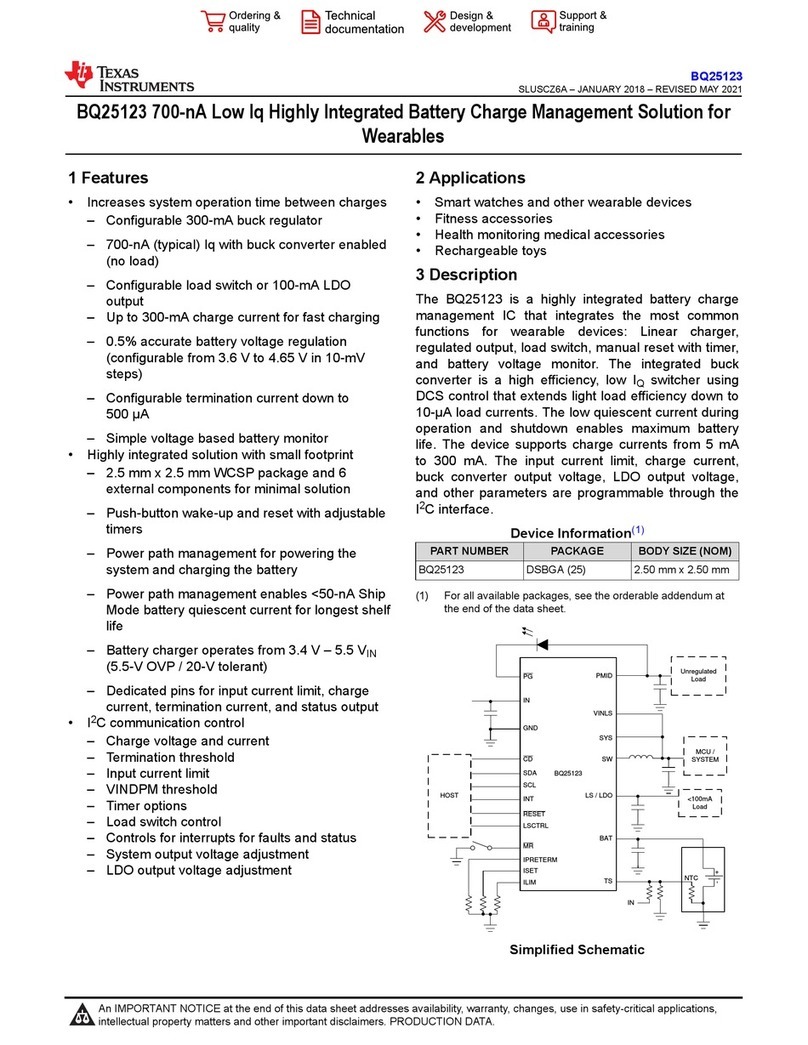

1 Features............................................................................1

2 Applications..................................................................... 1

3 Description.......................................................................1

4 Revision History.............................................................. 2

5 Description (continued).................................................. 3

6 Device Comparison Table...............................................3

7 Pin Configuration and Functions...................................4

8 Specifications.................................................................. 6

8.1 Absolute Maximum Ratings........................................ 6

8.2 ESD Ratings............................................................... 6

8.3 Recommended Operating Conditions.........................6

8.4 Thermal Information....................................................7

8.5 Electrical Characteristics.............................................8

8.6 Timing Requirements................................................12

8.7 Typical Characteristics..............................................15

9 Detailed Description......................................................17

9.1 Overview................................................................... 17

9.2 Functional Block Diagram......................................... 17

9.3 Feature Description...................................................18

9.4 Device Functional Modes..........................................30

9.5 Programming............................................................ 32

9.6 Register Maps...........................................................35

10 Application and Implementation................................ 48

10.1 Application Information........................................... 48

10.2 Typical Application.................................................. 48

11 Power Supply Recommendations..............................63

12 Layout...........................................................................64

12.1 Layout Guidelines................................................... 64

12.2 Layout Example...................................................... 64

13 Device and Documentation Support..........................65

13.1 Device Support....................................................... 65

13.2 Receiving Notification of Documentation Updates..65

13.3 Trademarks.............................................................65

13.4 Support Resources................................................. 65

13.5 Electrostatic Discharge Caution..............................65

13.6 Glossary..................................................................65

14 Mechanical, Packaging, and Orderable

Information.................................................................... 65

4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Revision * (April 2018) to Revision A (January 2021) Page

• Added Safety-Related Certification to Features................................................................................................. 1

• Added Device Comparison Table....................................................................................................................... 3

• Changed Storage Temperature.......................................................................................................................... 6

• Changed VD(PPM) to V(DPPM) .............................................................................................................................. 8

• Changed RDS(ON_LDO) ........................................................................................................................................ 8

• Changed Figure 8-2 .........................................................................................................................................12

• Deleted Update STAT to fault in VIN_UV actions in Fault and Status Condition Responses........................... 30

• Changed VIN_UV description...........................................................................................................................36

• Deleted I2C Address from title.......................................................................................................................... 39

• Changed reset state from 0100 1010 to 0100 0010......................................................................................... 47

BQ25121A

SLUSDA7A – APRIL 2018 – REVISED JANUARY 2021 www.ti.com

2Submit Document Feedback Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: BQ25121A