Texas Instruments LMK04826 User manual

Other Texas Instruments Motherboard manuals

Texas Instruments

Texas Instruments TAS5508-5142K7EVM User manual

Texas Instruments

Texas Instruments BQ25616J User manual

Texas Instruments

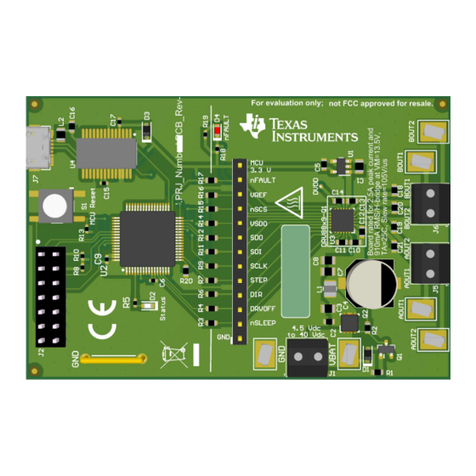

Texas Instruments DRV8899-Q1 User manual

Texas Instruments

Texas Instruments TPS65986EVM User manual

Texas Instruments

Texas Instruments TPS65300EVM User manual

Texas Instruments

Texas Instruments BQ25720 User manual

Texas Instruments

Texas Instruments DRV201 User manual

Texas Instruments

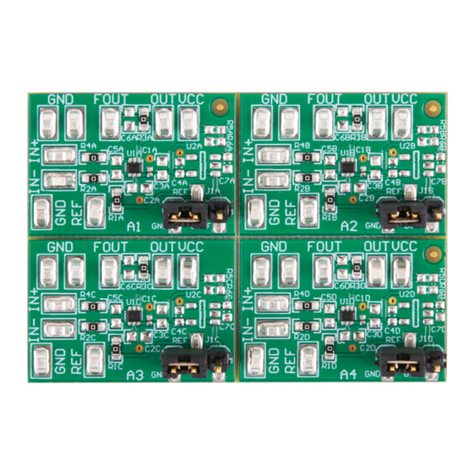

Texas Instruments INA185EVM User manual

Texas Instruments

Texas Instruments UCC25230EVM-662 User manual

Texas Instruments

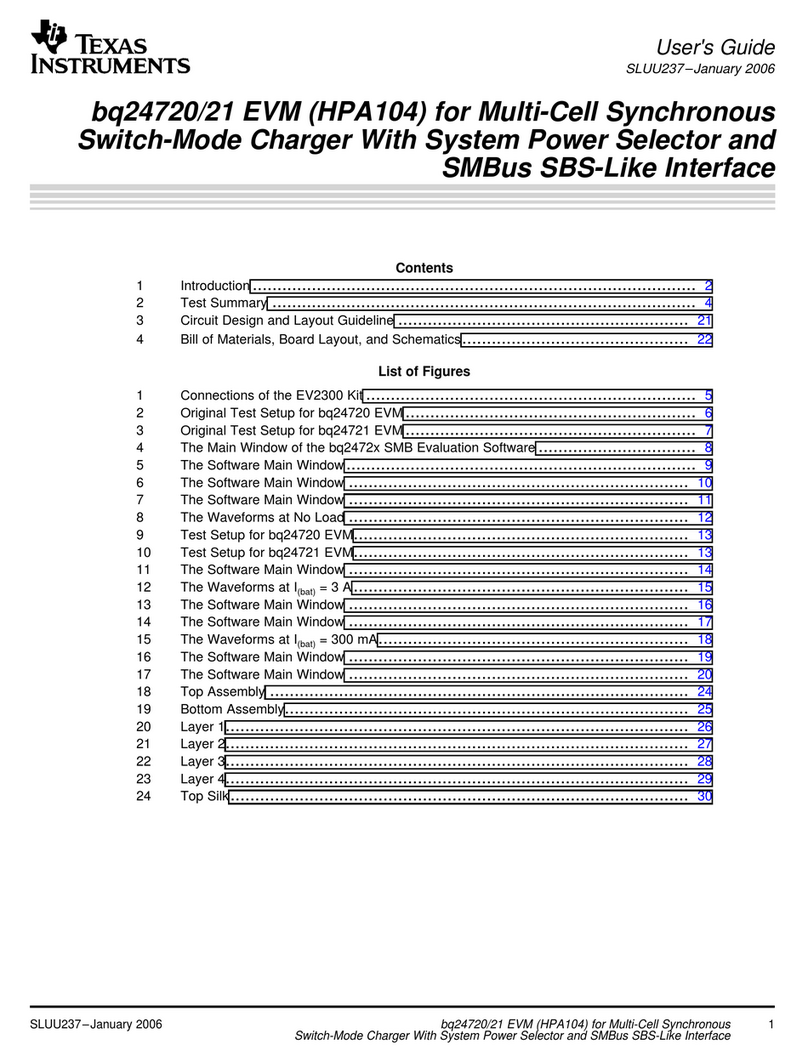

Texas Instruments bq24720 EVM User manual

Texas Instruments

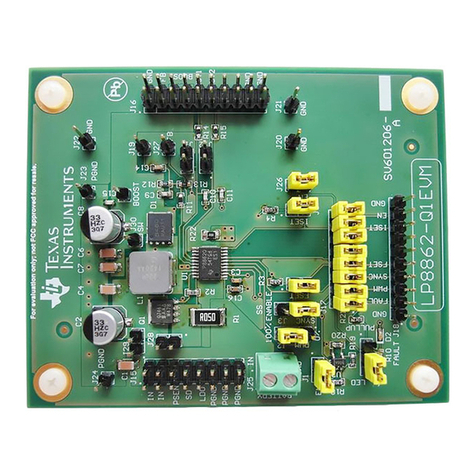

Texas Instruments LP8862-Q1EVM User manual

Texas Instruments

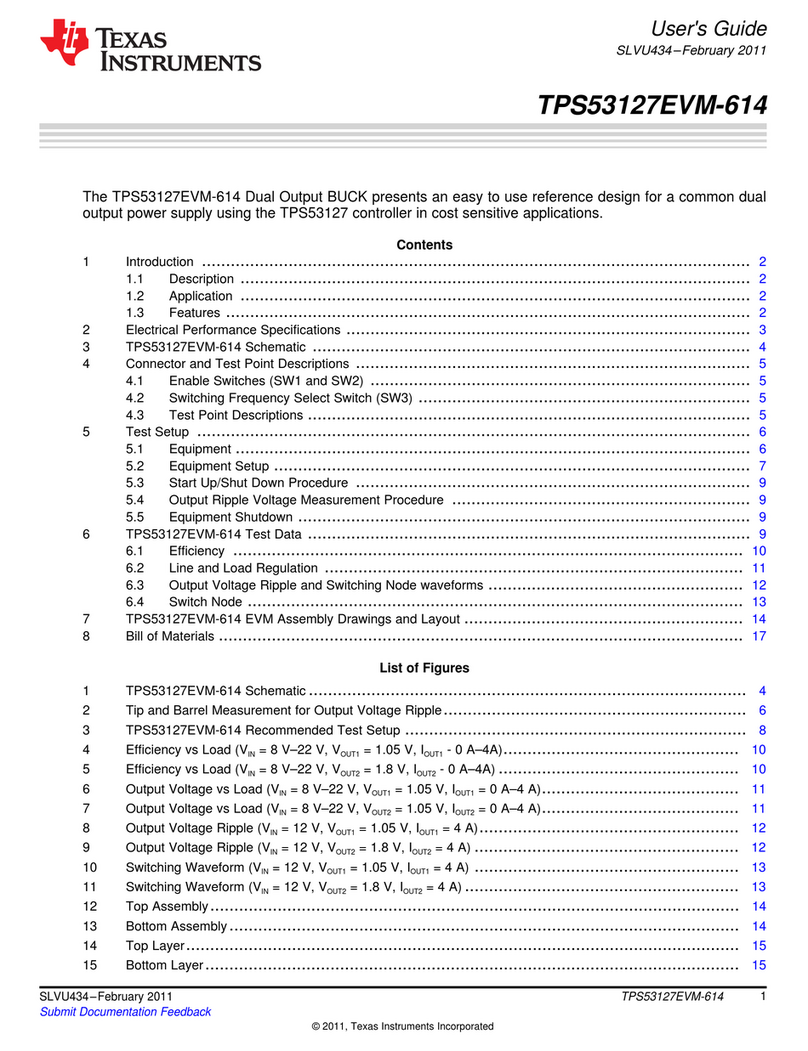

Texas Instruments TPS53127EVM-614 User manual

Texas Instruments

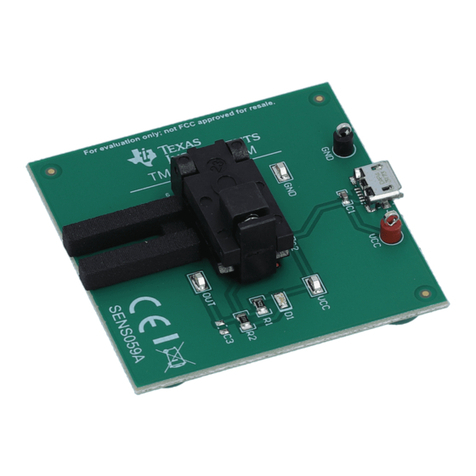

Texas Instruments TMAG5123EVM User manual

Texas Instruments

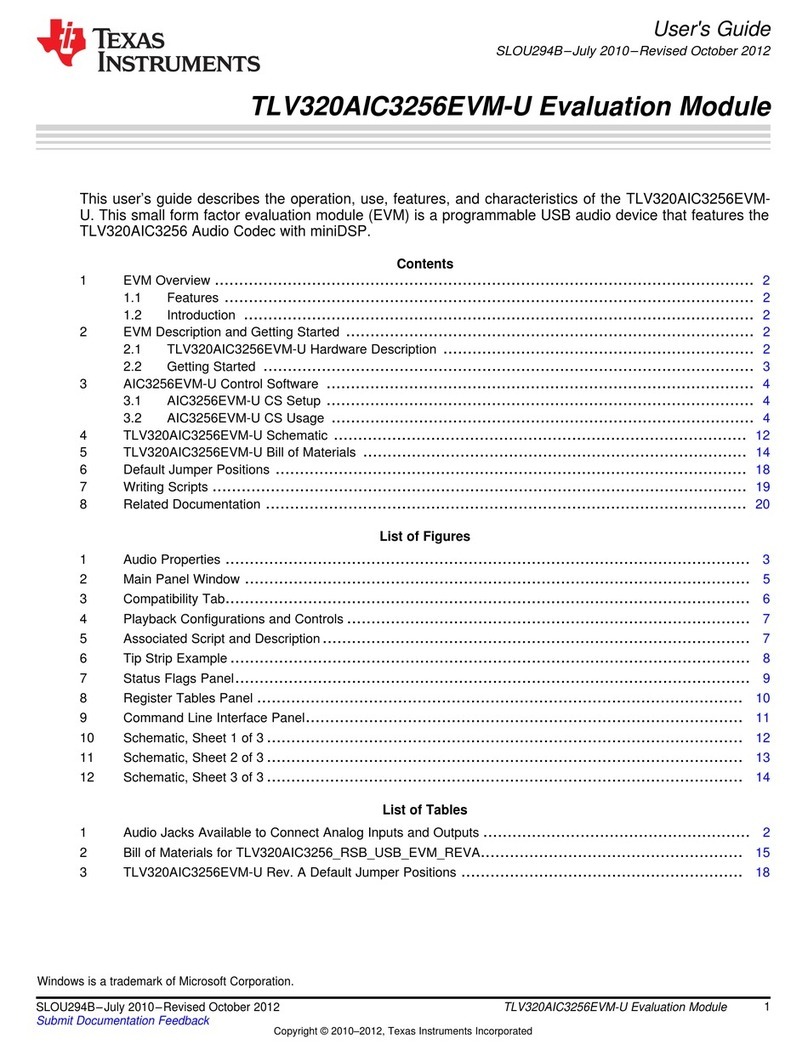

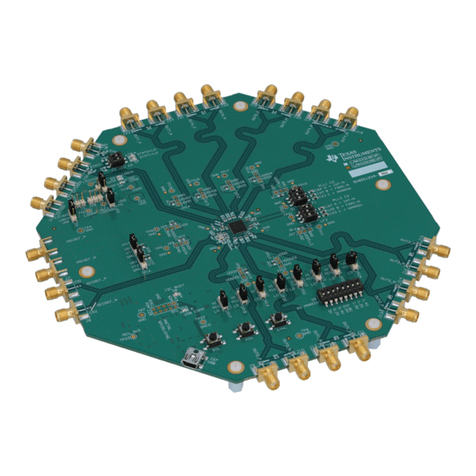

Texas Instruments TLV320AIC3256EVM-U User manual

Texas Instruments

Texas Instruments LMK03328EVM User manual

Texas Instruments

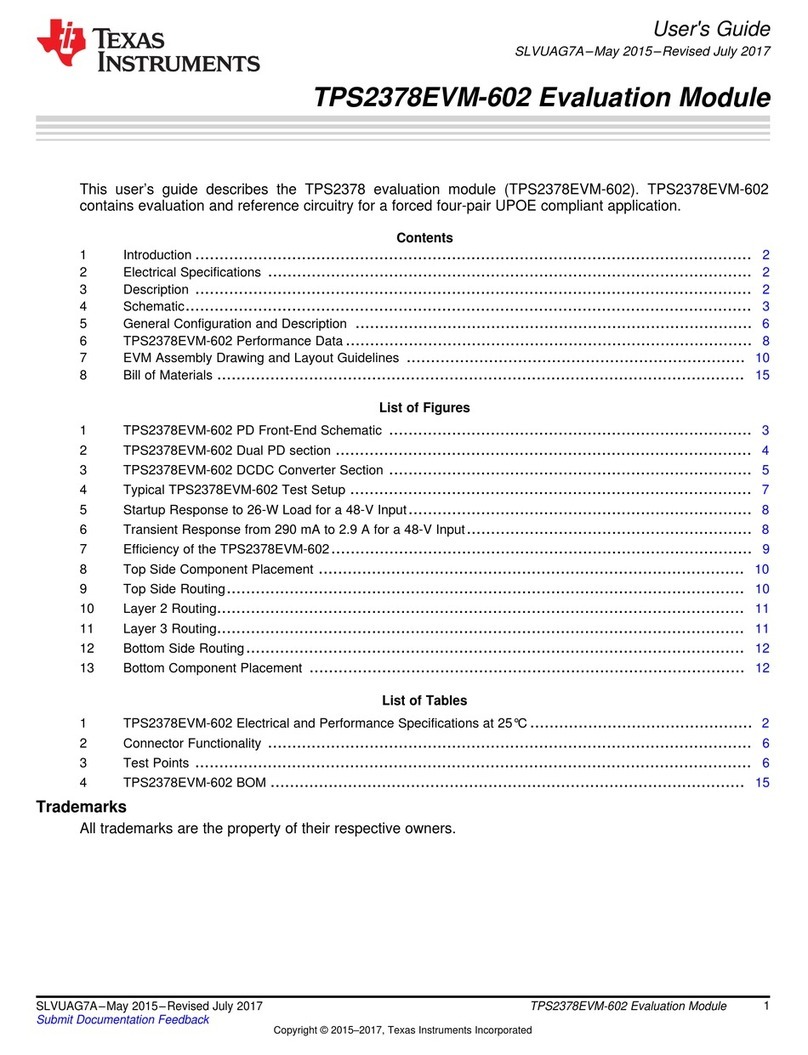

Texas Instruments TPS2378EVM-602 User manual

Texas Instruments

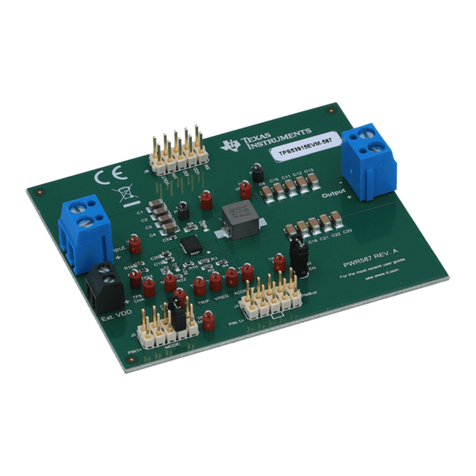

Texas Instruments TPS53915 User manual

Texas Instruments

Texas Instruments TPS53355EVM-864 User manual

Texas Instruments

Texas Instruments EZShunt INA780 User manual

Texas Instruments

Texas Instruments TPS65295EVM-079 User manual