System Description

www.ti.com

2TIDUEW7–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Integrated Power Supply Reference Design for NXP i.MX 6ULL

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other

important disclaimers and information.

1 System Description

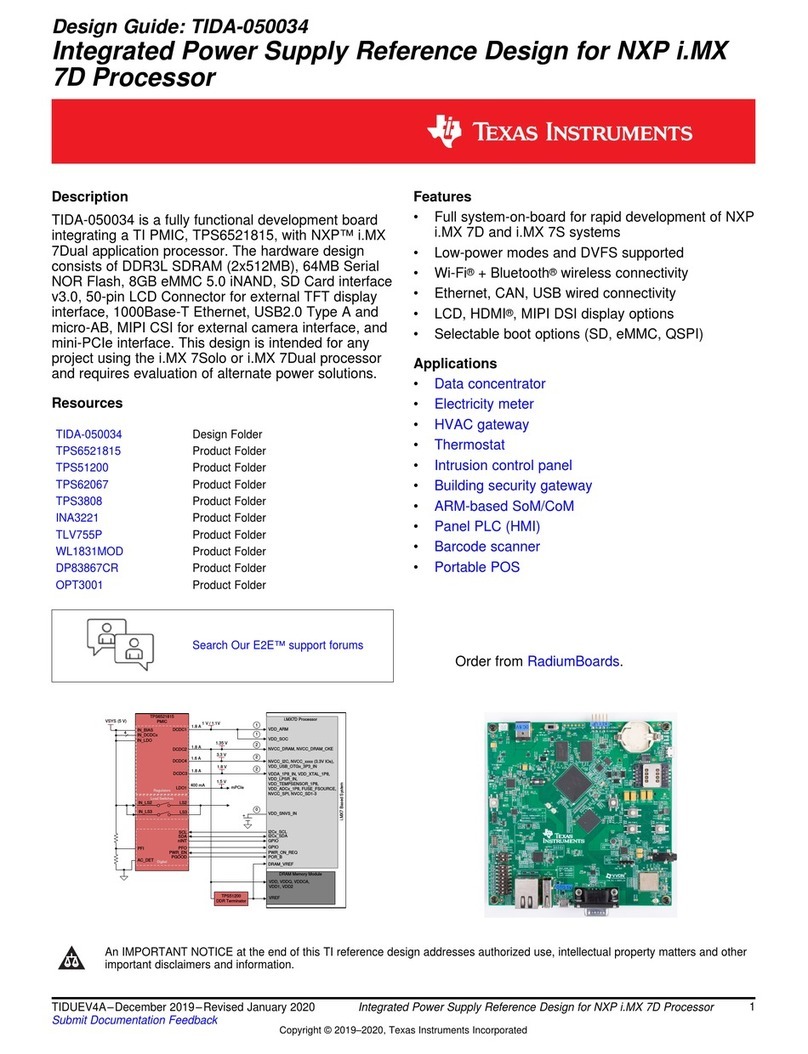

TIDA-050043 is first-and-foremost a reference design for powering the NXP i.MX 6ULL processor from the

TPS6521815 PMIC. To show that the PMIC can power the processor, it made the most sense to build a

data concentrator design that can also be used as a full evaluation kit (EVK) board with a variety of

peripheral devices to assist with development of various end equipments. As a result, there are a variety

of wired connections available, as well as multiple BOOT options. The end result of adding all the

peripherals, especially a 5-port USB hub, is that some external load switches have been added to provide

more voltage rails to deliver 5-V USB from the input to the USB hub. Finally, to ensure the entire board is

operational, we developed and tested software using the open-source embedded Linux Yocto SDK to get

started working with this design.

1.1 Key System Specifications

Table 1. Key System Specifications

PARAMETER SPECIFICATIONS DETAILS

Processor i.MX 6ULL, ARM Cortex-A7 Applications Processor,

MCIMX6Y2CVM08AB Section 2.2.1

PMIC TPS6521815 user-programmable PMIC with automatic sequencing and

DVFS Section 2.3.1

Memory 4-Gb DDR3L (512 MB), 256-Mb QSPI NOR-Flash (32 MB), 8GB

eMMC 5.0, SD v3.0 interface Section 2.2.2

Ethernet Dual-port ethernet interface - TI DP83849I PHY and 0845-2R1T-E4

RJ45 jack from Bel Fuse Section 2.3.2

Debug method (USB-to-UART) FTDI FT230X is required to implement USB to serial UART conversion Section 2.2.3

USB ports 5x USB Type-A ports (USB2517I-JZX hub IC) and 1x micro-AB port for

USB OTG (Amphenol 10104111-0001LF) Section 2.2.4

LCD display RGB TFT 40-pin connector (Molex 54132-4062) for LCD display

(Newhaven Display NHD-2.4-240320CF-CTXI#-F), compatible with

touch-screen controller (TI TSC2046IPWR) Section 2.2.5

JTAG header JTAG connection to i.MX 6ULL processor with 50-mil pitch, 10-pin

header Section 2.2.6

USB2ANY header Debug method for PMIC separate from processor I2C bus. Provided by

USB2ANY (standard 100-mil pitch, 10-pin header) Section 2.2.7

Current monitoring 2x TI INA3221 devices are used to monitor current through 6 rails in

the system Section 2.3.3

Operation with Coin Cell Coin cell for i.MX 6ULL SNVS input. Using DCDC6 of TPS6521815

PMIC, system always powers SNVS before full power-up sequence

begins.

Section 2.3.4

Tactile inputs, visual feedback Push-buttons and status LEDs connected to GPIOs of the processor to

assist with debugging software Section 2.2.8