www.ti.com

2SNLU233–October 2017

Submit Documentation Feedback

Copyright © 2017, Texas Instruments Incorporated

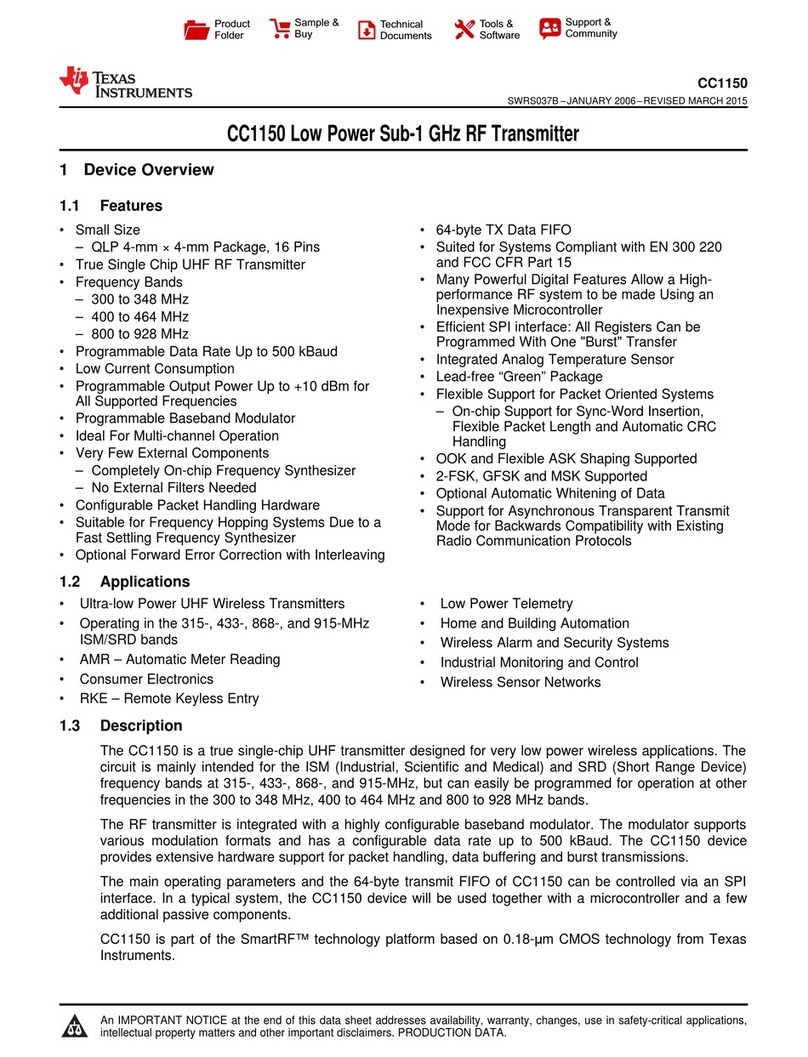

LVDS83BTSSOPEVM User’s Guide

Contents

1 Introduction ................................................................................................................... 3

2 LVDS83BTSSOPEVM Configuration...................................................................................... 3

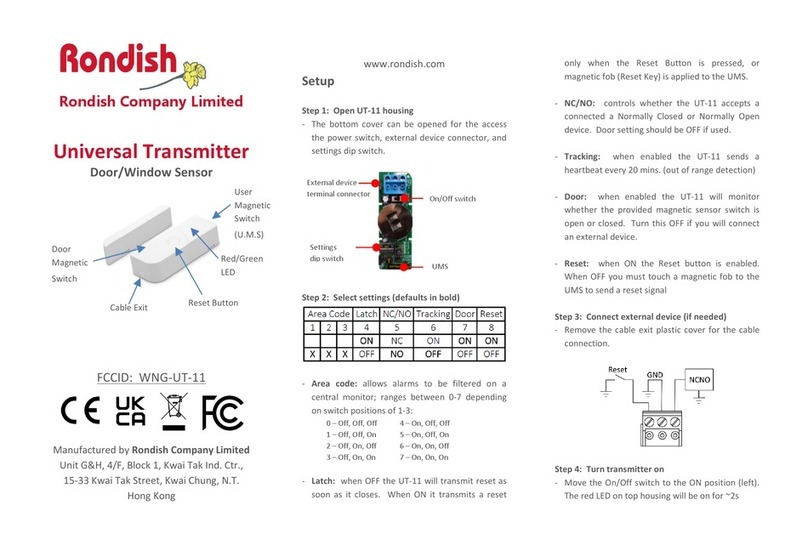

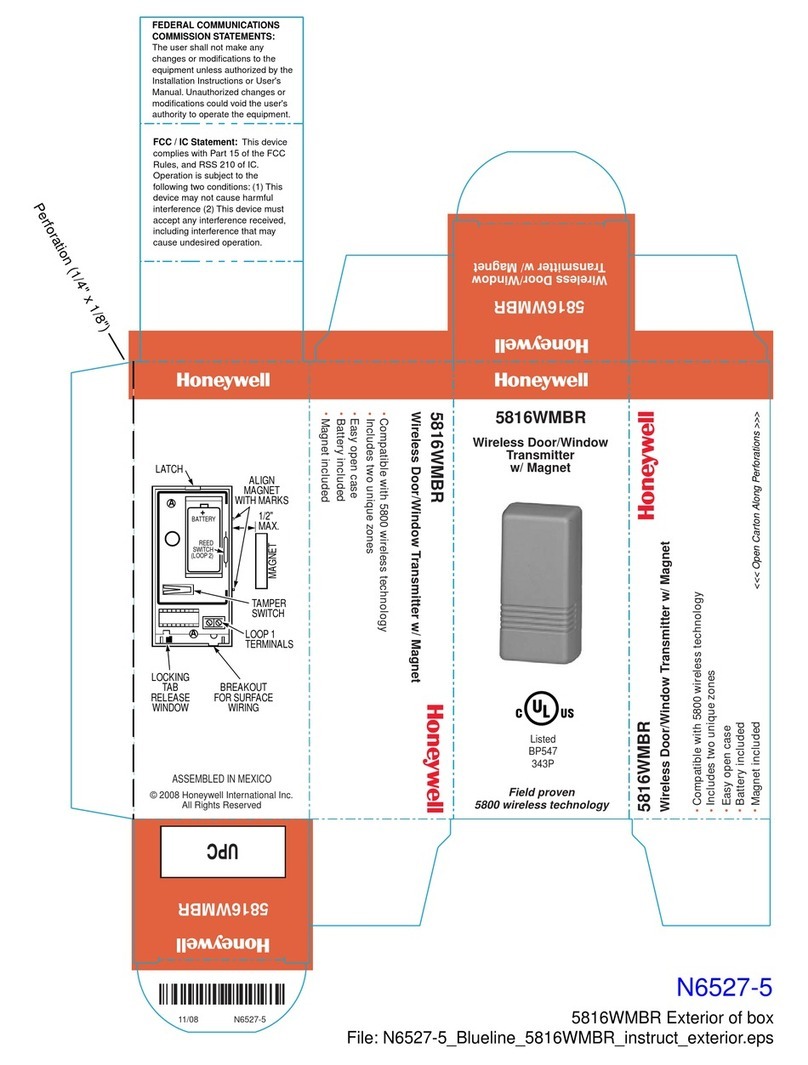

2.1 LVDS83BTSSOPEVM Kit Contents.............................................................................. 3

2.2 Description of EVM Board......................................................................................... 3

2.3 Power-Up Sequence ............................................................................................... 4

2.4 Signal Connectivity ................................................................................................. 5

3 PCB Construction .......................................................................................................... 10

3.1 LVDS83BTSSOPEVM Board Layout........................................................................... 10

4 LVDS83BTSSOPEVM Bill of Materials.................................................................................. 17

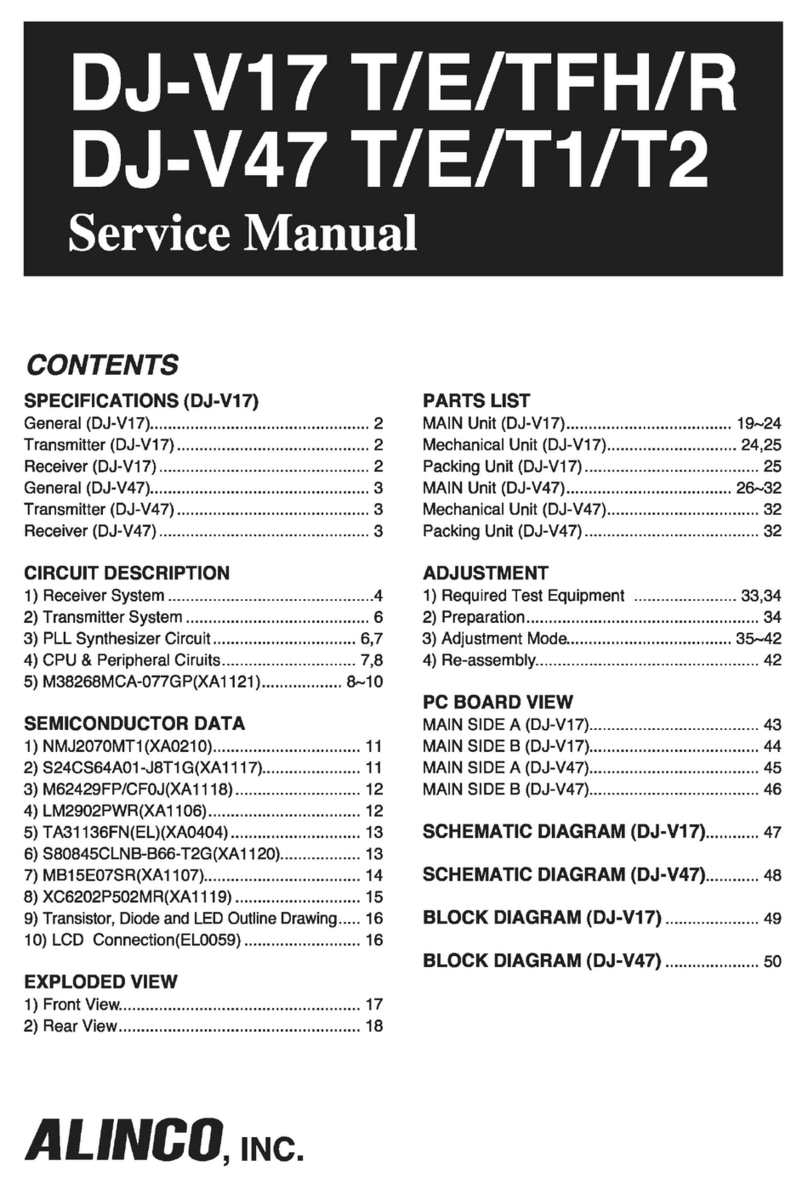

5 LVDS83BTSSOPEVM Schematics ...................................................................................... 18

List of Figures

1 LVDS83BTSSOPEVM ...................................................................................................... 3

2 Clock Rising Edge (High) Jumper Setting................................................................................ 4

3 Clock Falling Edge (Low) Jumper Setting................................................................................ 4

4 Active Shutdown/Clear Jumper Setting................................................................................... 4

5 24-Bit Color Host to 24-Bit LCD Panel Application With 2 MSB Transfer Over Fourth Data Channel .......... 6

6 24-Bit Color Host to 24-Bit LCD Panel Application With 2 LBS Transfer Over Fourth Data Channel............ 7

7 18-Bit Color Host to 18-Bit LCD Panel Application...................................................................... 8

8 12-Bit Color Host to 18-Bit LCD Panel Application...................................................................... 9

9 24-Bit Color Host to 18-Bit LCD Panel Application .................................................................... 10

10 LVDS83BTSSOPEVM Top Layer........................................................................................ 11

11 LVDS83BTSSOPEVM Layer 2 – GND.................................................................................. 12

12 LVDS83BTSSOPEVM Layer 3 – DUT GND............................................................................ 13

13 LVDS83BTSSOPEVM Layer 4 – VCC .................................................................................... 14

14 LVDS83BTSSOPEVM Layer 5 – GND.................................................................................. 15

15 LVDS83BTSSOPEVM Bottom Layer.................................................................................... 16

16 LVDS83BTSSOPEVM Schematics (1/3)................................................................................ 18

17 LVDS83BTSSOPEVM Schematics (2/3)................................................................................ 19

18 LVDS83BTSSOPEVM Schematic (3/3) ................................................................................. 20

List of Tables

1 BOM.......................................................................................................................... 17

Trademarks

FlatLink is a trademark of Texas Instruments.