LEA-M8F - Hardware Integration Manual

UBX-14000034 - R03 Early Production Information Contents

Page 3 of 30

Contents

Contents..............................................................................................................................3

1Hardware description ..................................................................................................5

1.1 Overview .............................................................................................................................................. 5

1.2 Architecture.......................................................................................................................................... 6

1.3 Pin description for LEA-M8F designs ..................................................................................................... 7

1.4 Connecting power................................................................................................................................ 8

1.4.1 VCC .............................................................................................................................................. 8

1.4.2 V_BCKP......................................................................................................................................... 8

1.4.3 VCC_RF......................................................................................................................................... 8

1.5 Interfaces.............................................................................................................................................. 8

1.5.1 UART............................................................................................................................................. 8

1.5.2 USB ............................................................................................................................................... 8

1.5.3 Display Data Channel (DDC) .......................................................................................................... 9

1.5.4 SPI................................................................................................................................................. 9

1.5.5 DDC interface for External DAC Control...................................................................................... 10

1.6 I/O and Control Pins............................................................................................................................ 10

1.6.1 RESET_N...................................................................................................................................... 10

1.6.2 D_SEL.......................................................................................................................................... 10

1.6.3 FREQ_PHASE_IN0 / EXINT0, FREQ_PHASE_IN1 / EXTINT1............................................................. 11

1.6.4 REF_FREQ_OUT ........................................................................................................................... 11

1.6.5 TIMEPULSE / TP2 ......................................................................................................................... 11

1.7 Device Configuration.......................................................................................................................... 11

2Design .........................................................................................................................12

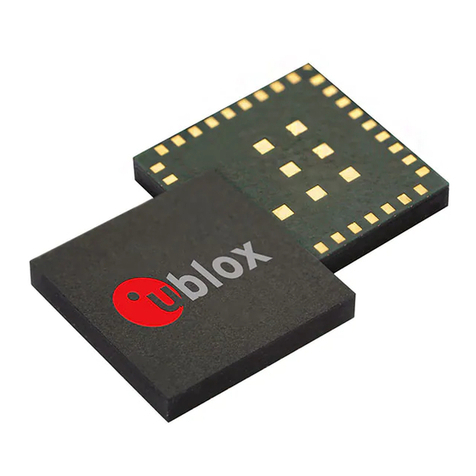

2.1 Layout: Footprint and paste mask ....................................................................................................... 12

2.1.1 Placement ................................................................................................................................... 12

2.1.2 Antenna connection and ground plane design ............................................................................ 13

2.1.3 Antenna micro strip connection................................................................................................... 15

2.2 GNSS Antenna Connection................................................................................................................. 16

2.2.1Passive Antenna Connection ....................................................................................................... 16

2.2.2 Active antenna connection .......................................................................................................... 17

3Migration to u-blox M8 modules ..............................................................................18

3.1 Software migration............................................................................................................................. 18

3.2 Hardware migration LEA-6T -> LEA-M8F ............................................................................................ 18

Supply Voltage .................................................................................................................19

4Product handling ........................................................................................................20

4.1 Packaging, shipping, storage and moisture preconditioning ............................................................... 20

4.2 Soldering ............................................................................................................................................ 20