NEO-D9C-Integration manual

Contents

1 Integration manual overview............................................................................................. 5

2 System description...............................................................................................................6

2.1 Overview.................................................................................................................................................... 6

2.1.1 QZSS L6 augmentation service.................................................................................................. 6

2.2 Architecture..............................................................................................................................................8

2.2.1 Block diagram..................................................................................................................................8

3 Receiver functionality.......................................................................................................... 9

3.1 Receiver configuration........................................................................................................................... 9

3.1.1 Changing the receiver configuration..........................................................................................9

3.1.2 Default QZSS configuration.........................................................................................................9

3.1.3 Default interface settings............................................................................................................ 9

3.1.4 Basic receiver configuration...................................................................................................... 10

3.1.5 QZSS L6 satellite and message selection..............................................................................10

3.1.6 QZSS L6 data message output................................................................................................ 13

3.2 Communication interfaces................................................................................................................. 14

3.2.1 UART............................................................................................................................................... 15

3.2.2 I2C interface..................................................................................................................................16

3.2.3 SPI interface..................................................................................................................................19

3.2.4 USB interface................................................................................................................................20

3.3 Predefined PIOs.....................................................................................................................................21

3.3.1 D_SEL..............................................................................................................................................21

3.3.2 RESET_N........................................................................................................................................ 21

3.3.3 SAFEBOOT_N................................................................................................................................21

3.3.4 Extended TX timeout.................................................................................................................. 22

3.4 Security................................................................................................................................................... 22

3.4.1 Receiver status monitoring....................................................................................................... 22

3.5 Forcing a receiver reset....................................................................................................................... 22

3.6 Firmware upload....................................................................................................................................22

4 Design..................................................................................................................................... 24

4.1 Pin assignment......................................................................................................................................24

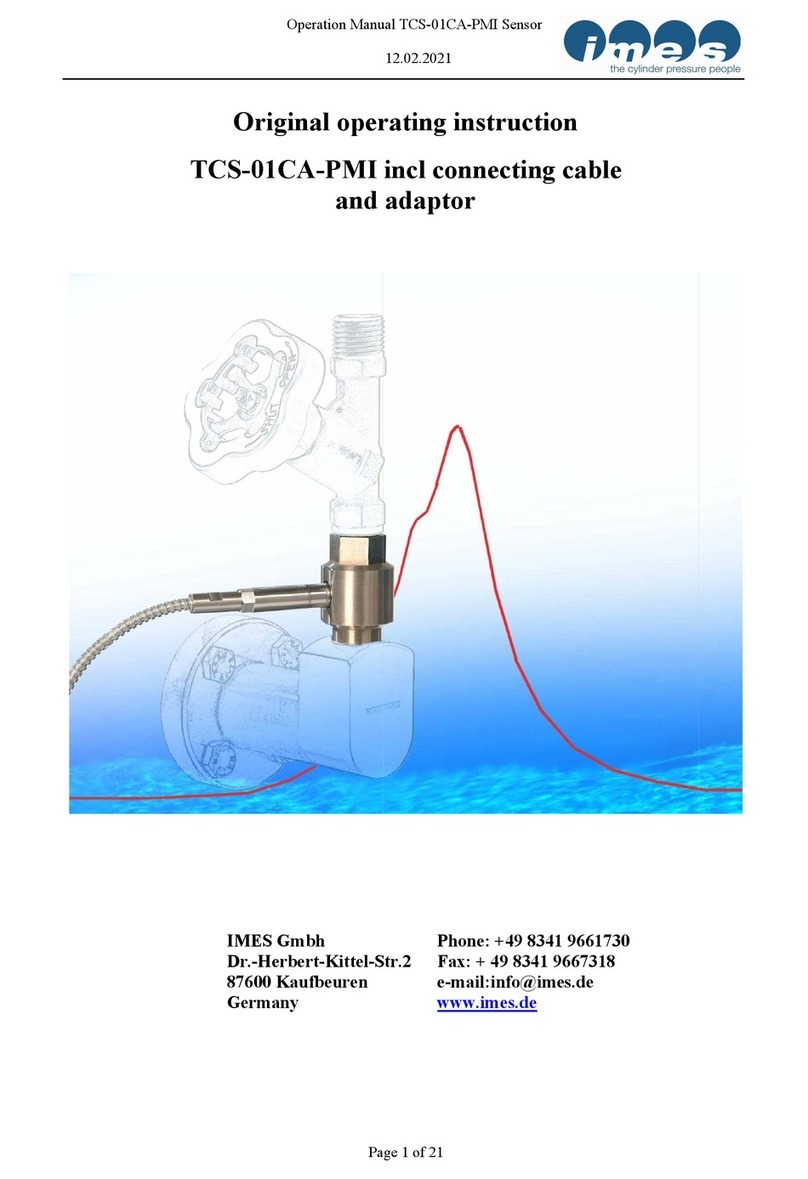

4.2 Antenna...................................................................................................................................................25

4.2.1 Antenna bias................................................................................................................................. 27

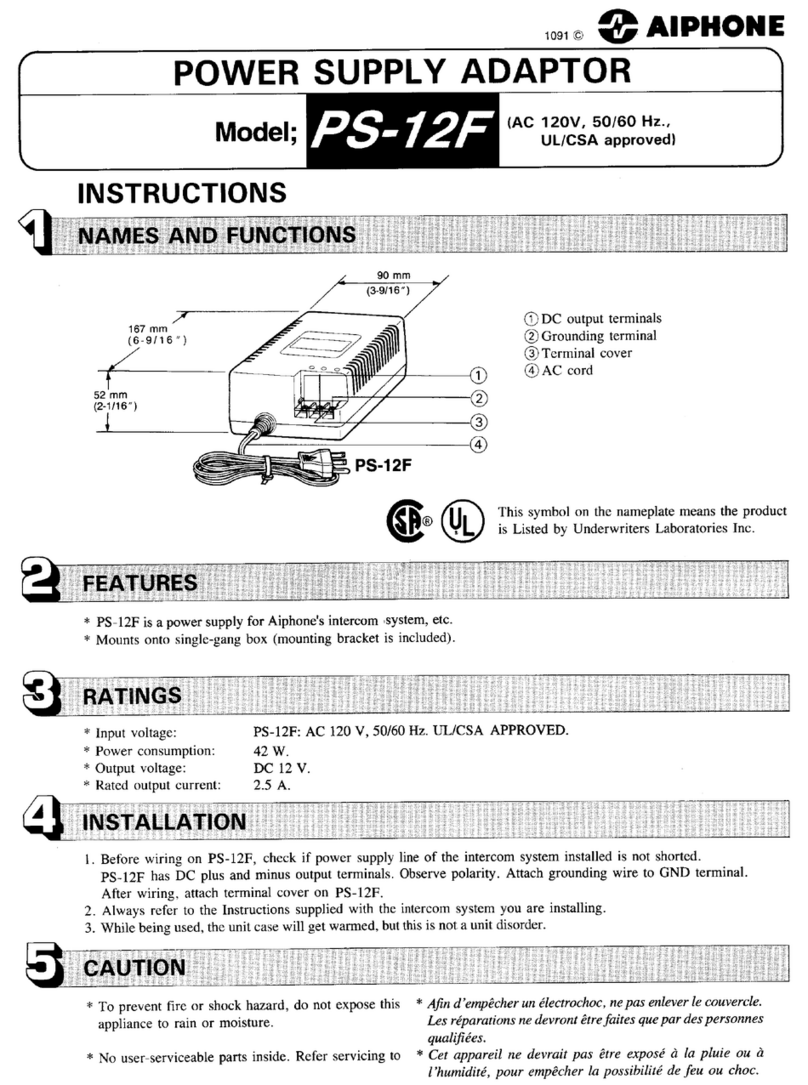

4.3 Power supply..........................................................................................................................................30

4.3.1 VCC: Main supply voltage.......................................................................................................... 30

4.3.2 NEO-D9C power supply.............................................................................................................. 30

4.4 NEO-D9C minimal design................................................................................................................... 30

4.5 EOS/ESD precautions.......................................................................................................................... 31

4.5.1 ESD protection measures.......................................................................................................... 31

4.5.2 EOS precautions...........................................................................................................................32

4.5.3 Safety precautions...................................................................................................................... 32

4.6 Electromagnetic interference on I/O lines.......................................................................................32

4.6.1 General notes on interference issues......................................................................................33

4.6.2 In-band interference mitigation................................................................................................33

4.6.3 Out-of-band interference........................................................................................................... 34

UBX-21031631 - R02

Contents Page 3 of 53

C1-Public