Chip Component Information

Replacing

Chip Components

Chip components are installed at the

fac-

tory

by a series of robots. The first one

places

a small spot of adhesive

resin

at the location

where each part is to be installed, and later

robots handle and place

Parts

using vacuum

suction.

For

Single

sided boards, solder Paste is

ap-

plied and the board is then baked to harden

the resin and flow the solder. For double sided

boards, no solder Paste is applied, but the

board is baked (or exposed to ultra-violet

light) to

eure

the resin before dip soldering.

In our laboratories and Service shops, small

quantities of chip components are mounted

manually by applying a spot of resin, placing

with tweezers, and then soldering by very

small dual streams of hot air (without physi-

cal contact during soldering). We remove

Parts by first removing

solder

using a vacuum

suction iron, which applies a light steady

vac-

uum at the iron tip, and then breaking the

adhesive with tweezers.

The special vacuum/desoldering equip-

ment is recommended if you expect to do a lot

of

Chip

replacements. Otherwise, it is usually

possible to remove and replace

Chip

compo-

nents with only a tapered, temperature-con-

trolled soldering iron, a set of tweezers and

braided

topper

solder

wick.

Soldering iron

temperature should be below 280” C

(536”

F).

Precautions

for

Chip

Replacement

DO not disconnect a

Chip

forcefully,

or the

foil Pattern may peel off the board.

Never re-use a

Chip

component. Dispose of

all removed

chip

components immediately to

avoid mixing with new

Parts.

Limit soldering time to 3 seconds or less to

avoid damaging the component and board.

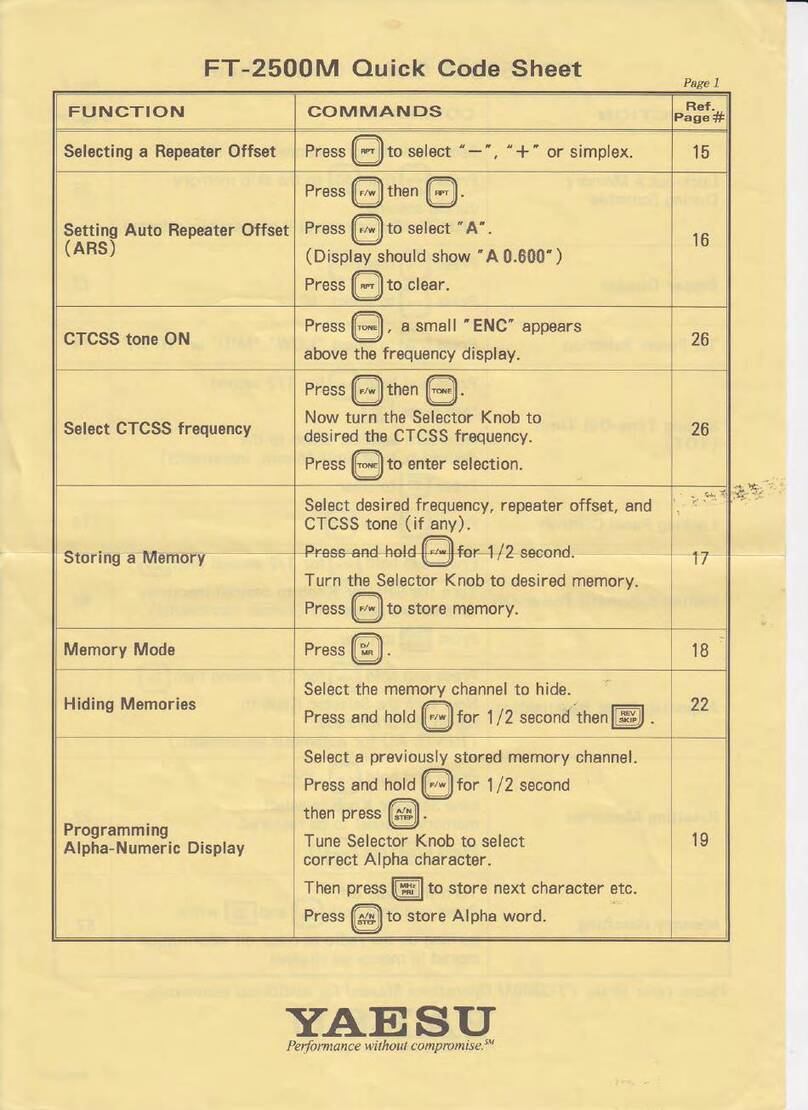

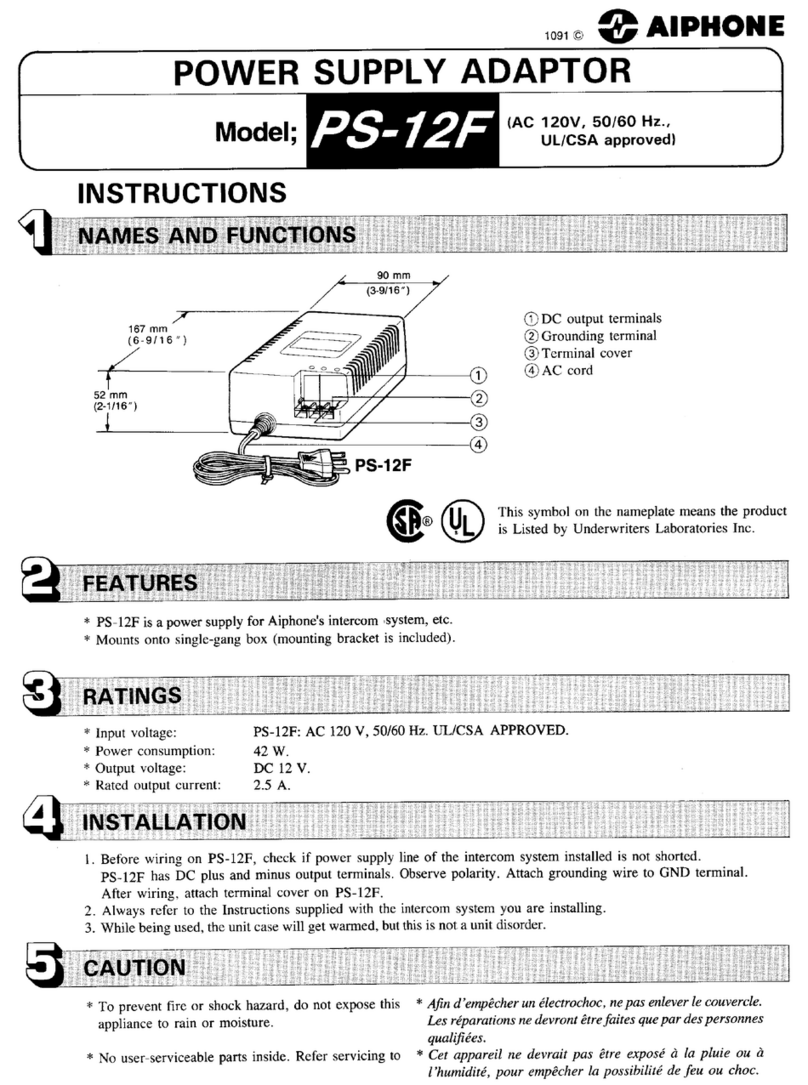

Removing Chip Components

Cl

Remove the

solder

at

each

joint, one joint at a

time, using

solder

wick

whetted with

non-

acidic fluxes as shown below. Avoid applying

pressure, and do not attempt to remove

tin-

ning

from

the

chip’s

electrode.

0

Grasp the

chip

on both sides with tweezers,

and gently twist the tweezers back and forth

(to break the adhesive bond) while

alter-

nately heating

each

electrode.

Be careful to

avoid peeling the foil

traces

from the board.

Dispose of the

chip

when removed.

0

After removing the

Chip,

use the topper braid

and soldering iron to

wick

away any excess

solder

and smooth the land for installation of

the replacement part.

FREI

00

Techmkd

Supplement