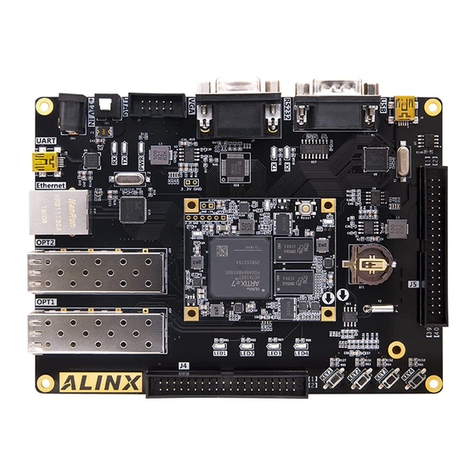

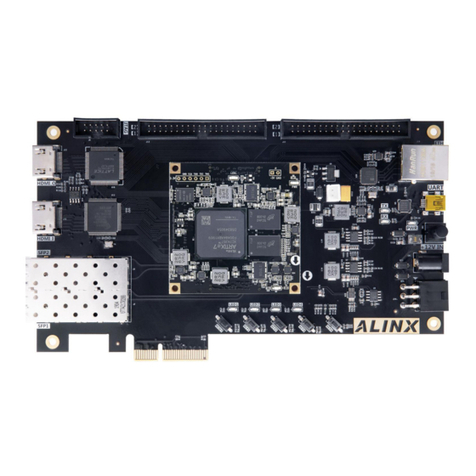

Alinx KINTEX-7FPGA User manual

Other Alinx Computer Hardware manuals

Alinx

Alinx AXU15EGB User manual

Alinx

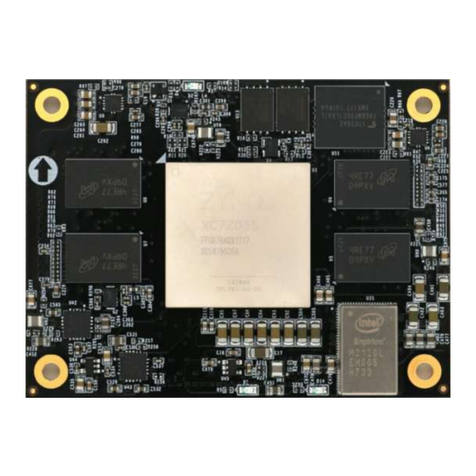

Alinx ACU4EV User manual

Alinx

Alinx ZYNQ AC7Z035 User manual

Alinx

Alinx AN9134 User manual

Alinx

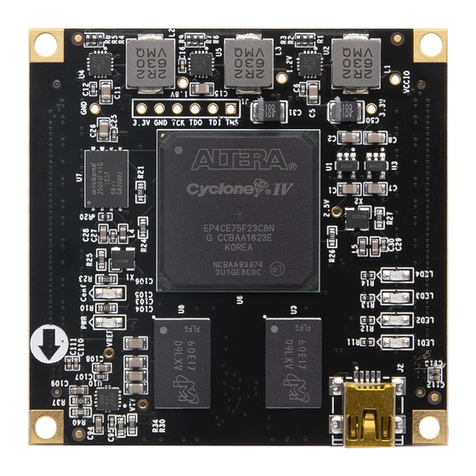

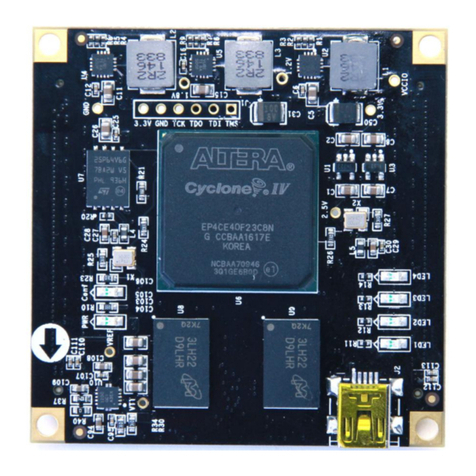

Alinx ALTER AC4075 User manual

Alinx

Alinx AV6045 User manual

Alinx

Alinx ARTIX-7 FPGA User manual

Alinx

Alinx FL1010 User manual

Alinx

Alinx ALTERA AC4040 User manual

Alinx

Alinx KINTEX UltraScale AXKU062 User manual

Popular Computer Hardware manuals by other brands

Toshiba

Toshiba TOSVERT VF-MB1/S15 IPE002Z Function manual

Shenzhen

Shenzhen MEITRACK MVT380 user guide

TRENDnet

TRENDnet TEW-601PC - SUPER G MIMO WRLS PC CARD user guide

StarTech.com

StarTech.com CF2IDE18 instruction manual

Texas Instruments

Texas Instruments LMH0318 Programmer's guide

Gateway

Gateway 8510946 user guide

Sierra Wireless

Sierra Wireless Sierra Wireless AirCard 890 quick start guide

Leadtek

Leadtek Killer Xeno Pro Quick installation guide

Star Cooperation

Star Cooperation FlexTiny 3 Series Instructions for use

Hotone

Hotone Ampero user manual

Connect Tech

Connect Tech Xtreme/104-Express user manual

Yealink

Yealink WF50 user guide