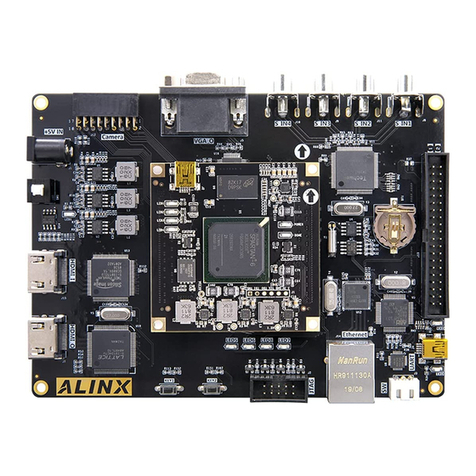

ZYNQ Ultrascale + FPGA Board AXU4EV-P User Manual

Table of Contents

Version Record.......................................................................................... 2

Part 1: FPGA Development Board Introduction......................................... 6

Part 2: ACU4EV core board......................................................................11

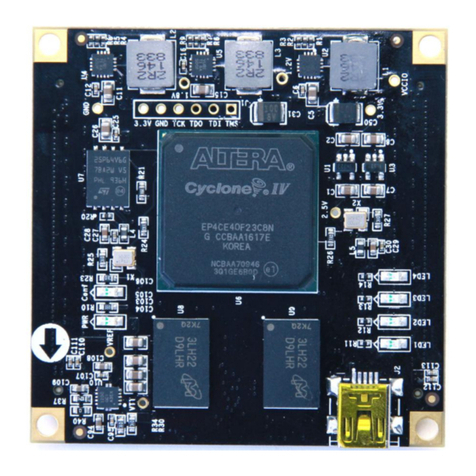

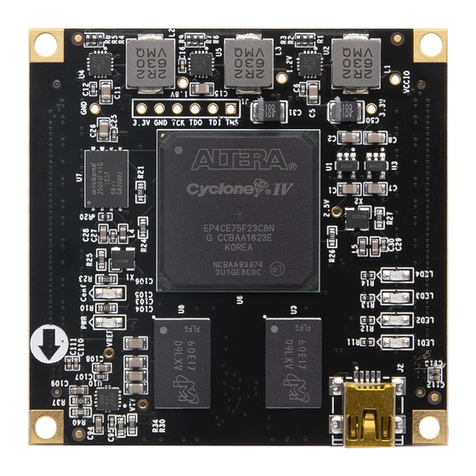

Part 2.1: ACU4EV Core Board Introduction ......................................11

Part 2.2: ZYNQ Chip ........................................................................ 12

Part 2.3: DDR4 DRAM ..................................................................... 14

Part 2.4: QSPI Flash ........................................................................ 21

Part 2.5: eMMC Flash ...................................................................... 22

Part 2.6: Clock Configuration ........................................................... 24

Part 2.7: LED.................................................................................... 26

Part 2.8: Power Supply..................................................................... 27

Part 2.9: ACU4EV Core Board Size Dimension ............................... 29

Part 2.10: Board to Board Connectors Pin Assignment ................... 29

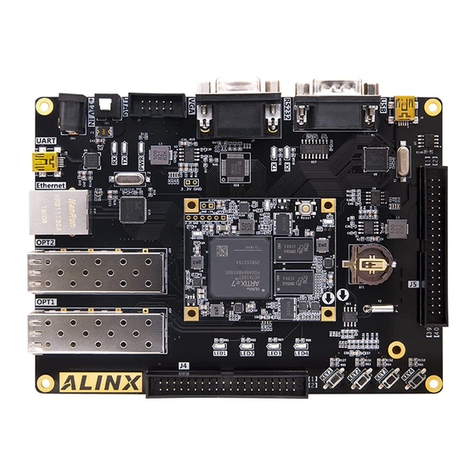

Part 3: Carrier Board ............................................................................... 38

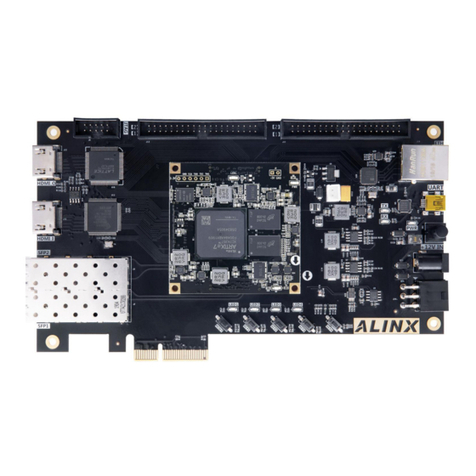

Part 3.1: Carrier Board Introduction ................................................. 38

Part 3.2: M.2 Interface...................................................................... 38

Part 3.3: DP Interface....................................................................... 39

Part 3.4: USB3.0 Interface ............................................................... 41

Part 3.5: Gigabit Ethernet Interface.................................................. 42

Part 3.6: USB to Serial Port.............................................................. 44

Part 3.7: SD Card Slot Interface....................................................... 45

Part 3.8: HDMI Output Interface....................................................... 46

Part 3.9: HDMI Input Interface.......................................................... 48

Part 3.10: SFP Interface................................................................... 50

Part 3.11: PCIe Slot.......................................................................... 52

Part 3.12: CAN Communication Interface........................................ 53

Part 3.13: 485 Communication Interface.......................................... 54