FPGA Video Processing Development Platform AV6150 User Manual

Table of Contents

Version Record.......................................................................................... 2

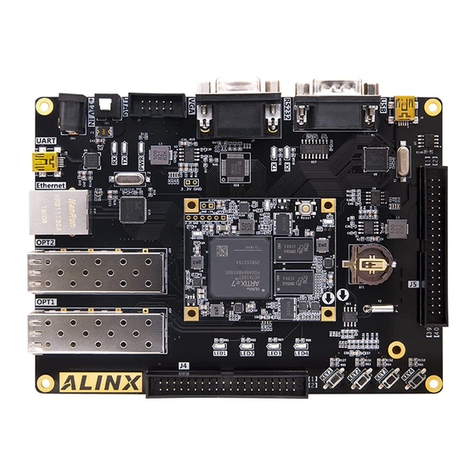

Part 1: FPGA Development Board Introduction......................................... 6

Part 2: Function realization........................................................................ 8

Part 2.1: Video Input............................................................................8

Part 2.2: Video Output.......................................................................11

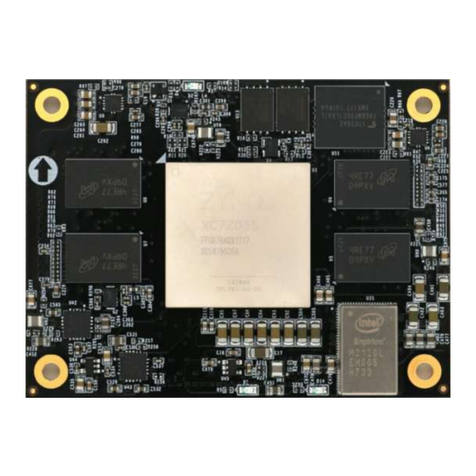

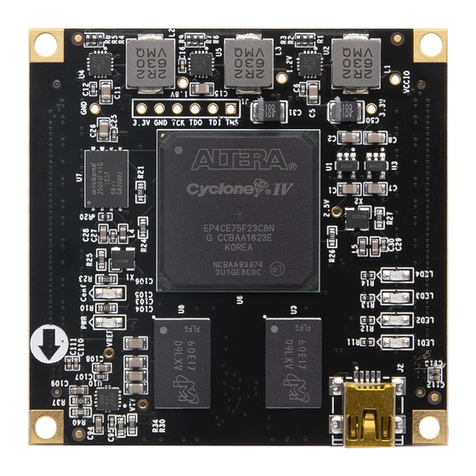

Part 3: AC6150 core board...................................................................... 12

Part 3.1: AC6150 Core Board Introduction........................................13

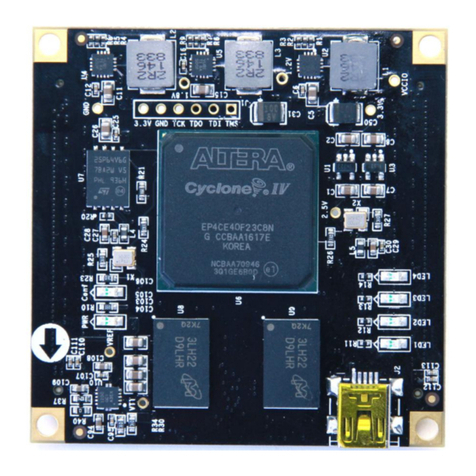

Part 3.2: FPGA..................................................................................13

Part 3.3: DDR3 DRAM ......................................................................15

Part 3.4: SPI Flash ............................................................................17

Part 3.5: Crystal oscillator on Core Board .........................................19

Part 3.6: LED Light on Core Board....................................................20

Part 3.7: AV6150 Power Supply ........................................................22

Part 3.8: Powe interface on Core Board............................................24

Part 3.9: Expansion Ports..................................................................25

Part 3.10: Structure Diagram.............................................................29

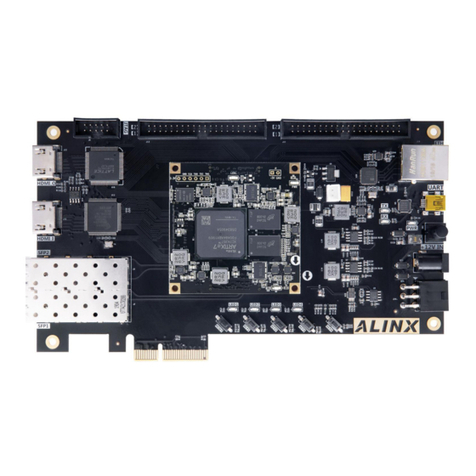

Part 4: Carrier board.................................................................................30

Part 4.1: Carrier boardIntroduction....................................................30

Part 4.2: VGA Display Interface.........................................................31

Part 4.3: HDMI Output Interface........................................................33

Part 4.4: HDMI Input Interface...........................................................35

Part 4.5: Video input interface...........................................................37

Part 4.6: Gigabit Ethernet Interface...................................................39

Part 4.7: ARM Controller ...................................................................42

Part 4.8: Camera Module Interface ...................................................49

Part 4.9: Expansion Header ..............................................................50