KINTEX UltraScale+ FPGA Board AXKU062 User Manual

http://www.alinx.com.cn

3/51

Table of Contents

Version Record.................................................................................................................................2

Table of Contents............................................................................................................................3

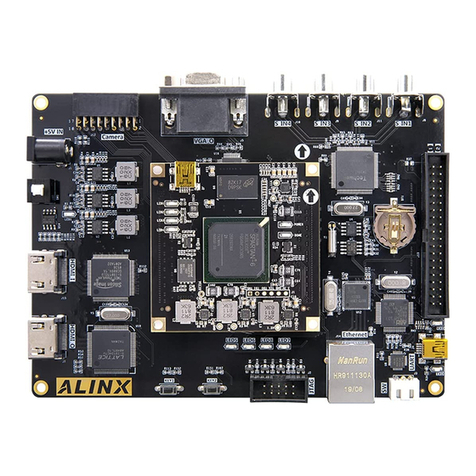

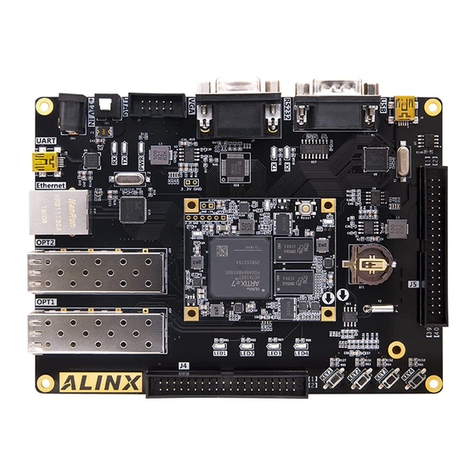

Part 1 AXKU062 Development Board......................................................................................7

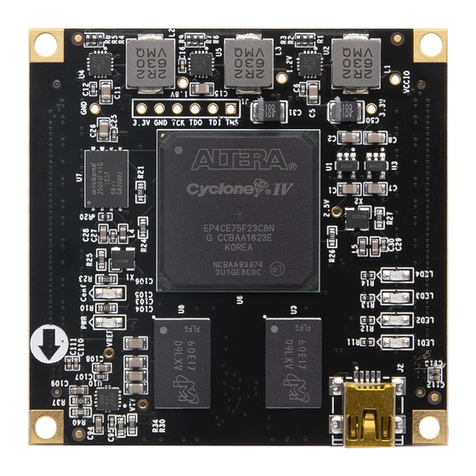

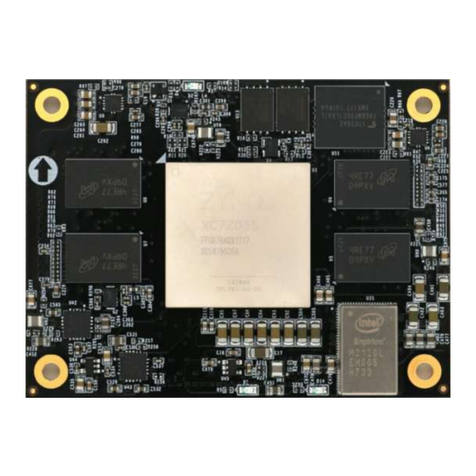

Part 1.1: FPGA Development Board Introduction.......................................................7

Part 1.2: FPGA Chip................................................................................................................8

Part 1.3: DDR4 DRAM ........................................................................................................... 9

Part 1.4: QSPI Flash..............................................................................................................13

Part 1.5: Clock configuration........................................................................................... 15

Part 1.6: LED Light................................................................................................................15

Part 1.7: Power Supply....................................................................................................... 16

Part 1.8: Size Dimension....................................................................................................18

Part 1.9: Board to Board Connectors pin assignment............................................18

Part 2: Carrier Board....................................................................................................................28

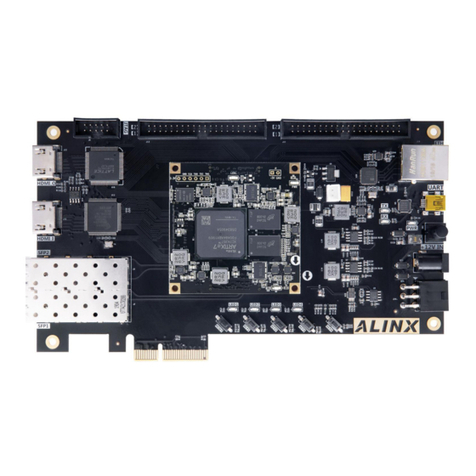

Part 2.1: Introduction..........................................................................................................28

Part 2.2: PCIE X8 interface................................................................................................ 29

Part 2.3: SFP+ Optical fiber interface ........................................................................... 30

Part 2.4: Gigabit Ethernet Interface ...............................................................................32

Part 2.5: USB to Serial Port............................................................................................... 33

Part 2.6: FMC Expansion Port.......................................................................................... 34

Part 2.7: SD Card Slot......................................................................................................... 44

Part 2.8: SMA Interface...................................................................................................... 45

Part 2.9: Temperature Sensor and EEPROM...............................................................45

Part 2.10: LED Light............................................................................................................. 46

Part 2.11: Keys.......................................................................................................................48

Part 2.12: JTAG Interface................................................................................................... 49

Part 2.13: Power Supply.....................................................................................................49

Part 2.14: Fan......................................................................................................................... 50

Part 2.15:Size Dimension...................................................................................................51