ARTIX-7 FPGA Development Board AX7103 User Manual

Table of Contents

Version Record.......................................................................................................2

Part 1: FPGA Development Board Introduction............................................... 6

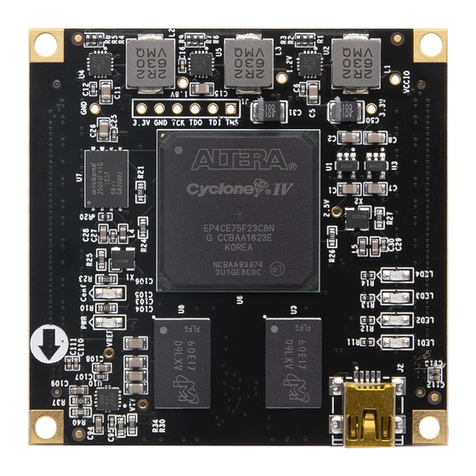

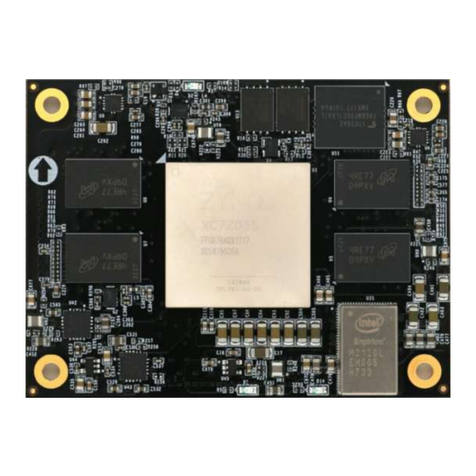

Part 2: AC7100B core board................................................................................9

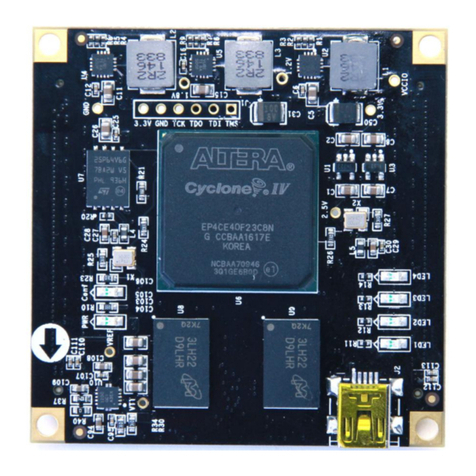

Part 2.1: AC7100B Core Board Introduction............................................ 9

Part 2.2: FPGA Chip....................................................................................11

Part 2.3: Active Differential Crystal...........................................................12

Part 2.4: DDR3 DRAM............................................................................... 15

Part 2.5: QSPI Flash...................................................................................17

Part 2.6: LED Light on Core Board.......................................................... 19

Part 2.7: Reset key......................................................................................19

Part 2.8: JTAG Interface.............................................................................20

Part 2.9: Power Interface on the Core Board.........................................21

Part 2.10: Board to Board Connectors pin assignment........................22

Part 2.11: Power Supply.............................................................................29

Part 2.12: Structure Diagram.................................................................... 31

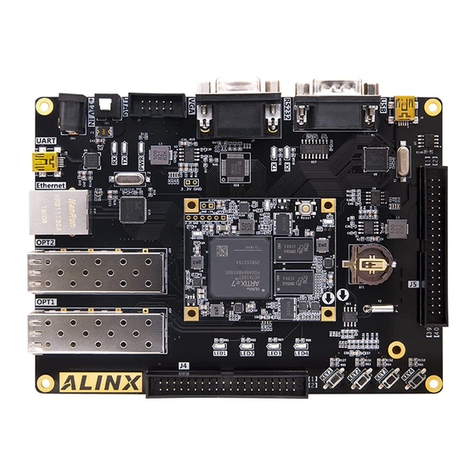

Part 3: Carrier board........................................................................................... 32

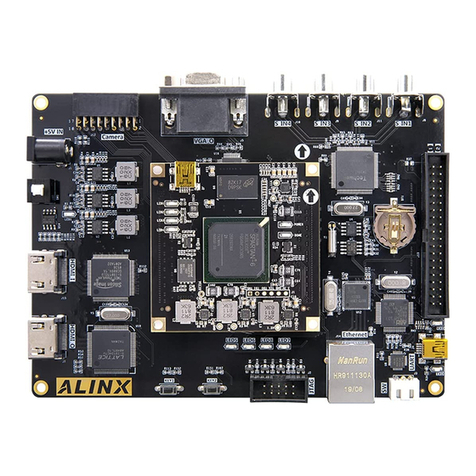

Part 3.1: Carrier board Introduction......................................................... 32

Part 3.2: Gigabit Ethernet Interface......................................................... 33

Part 3.3: PCIe x4 Interface........................................................................ 36

Part 3.4: HDMI output interface................................................................ 38

Part 3.5: HDMI Input interface.................................................................. 40

Part 3.6: SD Card Slot................................................................................42

Part 3.7: USB to Serial Port.......................................................................43

Part 3.8: EEPROM 24LC04.......................................................................45

Part 3.9: Expansion Header...................................................................... 46

Part 3.10: JTAG Interface.......................................................................... 49

Part 3.11: XADC interface (not installed by default)............................. 50