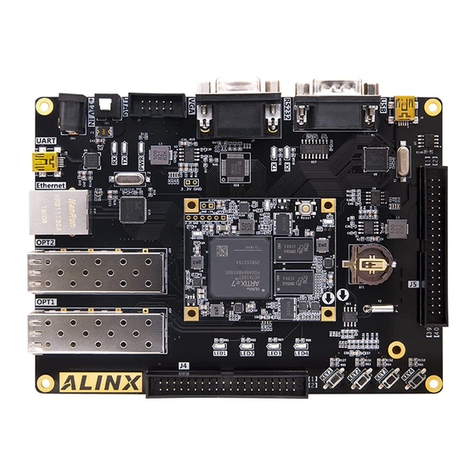

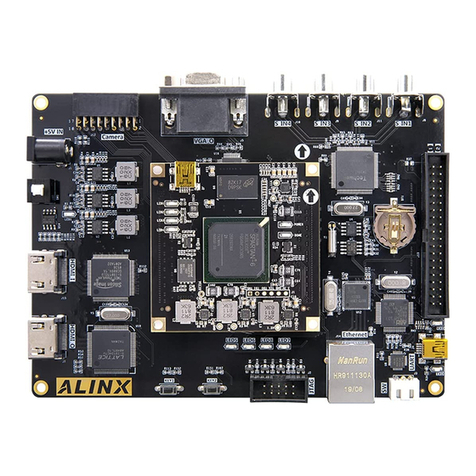

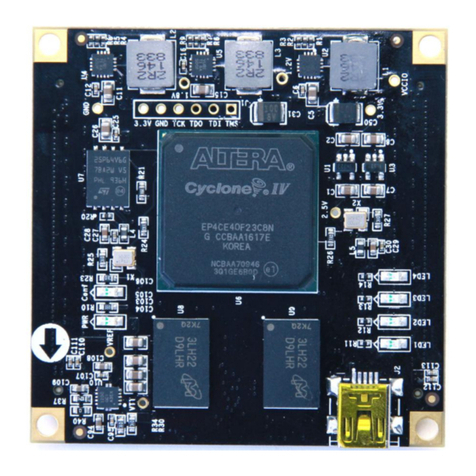

ZYNQ FPGA Development Board AX7020 User Manual

Table of Contents

Version Record...................................................................................................... 2

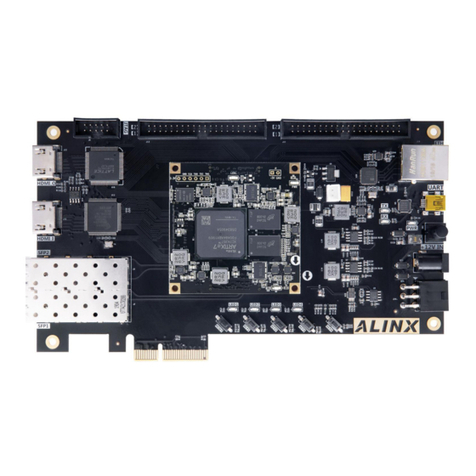

Part 1: FPGA Development Board Introduction................................................6

Part 2: Dimensional structure...............................................................................8

Part 3: Power Supply.............................................................................................9

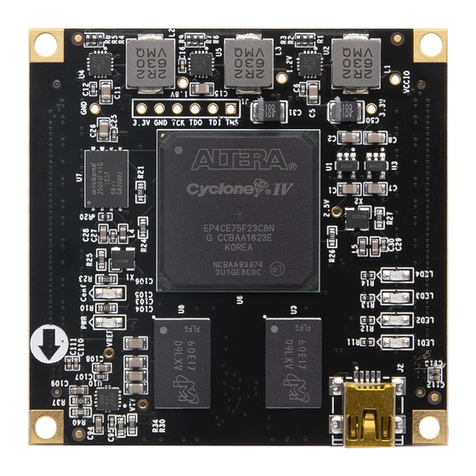

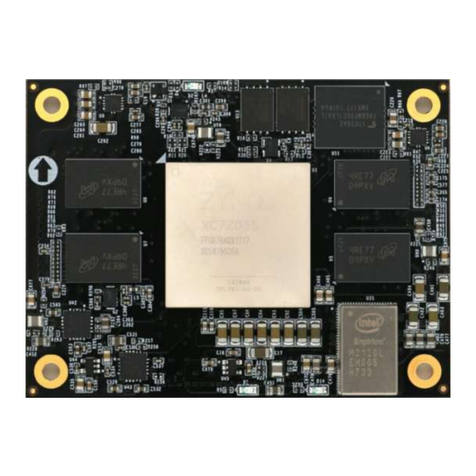

Part 4: ZYNQ Chip...............................................................................................12

Part 4.1: JTAG Interface............................................................................. 14

Part 4.2: FPGA Power System..................................................................15

Part 4.3: ZYNQ boot configuration........................................................... 16

Part 5: Clock Configuration................................................................................ 17

Part 5.1: PS system clock source............................................................. 17

Part 5.2: PL system clock source..............................................................18

Part 6:ZYNQ Processor System (PS) peripherals......................................19

Part 6.1: QSPI Flash................................................................................... 19

Part 6.2: DDR3 DRAM................................................................................21

Part 6.3: Gigabit Ethernet Interface..........................................................24

Part 6.4: USB2.0 Interface......................................................................... 27

Part 6.5: USB to Serial Port....................................................................... 29

Part 6.6: SD Card Slot................................................................................ 30

Part 6.7: PS PMOD connector.................................................................. 31

Part 6.8: User LEDs.................................................................................... 32

Part 6.9: User Buttons.................................................................................33

Part 7:ZYNQ Programmable Logic (PL) peripherals..................................34

Part 7.1: HDMI Interface.............................................................................34

Part 7.2: EEPROM 24LC04....................................................................... 37

Part 7.3: Real Time Clock DS1302...........................................................38