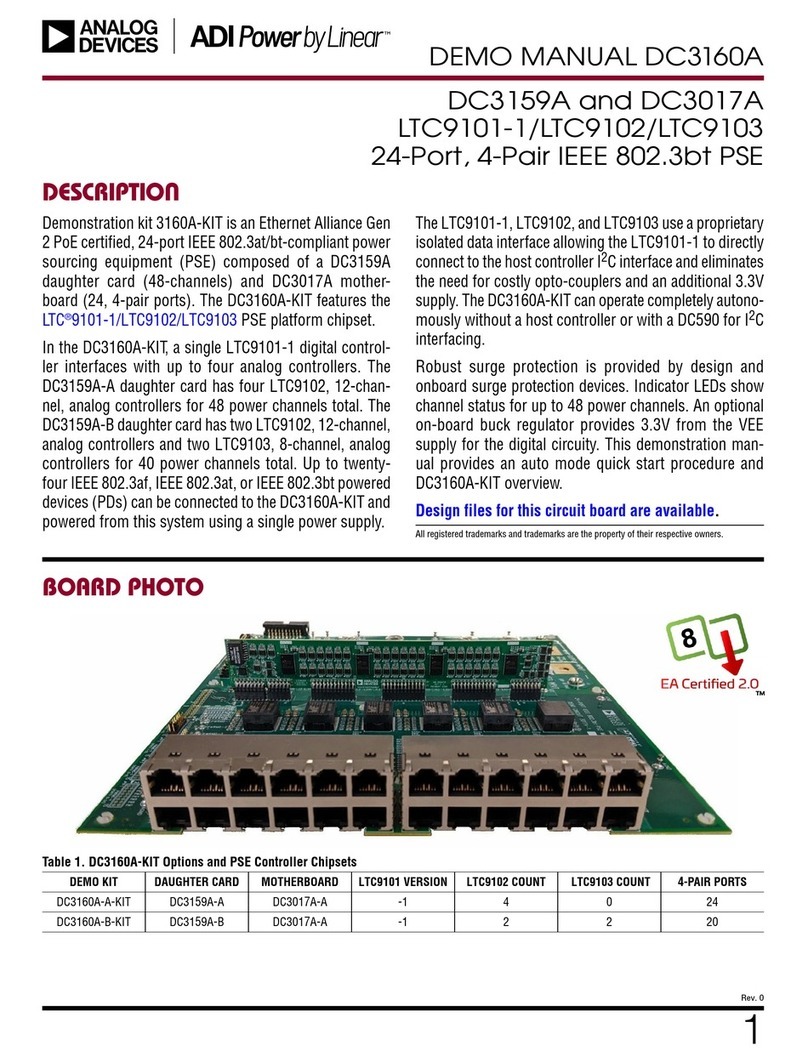

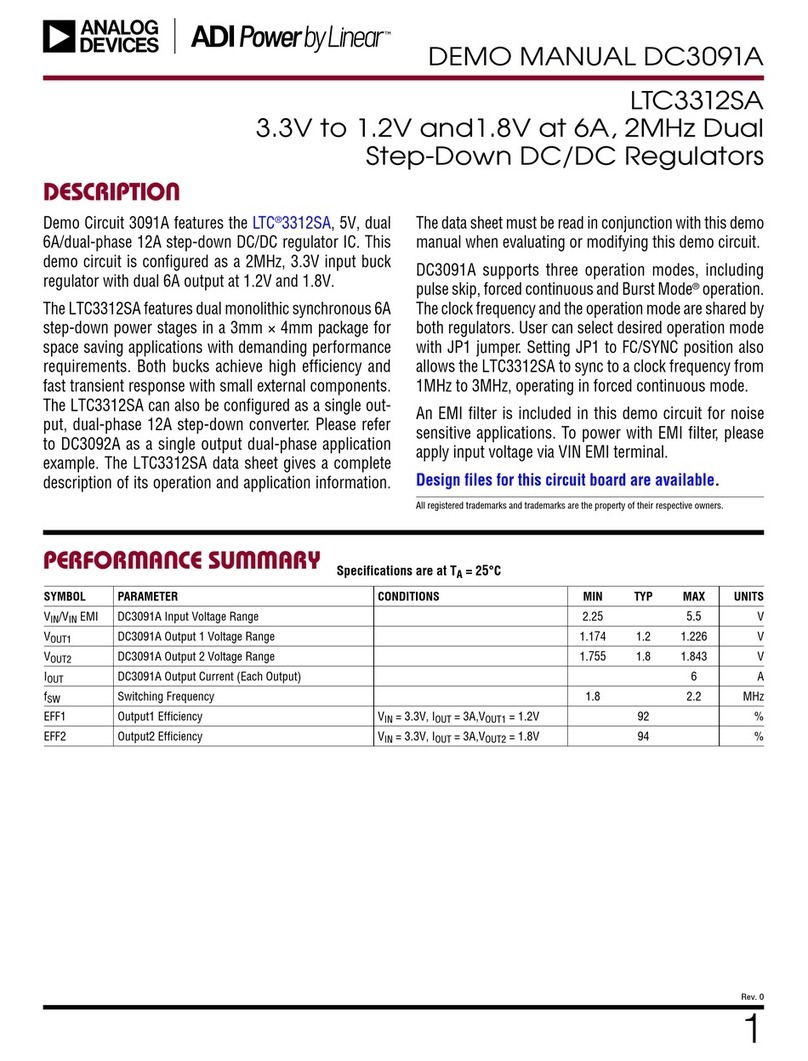

CHASSIS

ADDITIONAL JUMPERS ON CELL INPUTS 6/2/17 SABC

2.2UF AND 100NF PER VDD PIN

LOCAL GROUND

VSS

PLACE CLOSE TO TRANSFORMER

D_DWN_N AND DWN_P

CHASSIS

VSS

LOCAL GROUND

D_UP_N AND D_UP_P

100R DIFFERENTIAL PAIRS

200 200

* *

Transformer Isolated Config.

1

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

1KOHM AT 100MEGHZ

D_DWN_P

D_UP_ND_UP

D_DWN_P

D_DWN_N

BLK

CCM

VSS

D_DWN_N

MASTER

VREFGND1

D_UP_ND_UP

VSSVSS

VDD

VSS

VREFBUF

GPO1

GPO2

68PF 68PF

0

0

0

0

0

0

0

0

0.22UF

0.22UF

0

1K

51

3

2

ADR4525BRZ

4.99K

20

0

1UF

8

2

3

AD7284

6

1

4

3

2.2UF

2.2UF

2

1

4

0

7

6

5

0

4

1

2

4

5

5

6

7

8

1

3

60OHM

1UF

BAT54W T/R

10K 4.99K

TG110-E050N5LF

68PF

0

1803280

1UF

1000PF

0

8

1000PF

68PF

1K

TG110-E050N5LF

51

SML-211UTT86

7

TSW-101-08-F-D

VREG5

SML-211UTT86

BAT54W T/R

4.99K

VREG5 LED

TSW-101-08-F-D

1UF

SML-211UTT86

BZG03C43-TR

22-28-4033

LQFP64_SKTPPE20X20HOLDER_ALT

4

C

NTS

-

-

S. Bradshaw

AD7284

-

P1

R115

R116

R30

R114

C79 C80

C78

R112

R113

P8

P9

C19C17

R12

R11

R19

R98

C67C66

R99

TP66

C76

R101R100

R15

T1

T1

R85

C14

TP67TP21

P3

TP70

TP69

TP68

TP50

R89

C75C74

C73

U10

DS1

R8

R9 DS2

DS13

R16

TP65

TP64

TP63

TP62TP61

R21 R20

CR7

CR6

R22

D5 R87

R86

R18

R17

R83

C64

C65

C63C62

C12

R24

R27

C9

U1

R109

P4

TP3TP2

TP9

R5

TP1

TP4 C2

C1

E2

C3

TP5

R1

E1

C8

C7C5

C4

CR3

C6

TP8

C13

TP11

TP14

CR4

VREG5

VSS

VSS

VREG5 VSS

DUPND_UP_N

D_UP_P

SDO DDWNN

VSS

VSS

VSS

VSS

SDI

VSS

VSS

VREG5

VSS

VDD

VREFBUF

VSS

VSS

VDRIVE

VSS

VPIN<8..0>

VSIN<8..0>

VSS

BAT-

BAT+

VDD

VPAUX<4..1>

VSS

VREFBUF

RESET VSS

VSS

DUPP

VSS

VSS

VREG5

CB<8..1>

SCLK

CS_N

D_DWN_N

D_DWN_P

VSS

DDWNP

CCM

VSS

VSS

VSS

VSS

VREG5

VREF2

VDD

VREF1

VREF2

2

1

3

2

1

2

1

1

8

6

7

11

9

10

12 5

3

1

2

16

14

15

13 4

11

3

2

1

1

1

1

1

6

28

7

5

3

1

4

A C

A C

A C

1

1

1

11

A

C

A

C

1

3

3

2

1

11

1

1

1

21

1

21

13

1

1

1

1

3

NC

AD7284_THERMISTORS

VSS

VREFBUF

VPAUX<4..1>

VREG5

GPOP1

GPOP2

PAD

VSIN8

VSIN7

VSIN6

VSIN5

CB8

CB7

CB6

CB5

D_UP_N

D_UP

NC

NC

AGND2

ADCGND2

REFGND2

VREF2

NC

MASTER

DGND

DVCC

CCM

RESET

VDRIVE

CS_N

SCLK

SDI

SDO

D_DWN_N

D_DWN

AVCC

VPAUX4

VPAUX3

VPAUX2

VPAUX1

VREF1

VREFBUF

REFGND1

ADCGND1

VSIN4

VSIN3

VSIN2

VSIN1

VSIN0

CB4

CB3

CB2

CB1

AGND1

VSS

VSS

VPIN0

VPIN1

VPIN2

VPIN3

VPIN4

VPIN5

VPIN6

VPIN7

VPIN8

VDD

VDD

AD7284_CELL_CONNECTIONS

BAT+

VPIN<8..0>

VSIN<8..0>

CB<8..1>

BAT-

VSS

IO

NC1

VIN

GND TP

VOUT

NC

D

THIS DRAWING IS THE PROPERTY OF ANALOG DEVICES INC.

IN PART, OR USED IN FURNISHING INFORMATION TO OTHERS,

OR FOR ANY OTHER PURPOSE DETRIMENTAL TO THE INTERESTS

THE EQUIPMENT SHOWN HEREON MAY BE PROTECTED BY PATENTS

AC

IT IS NOT TO BE REPRODUCED OR COPIED, IN WHOLE OR

DRAWING NO.

2

SCALE

D

D

D

SIZE

D

REV

SHEET

1

1

A

2

3

4

3

5

8

D

7

67

8

A

B

CC

D

5

4

APPROVED

B

6

DESCRIPTION

REVISIONS

OF

OL G

E

OWNED OR CONTROLLED BY OWNED ANALOG DEVICES.

E

ANV

OF ANALOG DEVICES.

SCHEMATIC

S

PTD ENGINEER

DESIGN VIEW

REV DATE