9

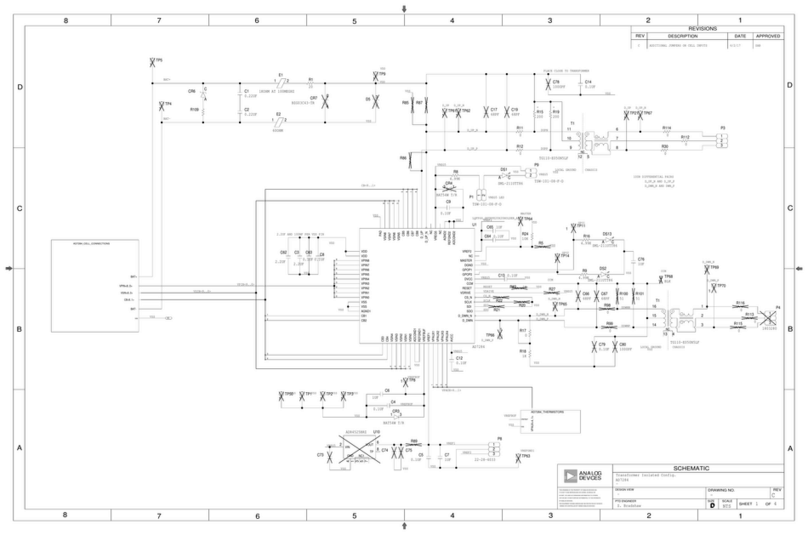

DEMO MANUAL DC 316 0A

Rev. 0

DEMONSTRATION CIRCUIT 3160A KIT

The PWRMD0 pin of the LTC9102/LTC9103 at address

ID:00b sets the maximum power allocation while operat-

ing autonomously. This pin connects to the RPWRMD resis-

tor using the PWRMD-1 jumper (JP1). RPWRMD, along

with the AUTO mode reset state are used to automatically

determine the power allocation per port. Refer to Table9

for the PWRMD0 and RPWRMD settings.

Device Configuration

The CFG0, CFG1, and CFG2 pins configure the number of

analog controllers and the port type in the system. Each pin

connects to a jumper that pulls either HI for a logical 1, or

LO for logical 0. CFG2 and CFG1 set the number of analog

controllers in the system. Refer to Table5 for the CFG[2:1]

settings. CFG0 sets whether the system is configured as

a 2-pair or 4-pair PSE, per Table6. Refer to Table7 and

Table8 for specific port type and number of ports for

each of the DC3160A-KITs. Refer to the Evaluating the

DC3160A-KIT as a 2-pair PSE section for more informa-

tion on 2-pair PSEs.

Custom Configurations

An LTC9101-1/LTC9102/LTC9103 system may be config-

ured in an arbitrary combination of 2-pair or 4-pair quads

by storing a custom configuration package in a dedicated

flash partition. If a stored configuration is utilized, the

state of the AUTO, CFG0, PWRMD0, and 4PVALID pins

can be overwritten by the configuration package. CFG[2:1]

are still required to inform the LTC9101-1 how many ana-

log controllers are in the system. AD[3:2] are still required

to inform the LTC9101-1 of the base I

2

C chip address.

Refer to the data sheet for more information and contact

ADI Applications for assistance with generating custom

configuration packages.

Digital Connections

The DC590 USB to I2C controller board is connected to

the DC3017A motherboard at J1 through a 14-pin ribbon

cable. I2C address pin AD3, and AD2 are set with a 2-bit

switch, SW3 on the DC3017A. Refer to Table4 for setting

the individual I

2

C address for each DC3160A-KIT. SDAOUT

and SDAIN can be tied together through a shunt resistor,

R73. Turrets on the DC3017A motherboard provide test

points for SCL, SDAIN, SDAOUT, VDD, DGND, INT, MSD,

and RESET.

MSD and RESET Pushbuttons

Pushbutton switch SW1, when pressed, pulls the RESET

pin of the daughter card logic low. The PSE control-

ler is then held inactive with all ports off. When SW1

is released, RESET is pulled high, and the PSE returns

to the AUTO mode reset state. Pushbutton switch SW2,

when pressed pulls the maskable shutdown input, MSD

pin of the daughter card logic low. When pressed, all ports

that have their corresponding mask bit set in the mconfig

register of the PSE controller will be shutdown. These

ports must then be manually re-enabled via I2C or by

resetting the PSE.

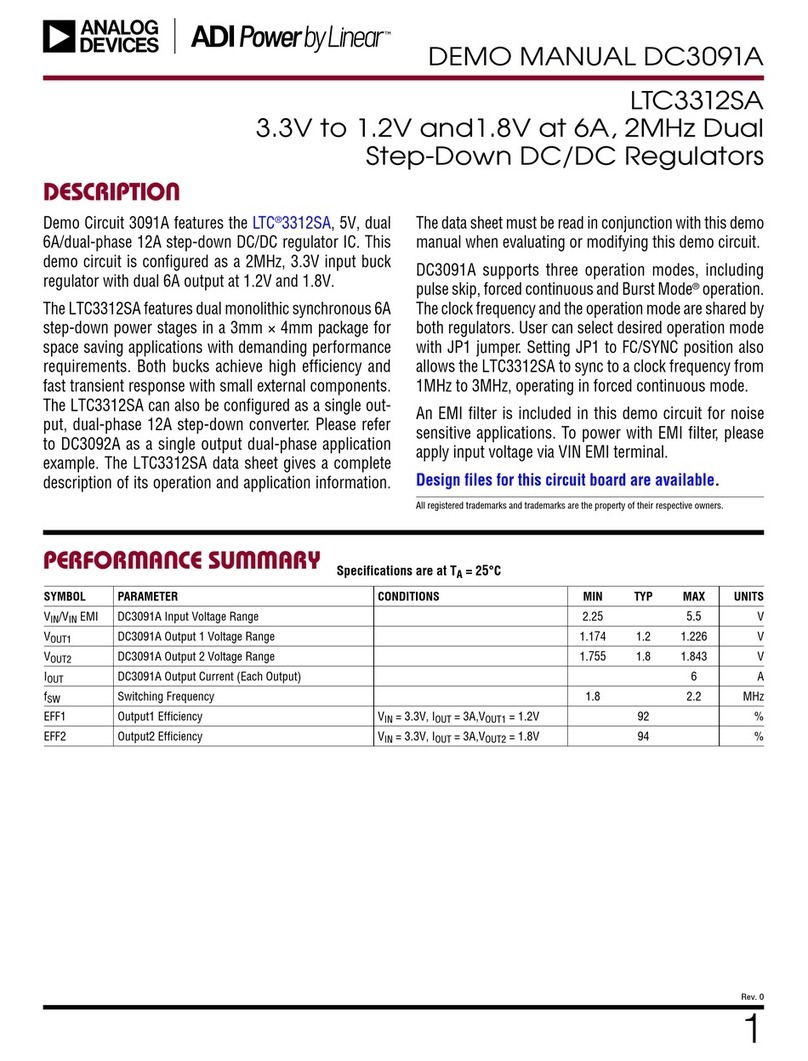

Onboard 3.3V Supply

The DC3017A motherboard has an onboard (non-iso-

lated) 3.3V/100mA buck regulator that provides a local

3.3V, with the net named BUCK33. This onboard logic

supply is for demonstration purposes only and allows for

use of a single supply while evaluating the DC3160A-KIT.

Surge Testing

The DC3160A-KIT can be configured with either the Digital

domain connected to reference ground plane, or with the

Digital domain floating with the Analog domain for dif-

ferent surge test setups. The default DC3160A-KIT con-

figuration has DGND connected to VEE and floating from

chassis ground.

Evaluating the DC3160A-KIT as a 2-pair PSE

The LTC9101-1/LTC9102/LTC9103 PSE chipset sup-

ports both 2-pair and 4-pair modes of operation, but the

DC3160A-KIT layout is specifically for 4-pair ports. Each

4-pair port may be physically split into two separate 2-pair

ports using an Ethernet splitter such as Tripp Lite’s N035-

001 or a custom Y-Cable. This device or cable splits the

pairsets from one RJ45 port at the PSE into two separate