Preliminary Technical Data UG-1828

Rev. PrC | Page 3 of 338

Datapath .................................................................................... 124

Digital Front End (DFE) ......................................................... 124

Analog Front End (AFE)......................................................... 129

Transmit Data Chain API Programming.............................. 130

Receiver/Observation Receiver Signal Chain........................... 131

Receive Data Chain.................................................................. 133

Analog Front-End Components ............................................ 134

LPF ............................................................................................. 135

ADC ........................................................................................... 135

Digital Front End Components.............................................. 136

DC Offset .................................................................................. 136

QEC............................................................................................ 137

DDC ........................................................................................... 137

Frequency Offset Correction.................................................. 137

PFIR ........................................................................................... 137

RSSI ............................................................................................ 137

Receive Data Chain API Programming ................................ 138

Transmitter/Receiver/Observation Receiver Signal Chain

Calibrations................................................................................... 140

Initial Calibrations ................................................................... 140

Tracking Calibrations .............................................................. 150

Receiver Gain Control ................................................................. 154

Receiver Datapath .................................................................... 155

Gain Control Modes ................................................................ 158

Gain Control Detectors........................................................... 166

AGC Clock and Gain Block Timing...................................... 169

Analog Gain Control API Programming.............................. 170

Digital Gain Control and Interface Gain (Slicer) ................ 177

Digital Gain Control and Interface Gain API Programming

.................................................................................................... 179

Usage Recommendations........................................................ 180

TES Configuration and Debug information ........................ 181

Rx Demodulator........................................................................... 184

Rx Narrow-band Demodulator Subsystem .......................... 184

Normal IQ Output Mode ........................................................ 188

Frequency Deviation Output Mode....................................... 188

API Programming.................................................................... 189

Power Saving and Monitor Mode .............................................. 191

Power-Down Modes ................................................................ 191

Power-Down/Power-Up Channel in Calibrated State ........ 192

Dynamic Interframe Power Saving........................................ 192

Monitor Mode .......................................................................... 194

Digital Predistortion.....................................................................197

Background................................................................................197

ADRV9001 DPD Function......................................................197

ADRV9001 DPD Supported Waveforms...............................199

DPD with Frequency Hopping (FH)......................................199

ADRV9001 DPD Performance ...............................................199

Closed Loop Gain Control (CLGC) .......................................201

DPD/CLGC Configuration .....................................................201

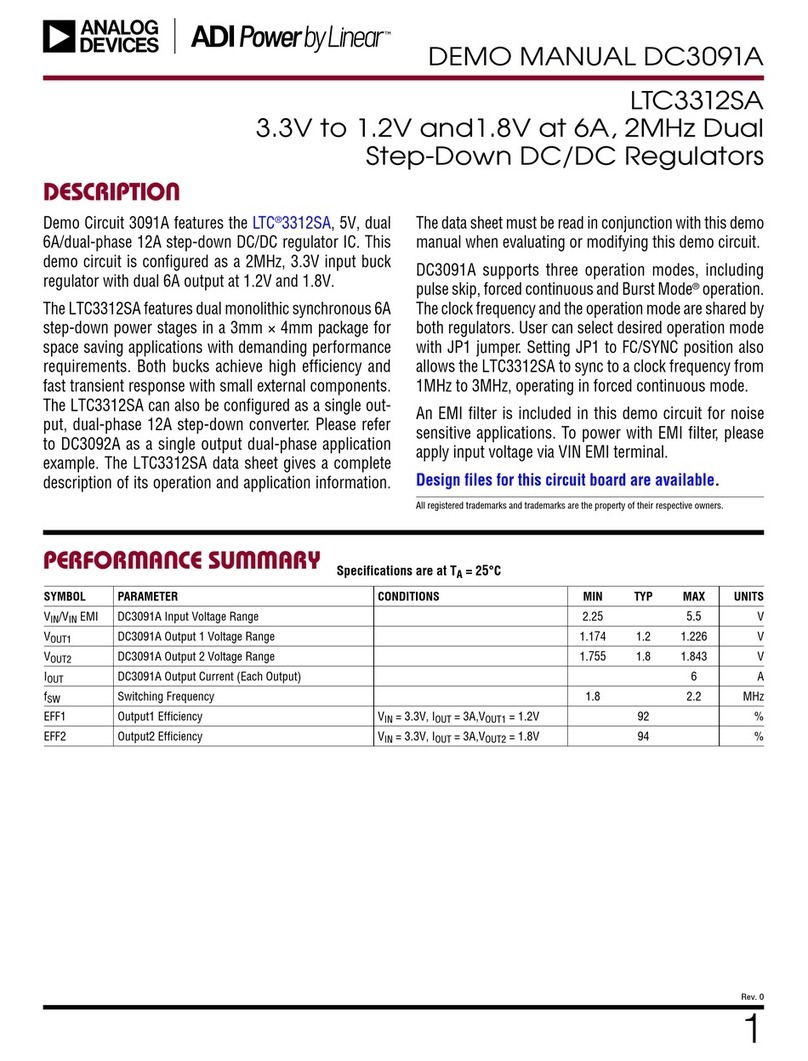

Board Configuration ................................................................210

Save and Load DPD Coefficients from Last Transmission .211

Define the Frequency Region when Performing DPD with

FH ...............................................................................................211

DPD/CLGC API Programming..............................................212

DPD Tuning and Testing .........................................................212

CLGC Target Gain Measurment.............................................215

Dynamic Profile Switching ..........................................................216

Overview ....................................................................................216

Initial Calibration with DPS ....................................................216

Perform DPS On the Fly ..........................................................217

DPS API Programming............................................................218

summary of DPS Limitations ..................................................218

DPS Operations in TES............................................................219

General-Purpose Input/Output and Interrupt Configuration221

Digital GPIO Operation...........................................................222

Analog GPIO Operation..........................................................225

Interrupt .....................................................................................226

Auxiliary Converters and Temperature Sensor.........................227

Auxiliary DAC (AuxDAC).......................................................227

Auxiliar y ADC (AuxADC) ......................................................227

Temperature Sensor ..................................................................228

RF Port Interface Information.....................................................229

Transmit Ports: TX1± and TX2±............................................229

Receive Ports: RX1A±, RX1B±, RX2A±, and RX2B± .........229

External LO Ports: LO1± and LO2± ......................................229

Device Clock Port: DEV_CLK1± ...........................................229

RF Rx/Tx Ports Impedance Data ............................................229

General Receiver Port Interface ..............................................232

General Transmitter Bias and Port Interface.........................234

Impedance Matching Network Examples..............................236

Receiver RF Port Impedance Matching Network.................236

Receiver RF Port Impedance Match Measurement Data ....239