ADP1974-EVALZ User Guide UG-883

Rev. 0 | Page 7 of 12

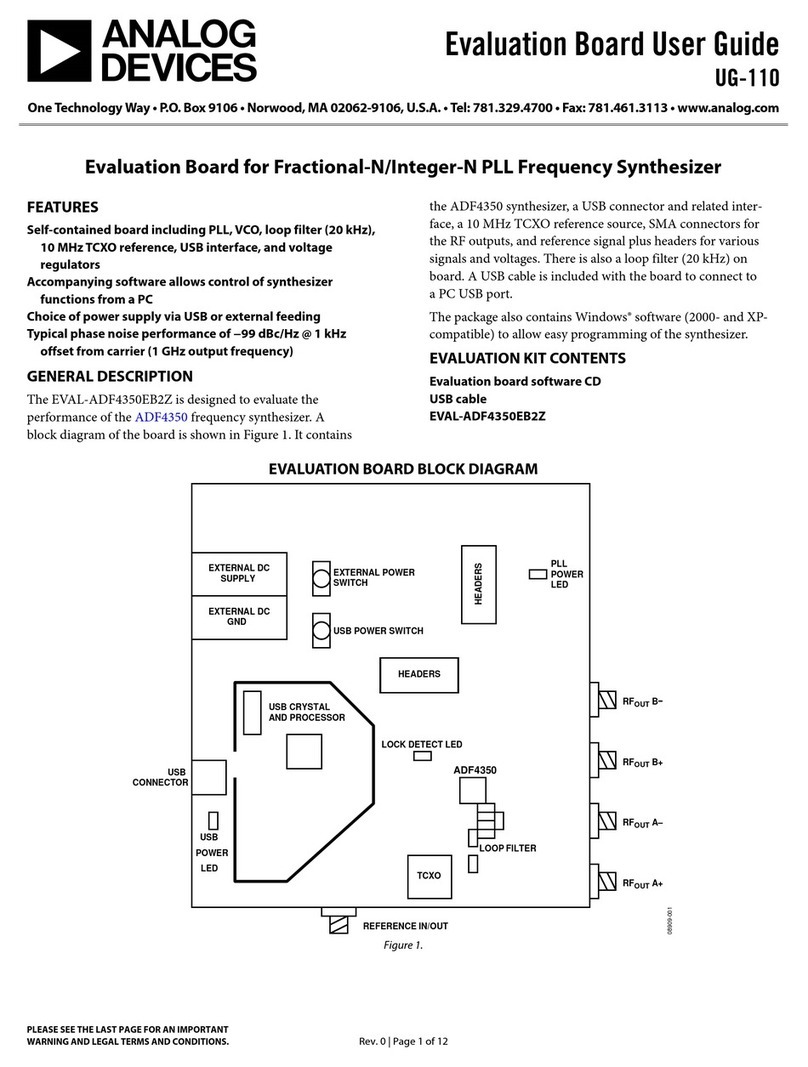

Maximum Duty Cycle Resistor (RDMAX)

To customize the maximum duty cycle of the DH and DL pins

for the ADP1974, use Figure 14 to select RDMAX.

450

0

50

100

150

200

250

300

400

350

020 40 60 80 100

R

DMAX

(kΩ)

DUTY CYCLE (%)

T

A

= +25°C

13517-014

Figure 14. RDMAX vs. Duty Cycle, RFREQ = 100 kΩ, VCOMP = 5 V

Current-Limit Set Resistor (RS)

If testing the current limit in an application, use the following

equation to set the current limit:

(6)

where:

IPK is the desired peak current limit in mA.

RSis the sense resistor used to set the peak current limit in Ω.

When the ADP1974 is configured to operate in buck (charge)

mode, the internal current-limit threshold is set to 300 mV

(typical) and the negative valley current-limit threshold is set to

450 mV (typical). When the ADP1974 is configured to operate

in boost (recycle) mode, the internal current-limit threshold is

set to 500 mV (typical). The external resistor (RCL) is needed to

offset the current properly to detect the peak in both buck and

boost operation. Set the RCL value to 20 kΩ. In operation, the

equations for setting the peak currents follow.

For buck/charge mode, the equations are

VCL (BUCK) = (ICL) × (RCL) − (IPK) × (RS) (7)

VNC (BUCK) = (ICL) × (RCL) + (IVL(NEG)) × (RS) (8)

For boost/recycle mode, the equation is

VCL (BOOST) = (ICL) × (RCL) + (IPK) × (RS) (9)

where:

VCL (BUCK) = 300 mV typical.

VNC (BUCK) = 450 mV typical.

VCL (BOOST) = 500 mV typical.

IPK = peak inductor current.

IVL(NEG) = valley inductor current.

ICL = 20 µA, typical.

RCL = 20 kΩ.

The ADP1974 is designed so that the peak current limit is the same

in both the buck mode and boost mode of operation. A tolerance

of 1% or better for the RCL and RSresistors is recommended.

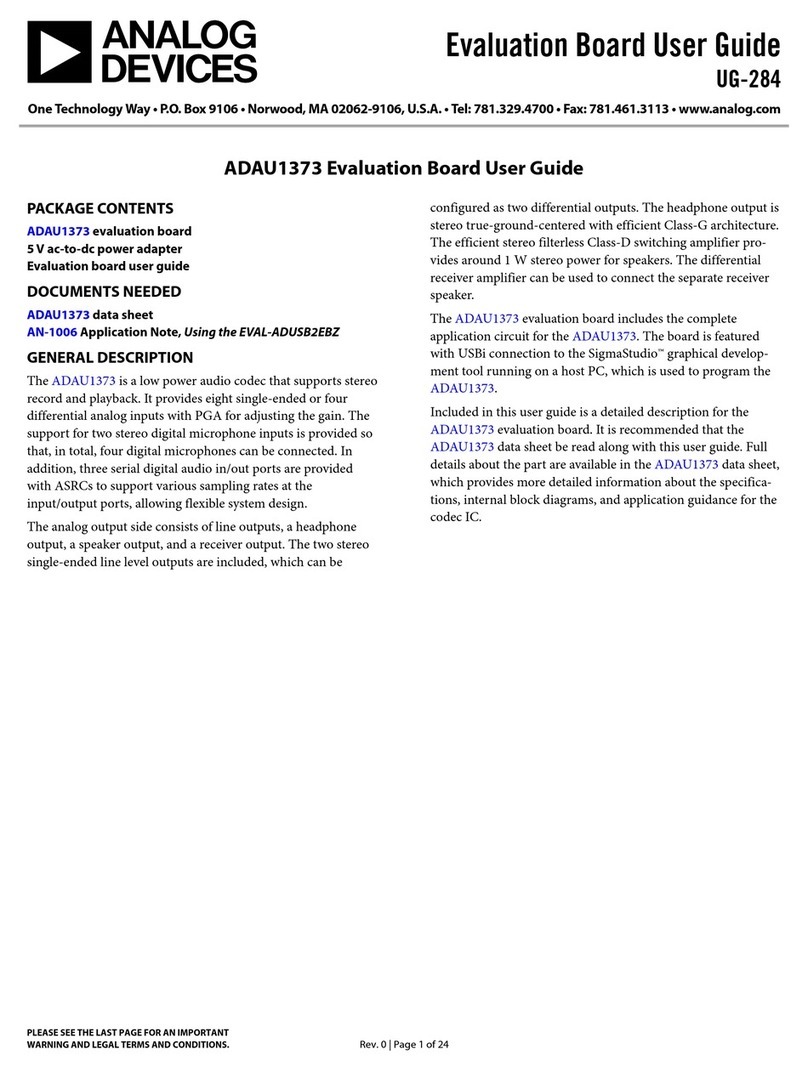

Soft Start Capacitor (CSS)

The ADP1974-EVA L Z comes with a 1 nF capacitor on the

evaluation board.

A CSS capacitor is not required for the ADP1974. When the CSS

capacitor is not used, the internal 5 µA (typical) current source

pulls the SS pin voltage to VREG, and there is no soft start control.

Use the following equation to calculate the delay time before

switching is enabled (tREG):

(10)

where:

ISS = 5 µA, typical.

CSS = soft start capacitor value.

During soft start, the ADP1974 operates in asynchronous

mode, and the synchronous FET is not driven. After the soft

start period is completed (SS > 4.5 V), the ADP1974 switches to

full synchronous mode.

VREG

4.5V

VOUT

0.52V

0V

V

SS

ENABLE

ADP1974 BEGIN

REGULATION

SYNCHRONOUS

OPERATION

t

REG

13517-015

Figure 15. Soft Start Diagram

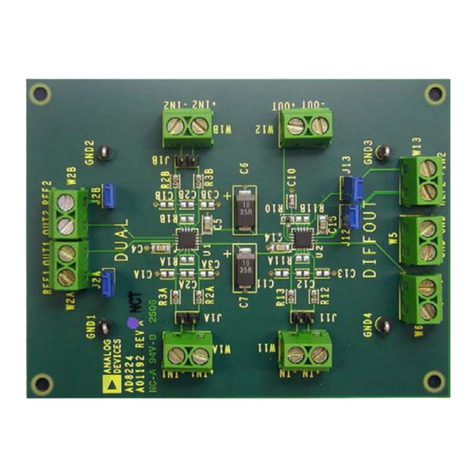

APPLICATION SPECIFIC ADP1974 CONTROL

When integrated in a battery test solution, the ADP1974 can be

controlled with external control signals from other devices in the

application. The FAULT pin allows an external device to signal

the ADP1974 when an external fault occurs. The COMP pin

allows an external device to control the PWM output signals on

the DH and DL pins. The SYNC and SCFG pins can be used to

synchronize the ADP1974 to an external clock signal or to

implement the ADP1974 as a master clock. The EN and MODE

pins provide logic control to turn the ADP1974 on or off and

to transition the system between boost/recycle mode and

buck/charge mode.