10 : COM Port PWR Setting Jumpers

PWR_COM1 (For COM Port1)

1-2: +5V (Default)

2-3: +12V

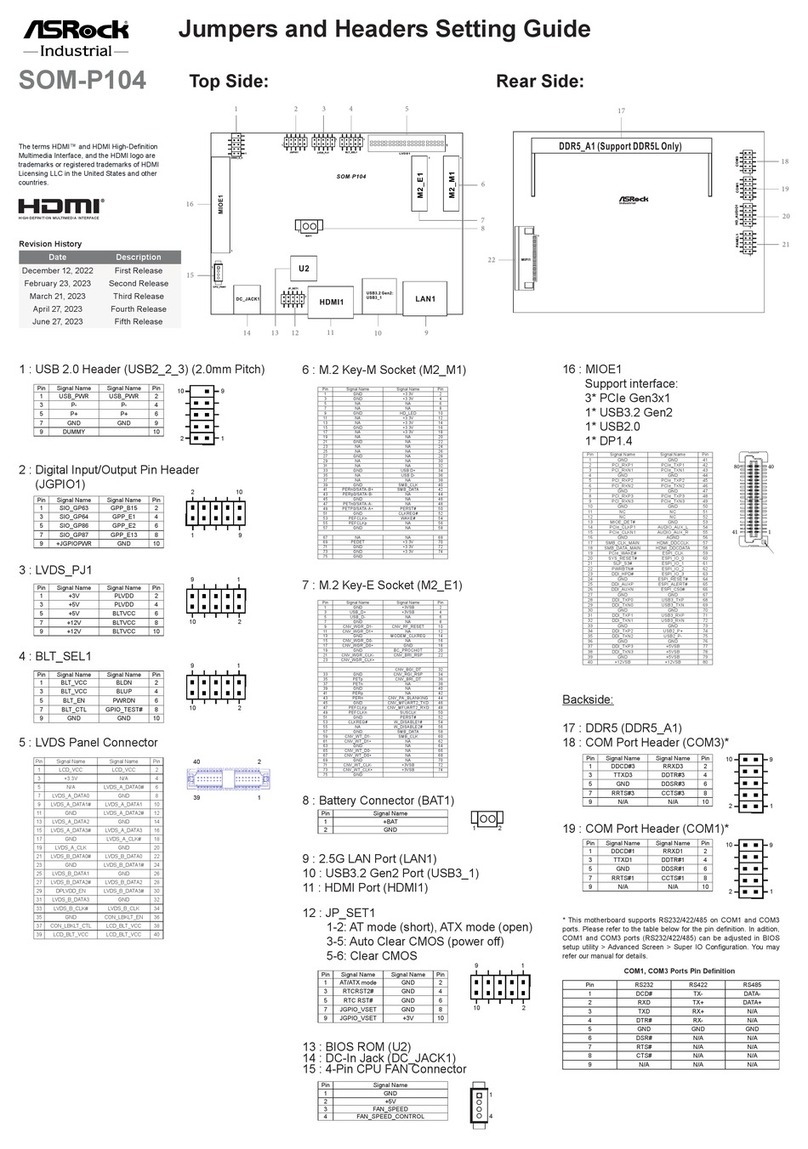

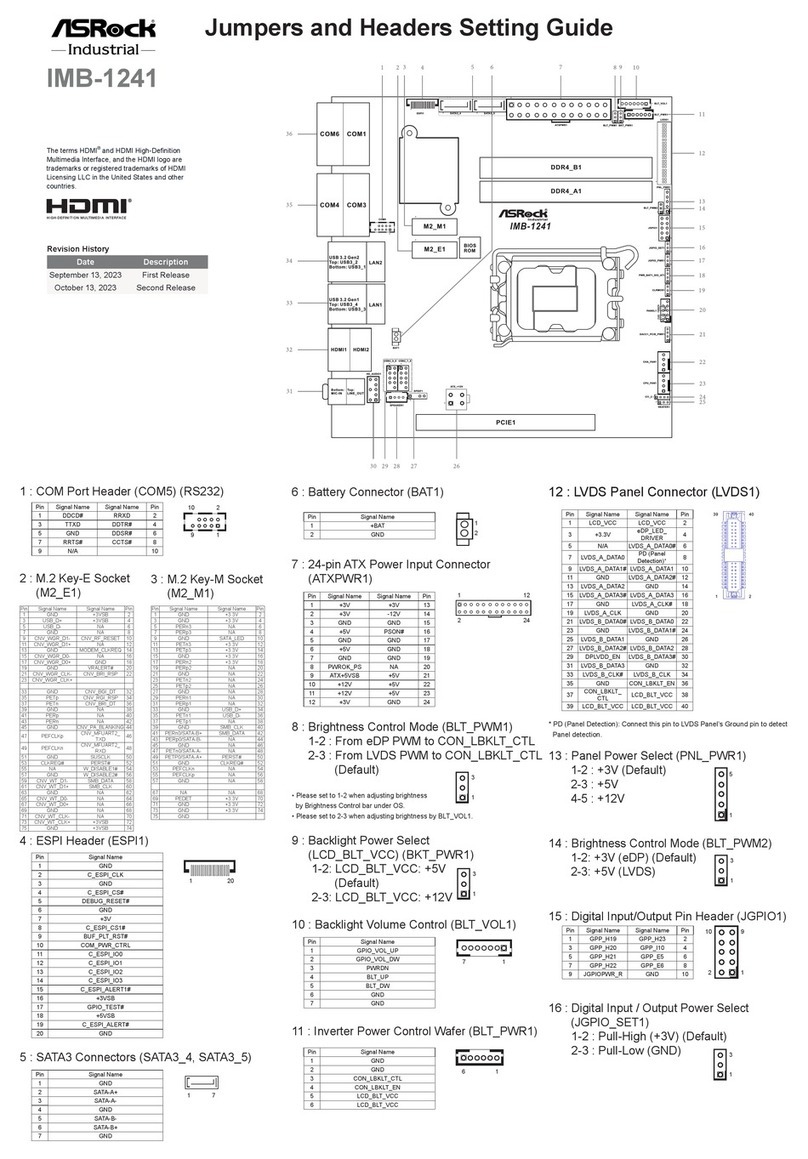

Jumpers and Headers Setting Guide

IMB-1239-WV

The terms HDMI® and HDMI High-Denition

Multimedia Interface, and the HDMI logo are

trademarks or registered trademarks of HDMI

Licensing LLC in the United States and other

countries.

Revision History

Date Description

April 24, 2023 First Release

August 14, 2023 Second Release

Industrial

IMB-1239-WV

16 (*Backside:

17

15

18

21

22

24

23

19

Mic In

1

HD_AUDIO1

PCIE1

USB 3.2 Gen2

T: USB3_2

B: USB3_1

Line Out

SATA3 _6 SATA3_5

HDMI2

LAN1

SPDIF1

1

M2_KEYM1

COM1

DC_JACK1

USB3_4_9

TO_UPS1

1

M2_KEYE1

PWR_ADAPTER

1

BLT_ VO L1 BLT_PWR1

1

1

COM3

40

20

BIOS

ROM

USB2_5_6

M2_B1

EDP_BLT_PWR2

1

1

1

1

JGPIO1

JGPIO_SET1

JGPIO_PWR1

BAT1 SATA_PWR1

1

1

1

1

1

1

1

1

CI1_2

CLRMOS1

1

PLED PWRBTN

HDLED RESET

1

PANEL1

SMBUS_TEST1

11

CPU_FAN1

C_FAN1HA

1

1

1

LAN2

1

USB2.0

T: USB3_8

B: USB3_7

DP1

HDMI1

PWR_BAT1_SIO_AT1

AT_TEST1_PCIE_PWR1

1

1

14

PWR_COM1

BKT_PWR1DACC1

HEATER1

11

1111

DDR _B15

DDR _A15

ESPI1

PNL_PWR1

1

LVDS 1

1

* This motherboard supports RS232/422/485 on COM1, 3 ports. Please refer to

the table below for the pin denition. In addition, COM1, 3 ports (RS232/422/485)

can be adjusted in BIOS setup utility > Advanced Screen > Super IO Congura-

tion. You may refer to our user manual for details.

** PD (Panel Detection): Connect this pin to

LVDS Panel’s Ground pin to detect Panel

detection.

1

2

1 : ESPI Header (ESPI1)

Pin Signal Name

1 GND

2 ESPI_CLK

3 GND

4 ESPI_CS#

5 ESPI_RESET#

6 GND

7 +3V

8 GND

9 SMB_CLK

10 SMB_DATA

11 ESPI_IO0

12 ESPI_IO1

13 ESPI_IO2

14 ESPI_IO3

15 GND

16 +3VSB

17 NA

18 GND

19 ESPI_ALERT#

20 GND

2 : M.2 Key-B Socket (M2_B1)

3 :

Battery Connector (BAT1)

4 : SATA Power Output Connector

(SATA_PWR1)

1 4

5 :

SATA3 Connectors (SATA3_5, SATA3_6)

Pin Signal Name Signal Name Pin

1 NA +3.3V 2

3 GND +3.3V 4

5 GND Full_Card_Power_o 6

7 USB_D+ W_DISABLE1# 8

9 USB_D- NA 10

11 GND

21 GND NA 20

23 NA NA 22

25 NA NA 24

27 GND NA 26

29 USB3_RX- NA 28

31 USB3_RX+ UIM_RESET 30

33 GND UIM_CLK 32

35 USB3_TX- UIM_DATA 34

37 USB3_TX+ UIM_PWR 36

39 GND NA 38

41 PERn0 NA 40

43 PERp0 NA 42

45 GND NA 44

47 PETn0 NA 46

49 PETp0 NA 48

51 GND PERST# 50

53 PEFCLKn CLKREQ# 52

55 PEFCLKp WAKE# 54

57 GND NA 56

59 NA NA 58

61 NA NA 60

63 NA NA 62

65 NA NA 64

67 NA NA 66

69 NA NA 68

71 GND +3.3V 70

73 GND +3.3V 72

75 NA +3.3V 74

6 :

Digital Input / Output Power Select

(JGPIO_PWR1)

1-2:

+12V (Default)

2-3:

+5V

7 :

Digital Input / Output

Default Value

Setting (JGPIO_SET1)

1-2: Pull-High (Default)

2-3: Pull-Low

8 :

Digital Input/Output Pin Header (JGPIO1)

Pin Signal Name Signal Name Pin

1SIO_GP71 GPP_H23 2

3SIO_GP72 GPP_I10 4

5SIO_GP73 GPP_E5 6

7SIO_GP74 GPP_E6 8

9JGPIOPWR_R GND 10

9 : COM Port Headers (COM1, COM3)*

Pin Signal Name Signal Name Pin

1DDCD# RRXD 2

3TTXD DDTR# 4

5GND DDSR# 6

7RRTS# CCTS# 8

9PWR 10

11 : HEATER1 Header (HEATER1)

Pin Signal Name

1 Heater PWR

2 GND

3 NCT

Pin Signal Name

1 +5V

2 GND

3 GND

4 +12V

Pin Signal Name

1 GND

2 SATA-A+

3 SATA-A-

4 GND

5 SATA-B-

6 SATA-B+

7 GND

1

7

13 : DACC1

Open: no ACC

Short: ACC (Default)

1 2

• Auto clear CMOS when system boot improperly.

14 : Backlight Volume Control

(BLT_VOL1)

15 :

Inverter Power Control Wafer

(BLT_PWR1)

Pin Signal Name

1 GPIO_VOL_UP

2 GPIO_VOL_DW

3 PWRDN

4 BLT_UP

5 BLT_DW

6 GND

7 GND

Pin Signal Name

1 GND

2 GND

3 CON_LBKLT_CTL

4 CON_LBKLT_EN

5 LCD_BLT_VCC

6 LCD_BLT_VCC

16** : LVDS Panel Connector

(LVDS1)

Pin Signal Name Signal Name Pin

1 LCD_VCC LCD_VCC 2

3 +3.3V N/A 4

5 N/A LVDS_A_DATA0# 6

7 LVDS_A_DATA0 PD (Panel Detection) 8

9 LVDS_A_DATA1# LVDS_A_DATA1 10

11 GND LVDS_A_DATA2# 12

13 LVDS_A_DATA2 GND 14

15 LVDS_A_DATA3# LVDS_A_DATA3 16

17 GND LVDS_A_CLK# 18

19 LVDS_A_CLK GND 20

21 LVDS_B_DATA0# LVDS_B_DATA0 22

23 GND LVDS_B_DATA1# 24

25 LVDS_B_DATA1 GND 26

27 LVDS_B_DATA2# LVDS_B_DATA2 28

29 DPLVDD_EN LVDS_B_DATA3# 30

31 LVDS_B_DATA3 GND 32

33 LVDS_B_CLK# LVDS_B_CLK 34

35 GND CON_LBKLT_EN 36

37 CON_LBKLT_CTL LCD_BLT_VCC 38

39 LCD_BLT_VCC LCD_BLT_VCC 40

12 : Backlight Power Select

(LCD_BLT_VCC) (BKT_PWR1)

1-2: LCD_BLT_VCC: +5V (Default)

2-3: LCD_BLT_VCC: +12V

4-5: LCD_BLT_VCC: DC_IN

Pin Signal Name

1 NA

2 GND

3 eDP_TX#3_CON

4 eDP_TX3_CON

5 GND

6 eDP_TX#2_CON

7 eDP_TX2_CON

8 GND

9 eDP_TX#1_CON

10 eDP_TX1_CON

11 GND

12 eDP_TX#0_CON

13 eDP_TX0_CON

14 GND

15 eDP_AUX_CON

16 eDP_AUX#_CON

17 GND

18 LCD_VCC

19 LCD_VCC

20 LCD_VCC

21 LCD_VCC

22 NA

23 GND

24 GND

25 GND

26 GND

27 eDP_HPD_CON

28 GND

29 GND

30 GND

31 GND

32 eDP_BKLTEN

33 eDP_BKLTCTL_R

34 SMB_DATA_MAIN

35 SMB_CLK_MAIN

36 LCD_BLT_VCC

37 LCD_BLT_VCC

38 LCD_BLT_VCC

39 LCD_BLT_VCC

40 NA

EDP1

40

1

** eDP Connector

(on the Backside

of PCB)

Pin RS232 RS422 RS485

1 DCD TX- RTX-

2 RXD RX+ N/A

3 TXD TX+ RTX+

4 DTR RX- N/A

5 GND GND GND

6 DSR N/A N/A

7RTS N/A N/A

8 CTS N/A N/A

9 PWR PWR PWR

COM1, 3 Ports Pin Denition

1 5

Pin Signal Name

1 +BAT

2 GND

120

12

123

123

2 10

1 9

19

210

3 2 1

123

1

1

7

6