CMD-5xx 08/07/02

2

CONTENTS

FEATURES ...................................................................................................................................................................3

CAUTIONARY NOTES..................................................................................................................................................5

GETTING STARTED .....................................................................................................................................................6

SOFTWARE DEVELOPMENT.........................................................................................................................................................6

TERMINAL SETTINGS..................................................................................................................................................................7

TUTORIAL..................................................................................................................................................................................7

Using the Debug Monitor.....................................................................................................................................................7

Programming the Onboard Flash Memory...........................................................................................................................8

MEMORY BANKS AND DEFAULT MEMORY MAP ......................................................................................................9

CMD-5XX DEFAULT MEMORY MAP...........................................................................................................................................9

SYNCHRONOUS SRAM MEMORY .............................................................................................................................................10

BURSTABLE FLASH MEMORY ...................................................................................................................................................10

PORT REPLACEMENT UNIT (PRU) MEMORY .............................................................................................................................10

MEM SOCKETS MEMORY ........................................................................................................................................................10

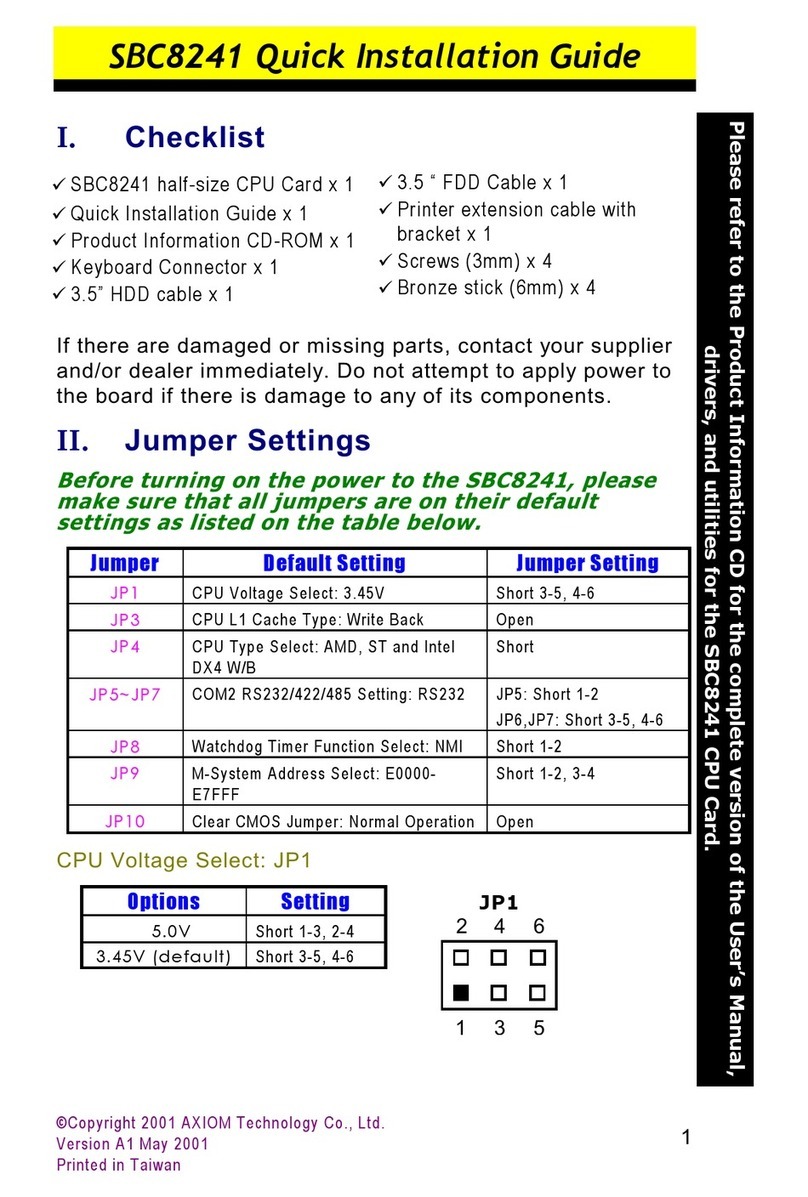

OPTION SWITCHES AND JUMPERS..............................................................................................................................................11

Mode Switch 1-4 External Reset Configuration Options...................................................................................................... 11

Mode Switch 1...................................................................................................................................................................11

Mode Switch 2...................................................................................................................................................................11

Mode Switch 3...................................................................................................................................................................11

Mode Switch 4...................................................................................................................................................................11

CFG_EN Jumper...............................................................................................................................................................11

MEMORY DEVICE / BANK SELECTION AND CONFIGURATION...................................................................................................... 12

Memory Bank Chip Select Configuration............................................................................................................................ 12

MAP_SW – Ram Bank and Flash Bank Options..................................................................................................................12

MEM_EN Jumper..............................................................................................................................................................13

MEM_OPT Jumper............................................................................................................................................................13

MEM_VOLT Jumper.......................................................................................................................................................... 13

PRU_EN Jumper ...............................................................................................................................................................13

COMMUNICATION PORTS.........................................................................................................................................14

COM_SWITCH - SERIAL PORT CONFIGURATION..................................................................................................................... 14

JP1 – COM-2 DCE/DTE Option ........................................................................................................................................ 14

DATA LINK CONTROLLER / J1850.............................................................................................................................................15

CAN INTERFACE AND OPTIONS ................................................................................................................................................15

LCD-PORT AND KEYPAD / KEY-PORT ...............................................................................................................................16

LCD / Keypad Memory Map ..............................................................................................................................................16

LCD Display CONTRAST..................................................................................................................................................16

JP2 - LCD_PORT Power Polarity Select............................................................................................................................ 16

PERSONALITY MODULE (PM-5XX) OPTIONS AND SETTINGS................................................................................17

CONFIG SWITCH ....................................................................................................................................................................17

PM-555/6 HARDWARE OPTIONS...............................................................................................................................................17

PM- 555/6 -T Additional Options ....................................................................................................................................... 17

PM-561/2/3/4 HARDWARE OPTIONS......................................................................................................................................... 18

PM561/2/3/4-T Options ..................................................................................................................................................... 18

PM-565/6 HARDWARE OPTIONS...............................................................................................................................................19

TROUBLESHOOTING.................................................................................................................................................20