2

GENERAL INFORMATION

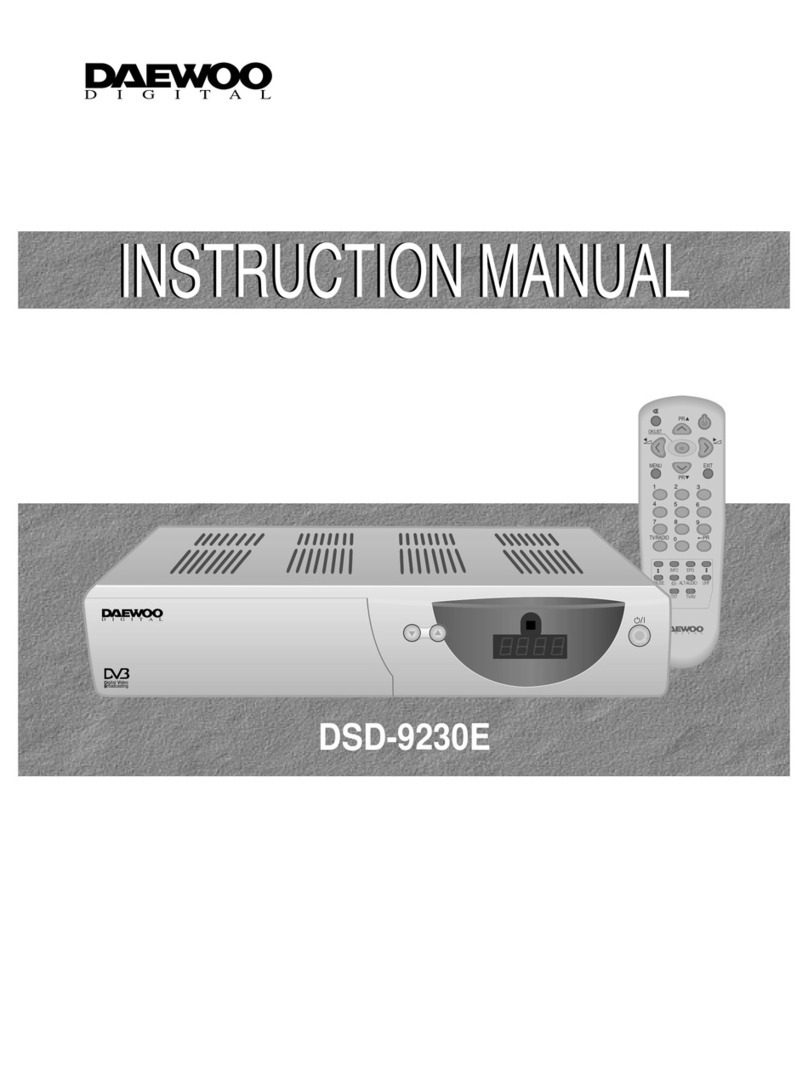

Digital Satellite Receiver is easy to use, and allows you to watch digital programs broadcasted via satellite.

This instruction manual will guide you through the initial installation of your receiver.

It also describes how to take full advantage of a wide range of features that are easily accessible.

Read this instruction manual carefully before installing your receiver.

MAIN FEATURES

• High quality Digital Video & Audio

• Fully DVB compliant

• Common Interface with 2 PCMCIA slots

• User friendly and easy-to use menu system

• Various channel editing function, on Channel Management. (favorite, move, lock, rename, delete and sort)

• User programmable Satellite & Transponder information

• Automatic search for newly added transponder (NIT search)

• Stores up to 4000 channels

• Support software upgrading through RS-232C port

• Plug-and-play data transfer system (DSR to DSR)

• Individual channel volume saving function

• Timer function

• Automatic reserved channel moving system

• Electronic Program Guide (EPG)

• Teletext function support

• Support RGB and CVBS video output

• SCPC/MCPC receivable from C/Ku Band

• Multi LNB control by DiSEqC 1.0 and 22 KHz switching

• Motorized system control by DiSEqC 1.2* and USALS**.

• 256 color On-Screen-Display

• Support S/PDIF output

(Optional function)

* DiSEqC

TM

is a trademark of EUTELSAT.

** USALS

TM

is a trademark of Stab.