Digital Equipment PDP-11 Series User manual

Other Digital Equipment Computer Hardware manuals

Digital Equipment

Digital Equipment VT 14 User manual

Digital Equipment

Digital Equipment DECbridge 90FL User manual

Digital Equipment

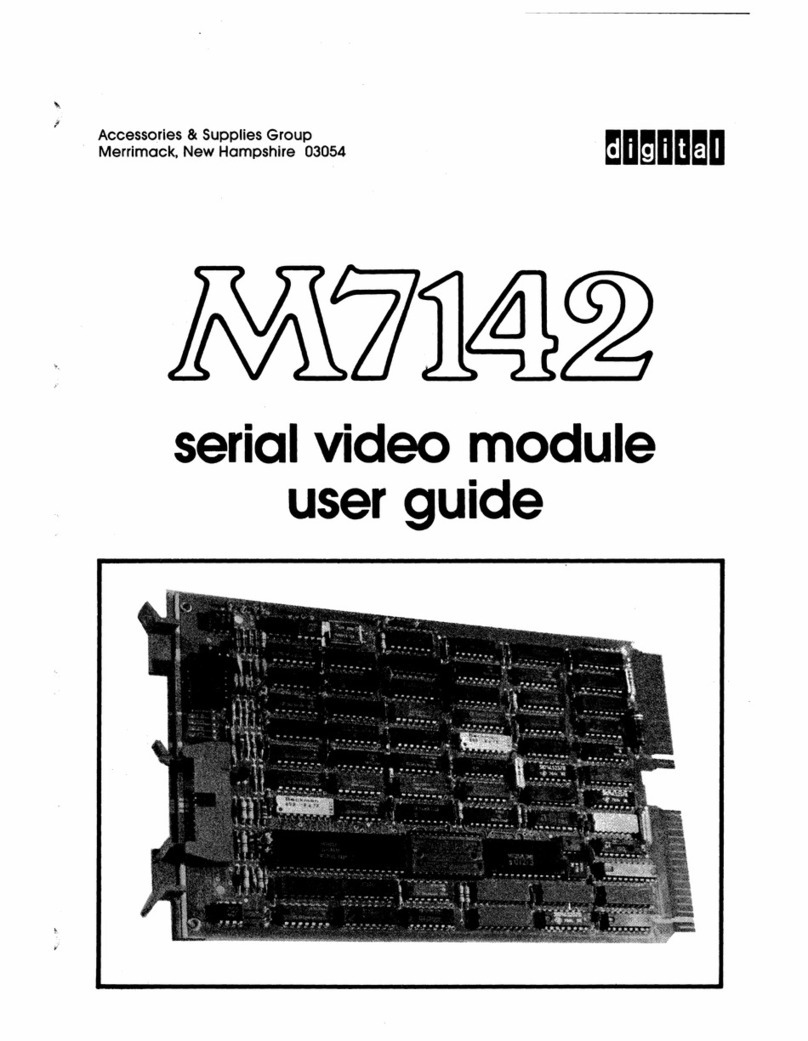

Digital Equipment M7142 User manual

Digital Equipment

Digital Equipment 300 Series AXP Guide

Digital Equipment

Digital Equipment Venturis FX Operating and maintenance instructions

Digital Equipment

Digital Equipment PDP-8 User manual

Digital Equipment

Digital Equipment RK05 Series User manual

Digital Equipment

Digital Equipment PDP-12 User manual

Digital Equipment

Digital Equipment BA11-K User manual

Digital Equipment

Digital Equipment VAX 4000 100 Guide

Digital Equipment

Digital Equipment VAX-11 /730 User manual

Digital Equipment

Digital Equipment DF32 User manual

Digital Equipment

Digital Equipment VAX 6000 Model 500 Instruction Manual

Digital Equipment

Digital Equipment PDP-11 Series User manual

Digital Equipment

Digital Equipment VAX 6000 User manual

Digital Equipment

Digital Equipment Digital Semiconductor 21164 Alpha... User manual

Digital Equipment

Digital Equipment PDP-9 Guide

Digital Equipment

Digital Equipment PC04 User manual

Digital Equipment

Digital Equipment VAX 4000 Series Guide

Digital Equipment

Digital Equipment PDP16-M User manual

Popular Computer Hardware manuals by other brands

EMC2

EMC2 VNX Series Hardware Information Guide

Panasonic

Panasonic DV0PM20105 Operation manual

Mitsubishi Electric

Mitsubishi Electric Q81BD-J61BT11 user manual

Gigabyte

Gigabyte B660M DS3H AX DDR4 user manual

Raidon

Raidon iT2300 Quick installation guide

National Instruments

National Instruments PXI-8186 user manual