3 - 3

When the [FIL] switch is turned “2F3K”, the filter is selected

FI761 which covering the 2.4 kHz bandwith.

When the [FIL] switch is turned “2FOP”, the filter is selected

an optional filter.

When the [FIL] switch is turned “2FTH”, the signal from the

2nd IF amplifier bypass the crystal bandpass filters through

D771 and D773.

The filtered or bypassed signal is amplified at the buffer

amplifier (Q801) and applied to the 3rd mixer circuit (IC811).

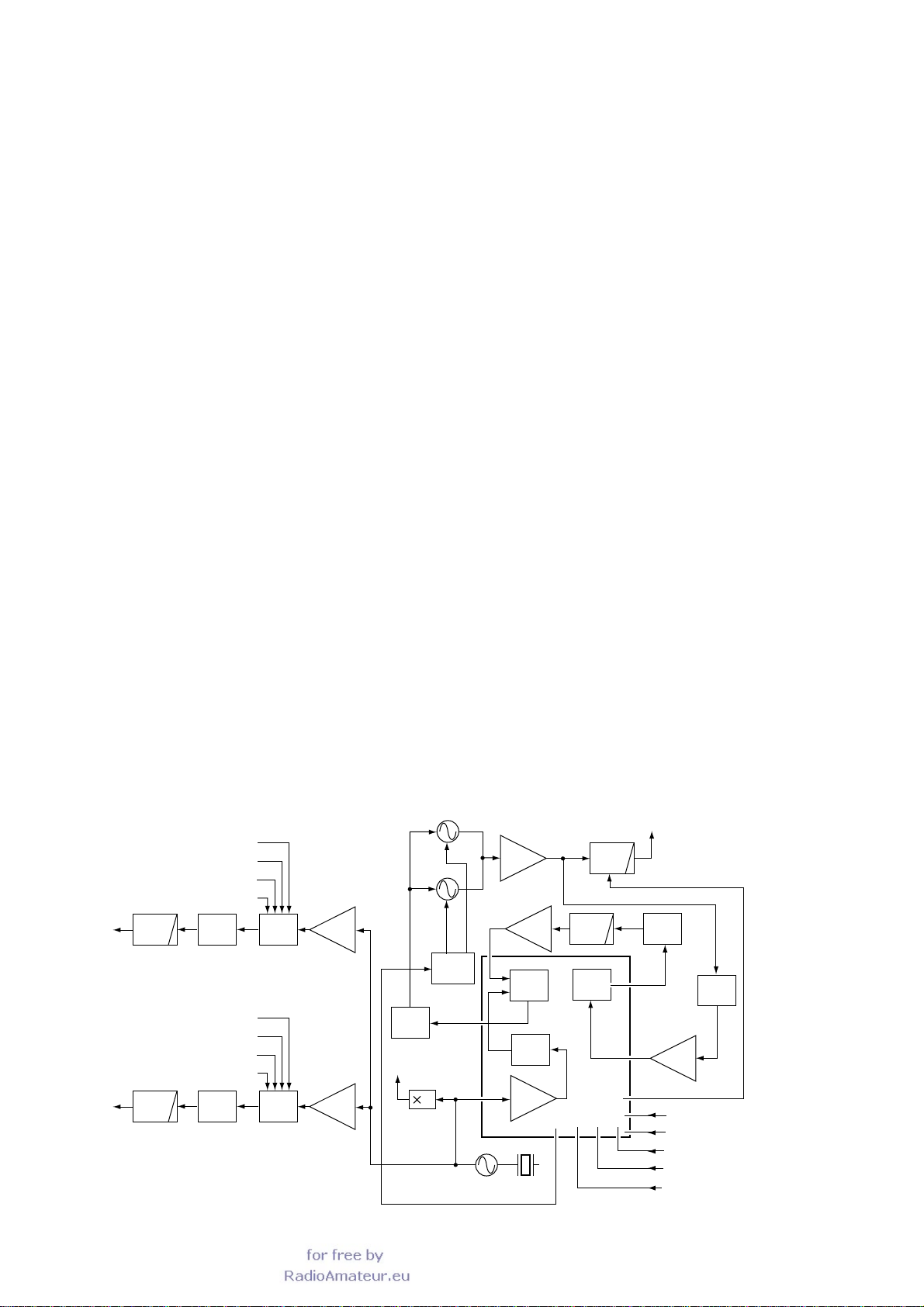

3-1-6 NOISE BLANKER CIRCUITS (MAIN UNIT)

The IC-R75 uses a trigger noise blanker circuit which

removes pulse-type noise signals at the noise blanker gate

(D711–D714).

The 2nd IF signal passes through the crystal bandpass filter

(FI701) to suppress unwanted signals.A portion of the output

signal is applied to a noise amplifier circuit (IC731, Q731,

Q733) and detected at a noise detector circuit (D731). The

detected voltage is applied to a noise blanker gate control cir-

cuit (Q735–Q737, D732).

The threshold level of the noise blanker gate control circuit

(Q735–Q737, D732) is set at 1.0 V on SSB mode (In case of

AM mode, is set at 1.6 V). When the detected voltage

exceeds the threshold level, Q737 outputs a blanking signal

to activate the noise blanker gate (D711–D714).

A portion of the detected voltage is applied to the noise

blanker AGC circuit (Q732, Q734). The noise components

are fed back to the noise amplifier (IC731). The time constant

of the noise blanker AGC circuit is determined by R737,

R744 and C739. This AGC circuit does not operate to detect

pulse-type noise.

When the operating frequency or mode is changed, the

“UNLC” signal is applied to the noise blanker gate control cir-

cuit (D732). The noise blanker gate prevents PLLclick noise.

3-1-7 3RD MIXER AND IF CIRCUITS (MAIN UNIT)

The 2nd IF signal is mixed with a 9.4665 MHz 3rd LO signal

to produce a 450–456 kHz 3rd IF signal at the 3rd mixer

(IC811).

The 9.4665 MHz 3rd LO signal is applied to the 3rd mixer IC

(IC811, pin 10) from the PLL unit via J811. The 450–456 kHz

3rd IF signal is applied either to one of the 3 ceramic band-

pass filters (FI851, FI861, FI871) or to an optional crystal

bandpass filter to suppress unwanted signals.

When the [FIL] switch is turned “3F3K”, the filter is selected

FI851 which covering the 2.4 kHz bandwith.

When the [FIL] switch is turned “3F6K”, the filter is selected

FI861 which covering the 6 kHz bandwith.

When the [FIL] switch is turned “3F15”, the filter is selected

FI871 which covering the 15 kHz bandwith.

When the [FIL] switch is turned “3FOP”, the filter is selected

an optional crystal bandpass filter.

When the mode is selected SSB mode, the filtered 3rd IF sig-

nal is amplified at the 3rd IF amplifier (Q891), and is then

applied to the 3rd IF amplifier (Q911) via the receiver total

gain control circuit (R898). The amplified signal is applied to

the SSB demodulator circuit.

When the mode is selected FM mode, the filtered 3rd IF sig-

nal is amplified at the 3rd IF amplifier (Q891), and is then

applied to the FM demodulator circuit.

When the mode is selected AM mode, the filtered 3rd IF sig-

nal is amplified at the 3rd IF amplifier (Q891), and is then

applied to the 3rd IF amplifier (Q911) via the receiver total

gain control circuit (R898). The amplified signal is applied to

the AM demodulator circuit.

1st, 2nd and 3rd IF amplifiers (Q471, Q721, Q891) are con-

trolled by AGC bias voltage.

3-1-8 BFO CIRCUIT (PLL UNIT)

The BFO (Beat Frequency Oscillator) circuit consists of Q1,

X1, Q201 and IC 201 on PLL unit. The oscillator provides a

beat frequency signal to the SSB demodulator circuit (MAIN

UNIT; IC1101) for demodulating the 3rd IF signal into an AF

signal.

The 30 MHz signal is oscillated at Q1 and X1 for the system

clock signal of the DDS IC (IC201). The oscillated signal is

amplified at Q201 and is applied to the DDC IC (IC201, pin

7) to produce the 455 kHz BFO signal.

The 455 kHz signal passes through the low-pass filter (L201,

L202, C202–C207) via the D/A converter, and is then mixed

with the 3rd IF signal at the SSB demodulator circuit (MAIN

unit; IC1101).

3-1-9 DEMODULATOR CIRCUIT (MAIN UNIT)

The demodulator circuit consists of 3 detector circuits.

(1) SSB DEMODULATOR CIRCUIT

A product detector (IC1101) demodulates SSB, RTTY and

CW signals into an AF signal. The 3rd IF signal from the IF

amplifier (Q911) is mixed with the BFO signal at the product

detector (IC1101) to be demodulated into an AF signal. The

AF signal passes through the AF input mode selector switch

(IC1201).

(2) FM DEMODULATOR CIRCUIT

A FM detector (IC1001, X1001) demodulates the FM signal

into an AF signal. The 3rd IF signal from the IF amplifier

(Q891) is amplified at the 3rd IF amplifier (Q1001), and is

then applied to the FM detector (IC1001, X1001) to demodu-

late the 3rd IF signal. The demodulated signal is applied to

the de-emphasis circuit (IC1211D) to produce the FMAF sig-

nal. The AF signal passes through the AF input mode selec-

tor switch (IC1201).

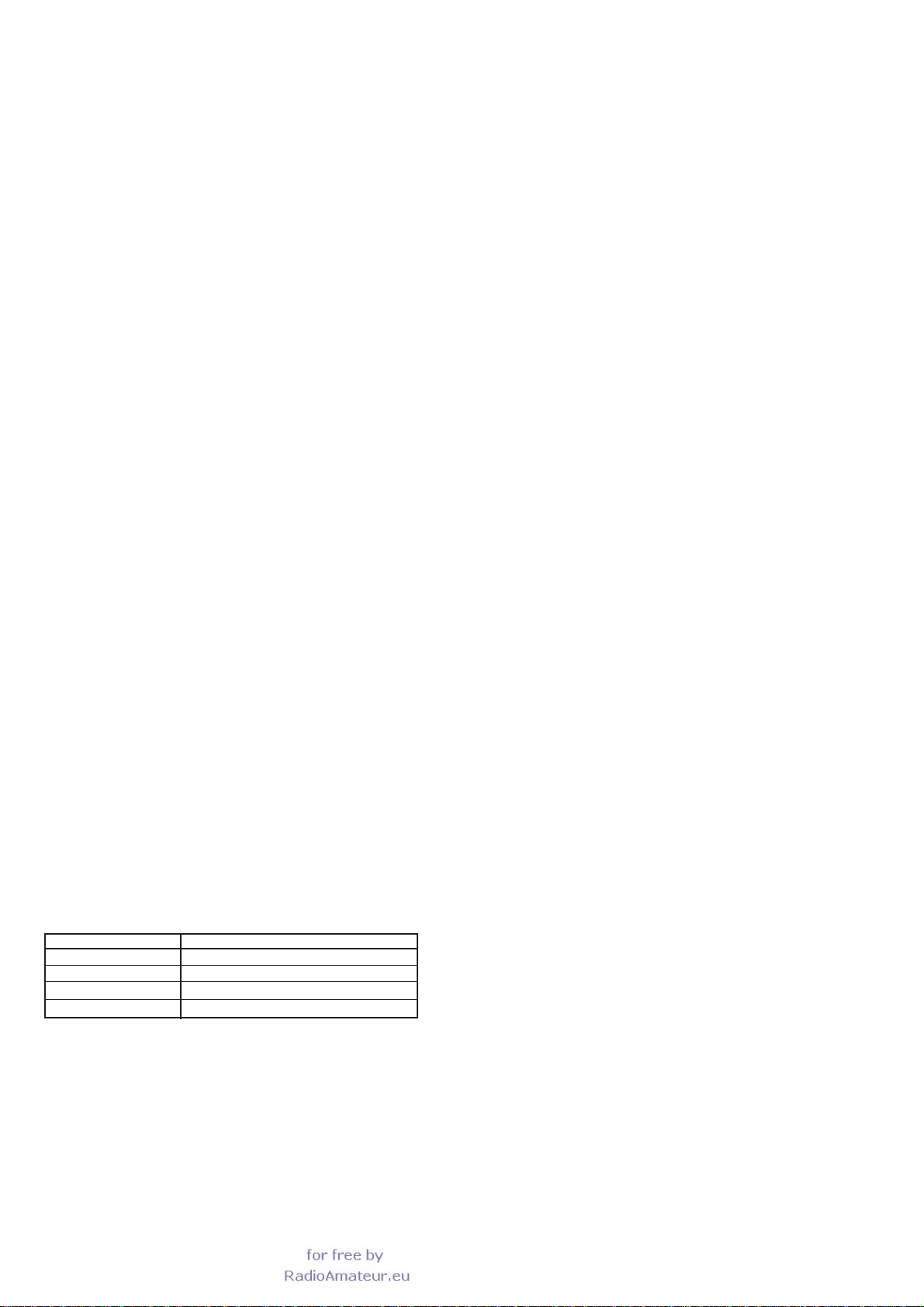

MODE

LSB, USB

CW

RTTY

AM, S-AM

FREQUENCY

455.0 kHz

455.9 kHz

456.0 kHz

450.0 kHz

3RD IF FREQUENCY