ISL28113, ISL28213, ISL28413

9FN6728.5

June 9, 2011

Applications Information

Functional Description

The ISL28113, ISL28213 and ISL28413 are single, dual and

quad, CMOS rail-to-rail input, output (RRIO) micropower

operational amplifiers. They are designed to operate from single

supply (1.8V to 5.5V) or dual supply (±0.9V to ±2.75V). The parts

have an input common mode range that extends 100mV above

and below the power supply voltage rails. The output stage can

swing to within 15mV of the supply rails with a 10kΩ load.

Input ESD Diode Protection

All input terminals have internal ESD protection diodes to both

positive and negative supply rails, limiting the input voltage to

within one diode beyond the supply rails (see “Pin Descriptions -

Circuit 1” on page 3). For applications where the input voltage

may exceed either power supply voltage by 0.5V or more, an

external series resistor must be used to ensure the input currents

never exceed 20mA (see Figure 19).

Output Phase Reversal

Output phase reversal is a change of polarity in the amplifier

transfer function when the input voltage exceeds the supply

voltage. The ISL28113, ISL28213 and ISL28413 are immune to

output phase reversal, even when the input voltage is 1V beyond

the supplies.

Unused Channels

If the application requires less than all amplifiers one channel,

the user must configure the unused channel(s) to prevent it from

oscillating. The unused channel(s) will oscillate if the input and

output pins are floating. This will result in higher than expected

supply currents and possible noise injection into the channel

being used. The proper way to prevent this oscillation is to short

the output to the inverting input and ground the positive input (as

shown in Figure 20).

Power Dissipation

It is possible to exceed the +125°C maximum junction

temperatures under certain load, power supply conditions and

ambient temperature conditions. It is therefore important to

calculate the maximum junction temperature (TJMAX) for all

applications to determine if power supply voltages, load

conditions, or package type need to be modified to remain in the

safe operating area. These parameters are related using

Equation 1:

where:

•P

DMAXTOTAL is the sum of the maximum power dissipation of

each amplifier in the package (PDMAX)

•PD

MAX for each amplifier can be calculated using Equation 2:

where:

•T

MAX = Maximum ambient temperature

•θJA = Thermal resistance of the package

•PD

MAX = Maximum power dissipation of 1 amplifier

•V

S= Total supply voltage

•I

qMAX = Maximum quiescent supply current of 1 amplifier

•V

OUTMAX = Maximum output voltage swing of the application

•R

L= Load resistance

ISL28113, ISL28213 and ISL28413 SPICE

Model

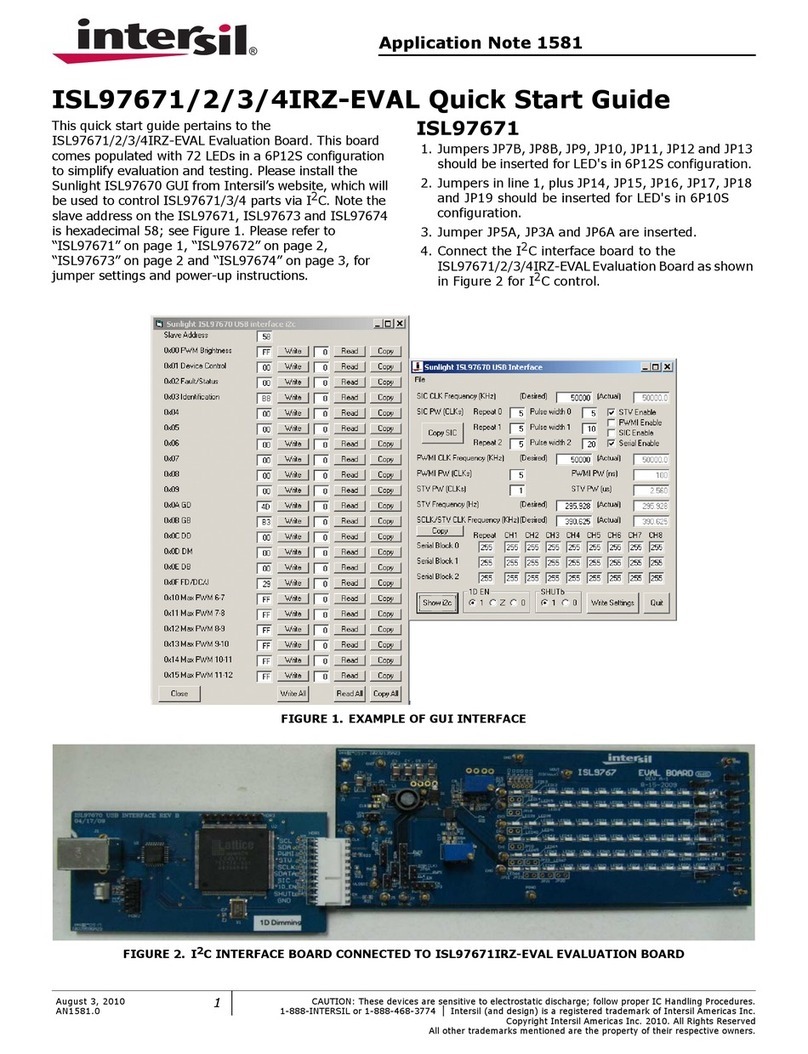

Figure 21 shows the SPICE model schematic and Figure 22 shows

the net list for the SPICE model. The model is a simplified version

of the actual device and simulates important AC and DC

parameters. AC parameters incorporated into the model are: 1/f

and flatband noise, Slew Rate, CMRR, Gain and Phase. The DC

parameters are IOS, total supply current and output voltage swing.

The model uses typical parameters given in the “Electrical

Specifications” Table beginning on page 4. The AVOL is adjusted

for 85dB with the dominate pole at 100Hz. The CMRR is set 72dB,

f = 35kHz). The input stage models the actual device to present an

accurate AC representation. The model is configured for ambient

temperature of +25°C.

Figures 23 through 32 show the characterization vs simulation

results for the Noise Voltage, Closed Loop Gain vs Frequency,

Large Signal 5V Step Response, CMRR and Open Loop Gain

Phase.

FIGURE 19. INPUT ESD DIODE CURRENT LIMITING

-

+

RIN-

RL

VIN-

V+

V-

RIN+

RF

RG

FIGURE 20. PREVENTING OSCILLATIONS IN UNUSED CHANNELS

-

+

TJMAX TMAX θJAxPDMAXTOTAL

+= (EQ. 1)

PDMAX VSIqMAX VS

(- VOUTMAX)VOUTMAX

RL

------------------------

×+×=(EQ. 2)