Table 16 Supported Linux Versions ..................................................................... 13

Table 17 SSI Connector Pin Assignment for PCIe-5312/5315 ............................. 40

Table 18 Relationship between switch position and slot number ...................... 41

Table 19 Random Noise .......................................................................................45

Figure 1 JYPEDIA Information ................................................................................ 2

Figure 2 Experiment Setup .................................................................................... 3

Figure 3 -3dB Bandwidth ....................................................................................... 7

Figure 4 CMRR ....................................................................................................... 8

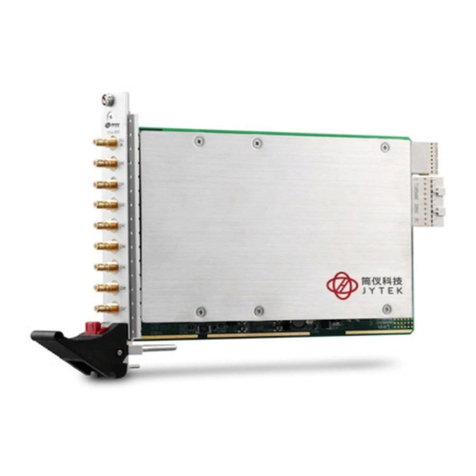

Figure 5 JY5312/5315 Front Panel .......................................................................11

Figure 6 AI Simultaneous Mode Acquisition ........................................................17

Figure 7 MultiChannel Continuous Parament ..................................................... 19

Figure 8 Multichannel Continuous Acquisition ................................................... 19

Figure 9 Differential Mode for Grounding Signal ................................................ 20

Figure 10 Differential Mode for Floating Signal .................................................. 20

Figure 11 Immediate Trigger Paraments .............................................................21

Figure 12 SoftwareTrigger Paraments .................................................................22

Figure 13 Software trigger Acquisition ................................................................ 23

Figure 14 Rising Slope Trigger ..............................................................................24

Figure 15 Falling Slope Trigger .............................................................................24

Figure 16 Hysteresis with Rising Slope Trigger ....................................................25

Figure 17 Hysteresis with Falling Slope Trigger ................................................... 25

Figure 18 Entering Window Trigger .....................................................................26

Figure 19 Leaving Window Trigger ...................................................................... 26

Figure 20 Analog Trigger Paraments ................................................................... 27

Figure 21 Waiting For Trigger .............................................................................. 27

Figure 22 Analog Trigger Acquisition ...................................................................28

Figure 23 External Digital Trigger ........................................................................ 28

Figure 24 Digital Trigger Paraments .................................................................... 29

Figure 25 Digital Trigger Acquisition ....................................................................30

Figure 26 Start Trigger ......................................................................................... 31

Figure 27 Reference Trigger ................................................................................ 32

Figure 28 Re-Trigger .............................................................................................32

Figure 29 Retrigger Paraments ............................................................................ 33

Figure 30 Retrigge rIn Start Trigger Mode ...........................................................34

Figure 31 Retrigger in Reference Trigger Mode .................................................. 34

Figure 32 Retrigger Paraments ............................................................................ 35

Figure 33 Retrigger Complete State .................................................................... 35

Figure 34 Single Digital Output ............................................................................36

Figure 35 Single Digital Input ...............................................................................37

Figure 36 Timing diagram .................................................................................... 38