II

Table of Contents

Geng Service �������������������������������������������������������������������������������������������������� I

1 Introducon������������������������������������������������������������������������������������������������ 1

1�1 Features ��������������������������������������������������������������������������������������������� 1

1.2 Applicaons ��������������������������������������������������������������������������������������� 1

1.3 Specicaons ������������������������������������������������������������������������������������� 2

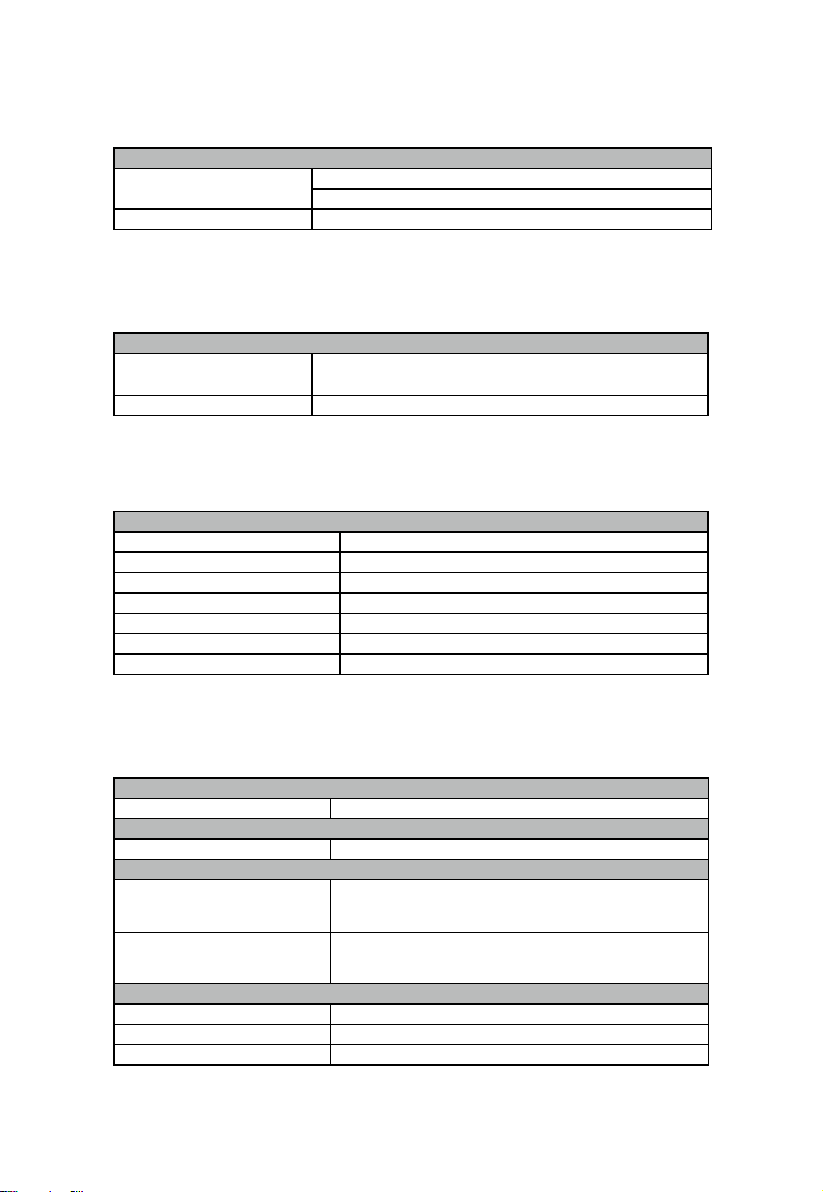

1�3�1 Analog Input ��������������������������������������������������������������������������� 2

1�3�2 Timebase �������������������������������������������������������������������������������� 4

1�3�3 Triggers ����������������������������������������������������������������������������������� 4

1.3.4 General Specicaons ������������������������������������������������������������� 4

1.4 Soware Support ������������������������������������������������������������������������������� 5

1�4�1 SDK ����������������������������������������������������������������������������������������� 5

1�4�2 DSA-DASK�������������������������������������������������������������������������������� 5

1�5 Device Layout and I/O Array��������������������������������������������������������������� 6

2 Geng Started�������������������������������������������������������������������������������������������� 8

2.1 Installaon Environment �������������������������������������������������������������������� 8

2�2 Installing the Module ������������������������������������������������������������������������� 9

3 Operaons �������������������������������������������������������������������������������������������������10

3.1 Funconal Block Diagram������������������������������������������������������������������10

3�2 Analog Input Channel������������������������������������������������������������������������10

3.2.1 Analog Input Front-End Conguraon ������������������������������������10

3�2�2 Input Range and Data Format�������������������������������������������������11

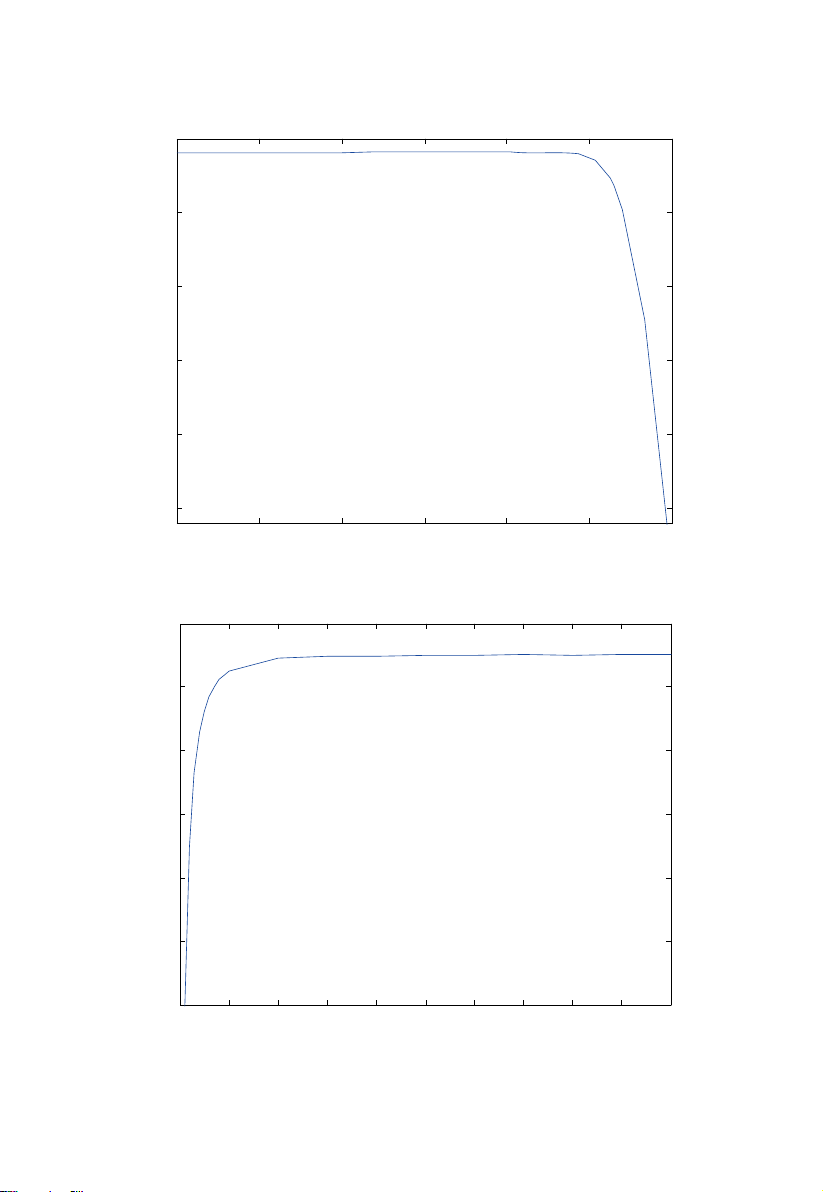

3�2�3 ADC and Analog Input Filter ���������������������������������������������������12

3�2�4 DMA Data Transfer�����������������������������������������������������������������12

3�3 Trigger Source and Trigger Modes������������������������������������������������������14

3�4 Trigger Mode�������������������������������������������������������������������������������������16

3�5 ADC Timing Control ���������������������������������������������������������������������������18

3�5�1 Timebase �������������������������������������������������������������������������������18

3�5�2 DDS Timing vs� ADC����������������������������������������������������������������18

3�5�3 Filter Delay in ADC �����������������������������������������������������������������19

3.6 Synchronizing Mulple Modules �������������������������������������������������������19

3.6.1 SSI_TIMEBASE ������������������������������������������������������������������������20

3�6�2 SSI_SYNC_START ��������������������������������������������������������������������20

3�6�3 SSI_TRIG���������������������������������������������������������������������������������20

Appendix A Calibraon �����������������������������������������������������������������������������������21

A.1 Calibraon Constant �������������������������������������������������������������������������21

A.2 Auto-Calibraon �������������������������������������������������������������������������������21

Important Safety Instrucons ��������������������������������������������������������������������������22