CONTENTS

1. Overview.............................................................................................................................................................4

1.1 Introduction................................................................................................................................................4

1.2 Package Contents .......................................................................................................................................4

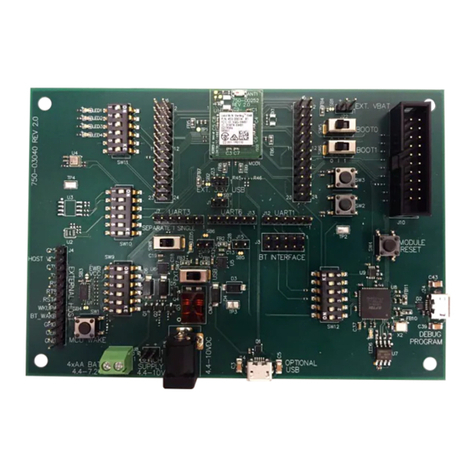

2. M.2 Development Kit –Main Development Board............................................................................................4

1.3 Key Features ...............................................................................................................................................5

1.4 Understanding the Development Board ....................................................................................................6

3. Functional Blocks................................................................................................................................................7

1.5 Pin Definitions ............................................................................................................................................7

1.5.1 M.2 Key-E Socket ................................................................................................................................7

1.5.2 SDIO-Pin Header .................................................................................................................................9

1.5.3 PCIe Golden Finger .......................................................................................................................... 10

1.6 Power Supply........................................................................................................................................... 11

1.7 Tact Switch............................................................................................................................................... 12

1.7.1 PCIE_W_DISABLE_N (SW5).............................................................................................................. 13

1.7.2 PDn (SW6)........................................................................................................................................ 13

1.7.3 PMU_EN (SW7)................................................................................................................................ 14

1.8 4-wire UART Serial Interface ................................................................................................................... 14

1.8.1 UART Mapping................................................................................................................................. 14

1.8.2 UART Interface Driven by USB......................................................................................................... 14

1.8.3 UART Interface Driven by External Source ...................................................................................... 15

1.9 32.768 KHz Oscillator............................................................................................................................... 15

1.10 PCM ......................................................................................................................................................... 16

1.11 LTE Coexistence ....................................................................................................................................... 16

1.12 LED Indicator ........................................................................................................................................... 17

4. Additional Documentation .............................................................................................................................. 17

5. Appendix.......................................................................................................................................................... 17