-3-

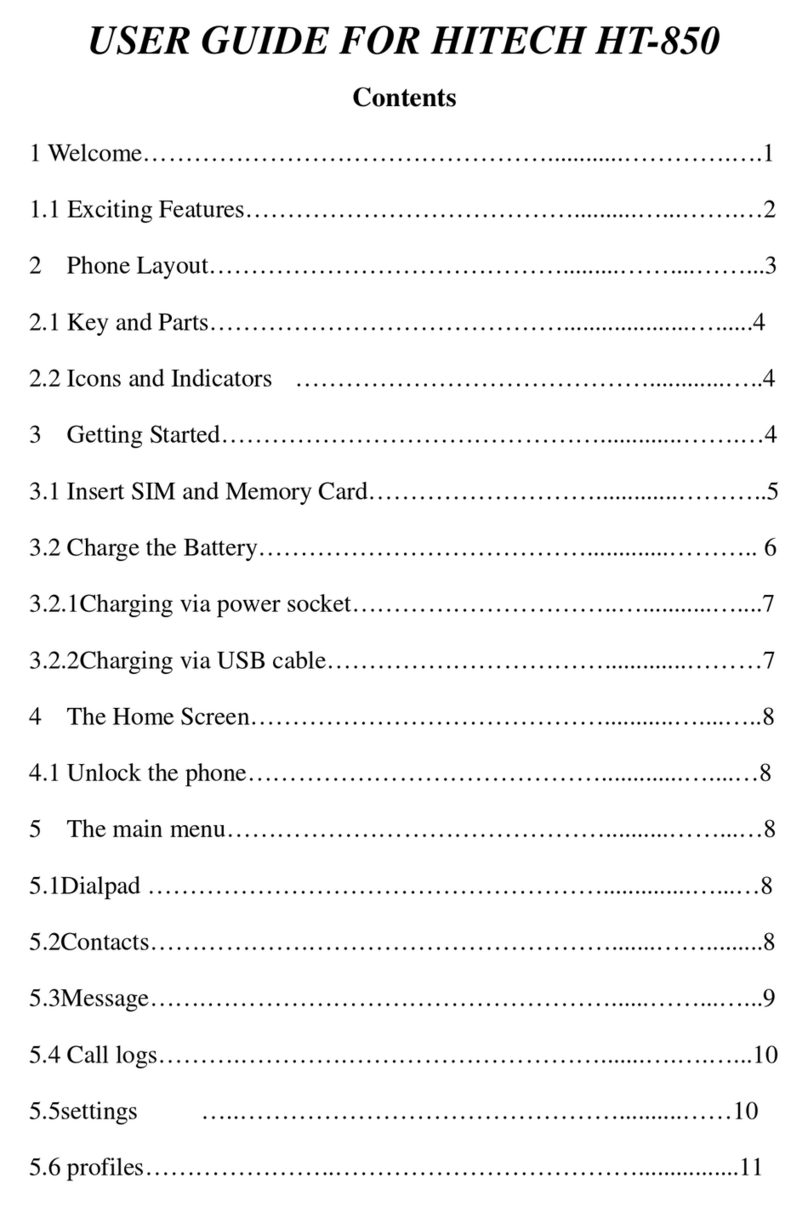

Table of Contents

1. INTRODUCTION.................................. 5

1.1 Purpose ............................................….

1.2 Regulatory Information ..........................

1.3 Abbreviations .........................................

2. General Performance .....................… 8

2.1 Product Name ................................…….

2.2 Supporting Standard ……………………..

2.3 Main Parts …………………………………

2.4 H/W Features …………………………….

2.5 S/W Features …………………………….

3. H/W Circuit Description ....................13

3.1 RF Transceiver General Description ……

3.2 Receiver Part …………………………….

3.3 Digital Baseband (DBB) Processor ………

3.4 Analog Baseband (ABB) Processor …...…

3.5 Camera Circuit ……..………………………

5

5

7

8

8

8

9

11

13

13

20

25

44

4. TROUBLE SHOOTING ................… 51

4.1 Main Components Placement(G5500) ...

Main Components Placement(G7050) ...

4.2 Main Components .....................…..........

4.3 Keypad Components Placement ............

4.4 Baseband Components ..……………..…

4.5 Power On Trouble …..........…………..….

4.6 Charging Trouble ........................…..…..

4.7 LCD Display Trouble ………....................

4.8 Receiver Trouble ………….....................

4.9 Microphone Trouble ………………………

4.10 Vibrator Trouble ……….…………………

4.11 Keypad Backlight Trouble …….…………

4.12 Slide Open/Close Trouble ……….………

4.13 SIM Detect Trouble …….....……………..

51

52

53

54

55

56

57

59

61

65

68

70

72

74

5. ASSEMBLY INSTRUCTION ………....102

5.1 Disassembly (G5500) .............................

5.2 Disassembly (G7050) …........………….

102

108

8. CIRCUIT DIAGRAM .............………... 129

8.1 BB ………..…………….........................

8.2 MEMORY, etc. …………………………….

8.3 MIDI, AUDIO ………….………………….

8.4 I/O, Connector ……….…………….……

8.5 RF ………………………..….……..…….

8.6 CAMERA ………………………………...

8.7 KEYPAD ………………………………….

129

130

131

132

133

134

135

6. DOWNLOAD ……………………...……114

6.1 Download Setup .....................................

6.2 Download Procedure ………...….……….

114

115

7. SERVICE AND CALIBRATION …….. 122

4.14 Earphone Trouble ……….……………….

4.15 Infrared Data Association Trouble ……

4.16 Camera Trouble ………………………….

76

81

84

7.1 Service S/W ……....................................

7.2 Calibration ……………….…...….……….

122

125

9. PCB LAYOUT .............……………..... 137