5

Page:

4

HKADC[5] - VBATT_TEMP

PMIC_AUXIN[1]

Value fixed

3

C

8

LG ELECTRONICS INC.

8-bit, NAND boot

8

6

E

150K : 150K : 1.30V

1%

PCB_Rev_ADC

MODE

150K : 100K : 1.04V

C

Size:

98

1110

150K : 680K : 2.13V

MFG ENGR CHK:

USB 48M CLK

150K : 10K : 0.016V

Near to B18 (VDD_PLL)

Normal boot

1

H

for VSS_THERMAL

MOBILE HANDSET R&D CENTER

DEVELOPMENT LAB 4 DEVELOPMENT GROUP 1

9

H

D

BOOT_MODE3

Changed by:

150K : 750K : 2.17V

6

JH Park

E

0

1

4

G

Size:

Engineer:

B

5

G

16-bit, NAND boot

5

Engineer:

7

D

C

10

DOC CTRL CHK:

12

JH Park

QA CHK:

3

(VDD_DAC_REF)

1 7

PMIC_AUXIN[2] - PA_THERM

Time Changed:

F

1%

2

Changed by:

150K : 300K : 1.73V

150K : 470K : 1.97V

B

3

TITLE:

10%

(CAD : 10uF=>Input MSMA_2.6V)

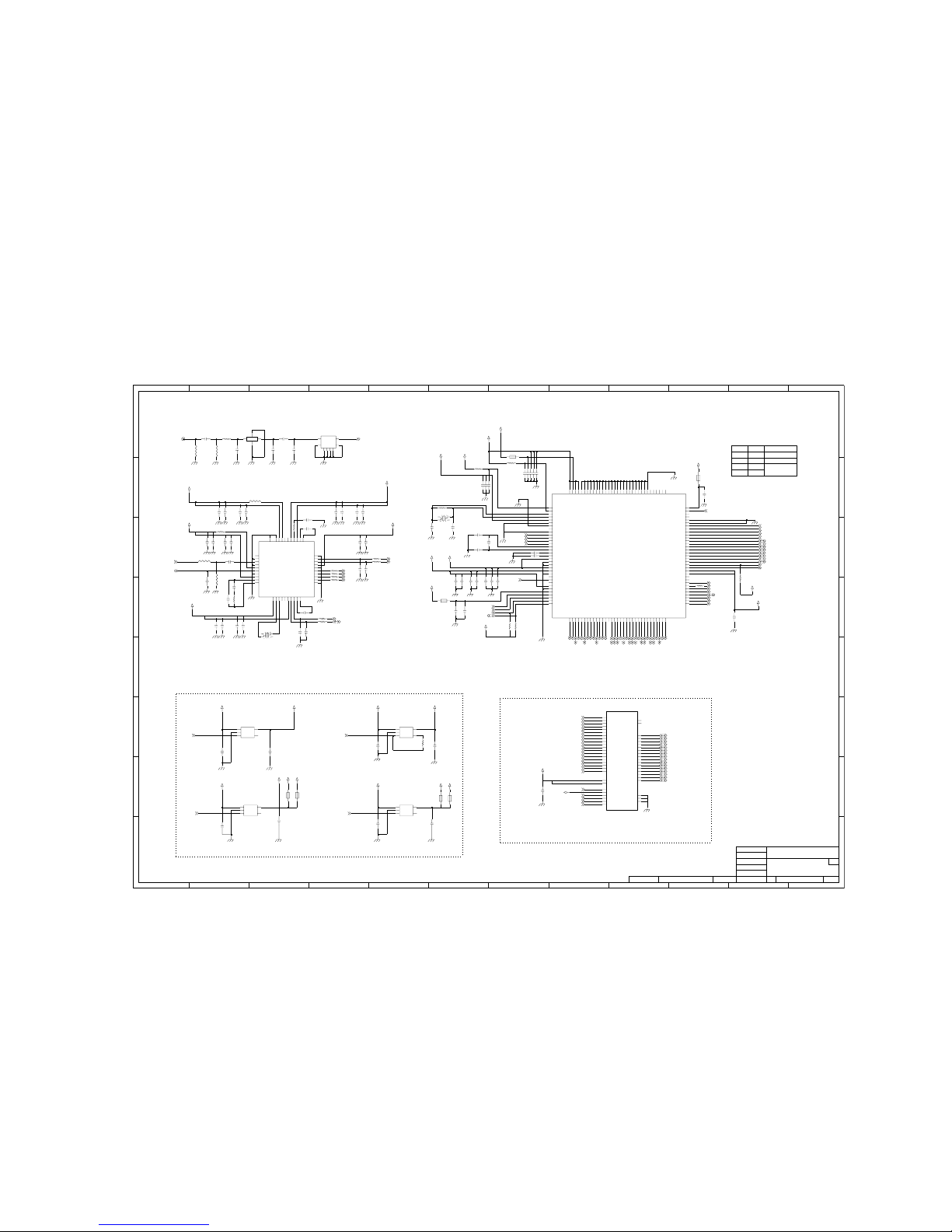

HKADC(4):PCB_Rev_ADC

11

150K : 47K : 0.62V

5

D12(VDDA1) and F12(DAC_REF)

w18 (Analog VSS guard ring for CODEC)

Date Changed:

1

MFG ENGR CHK:

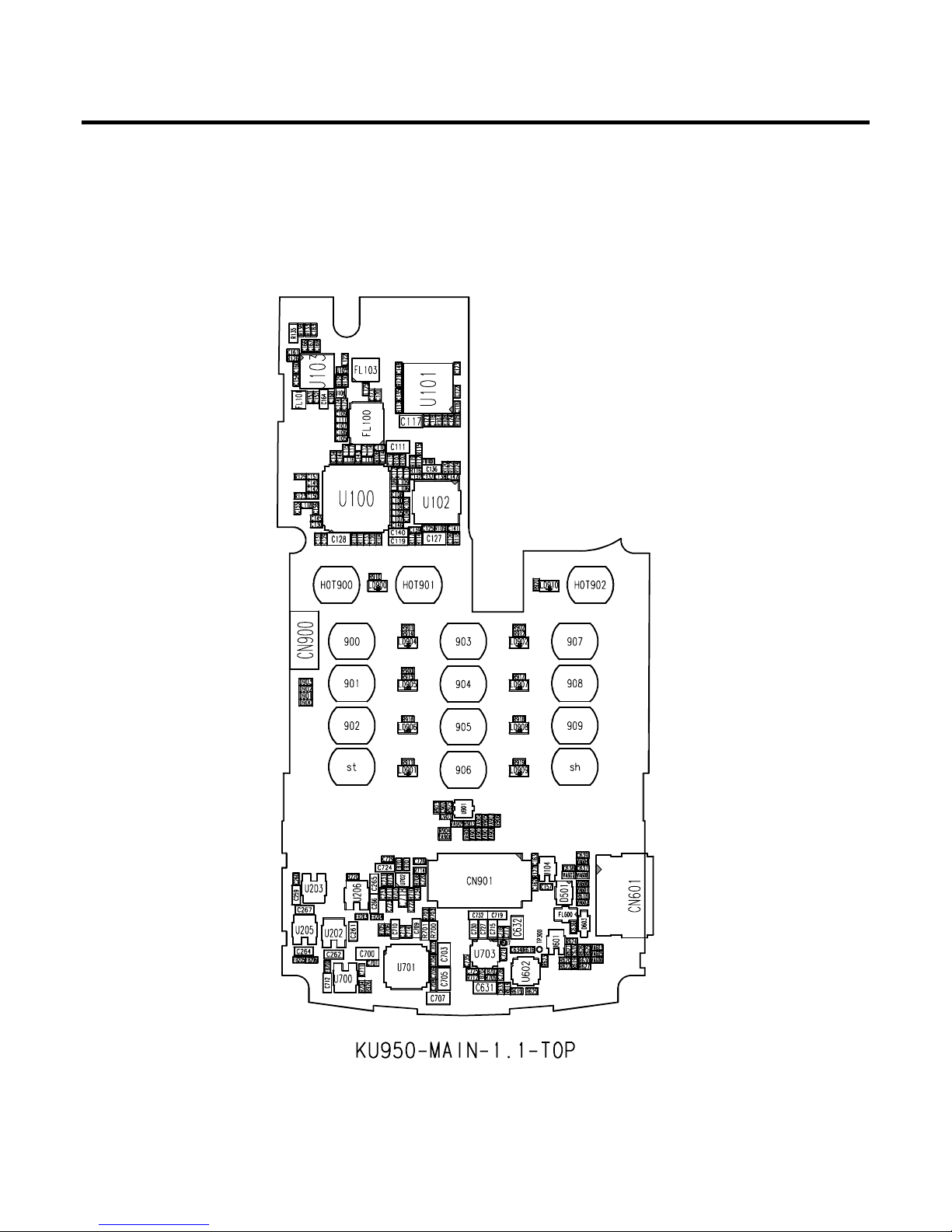

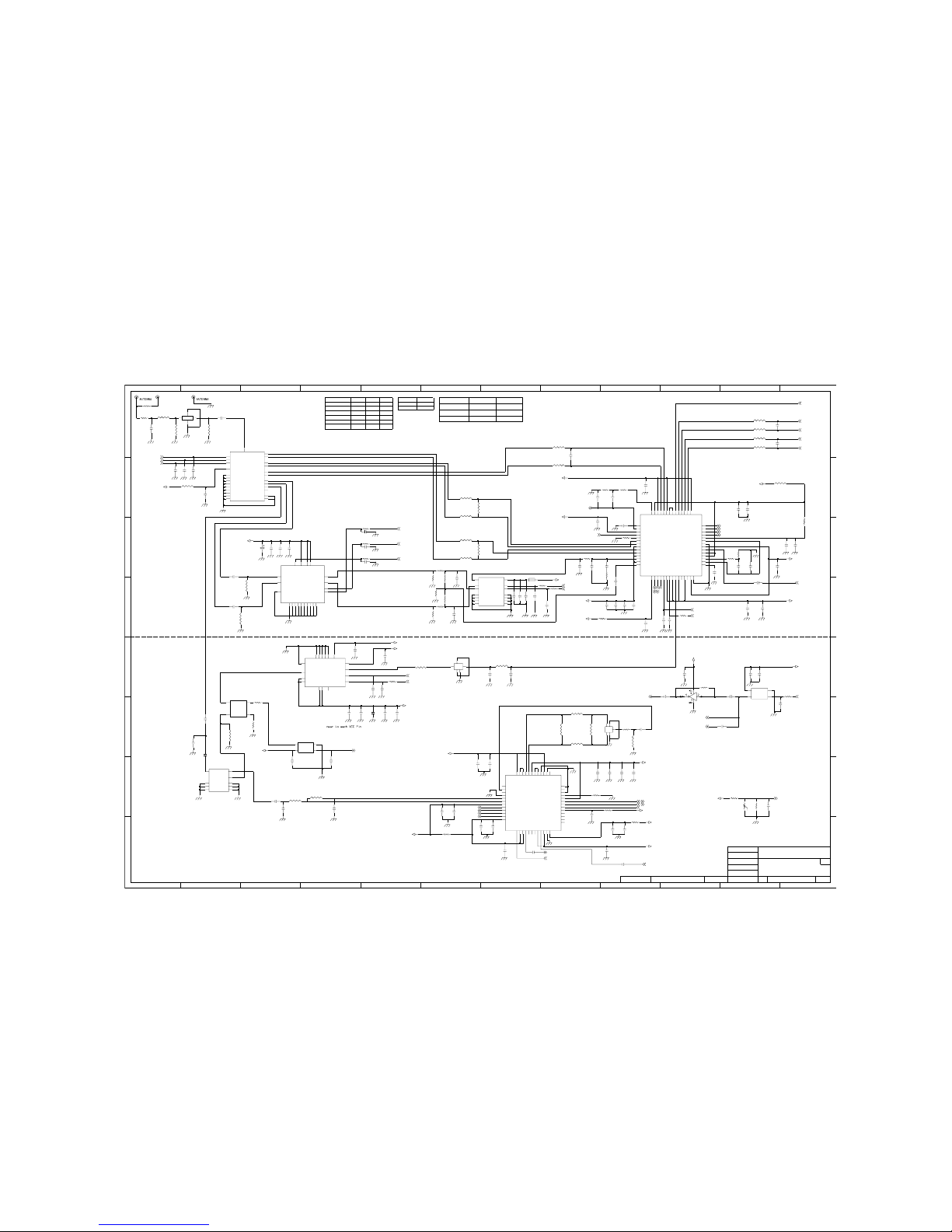

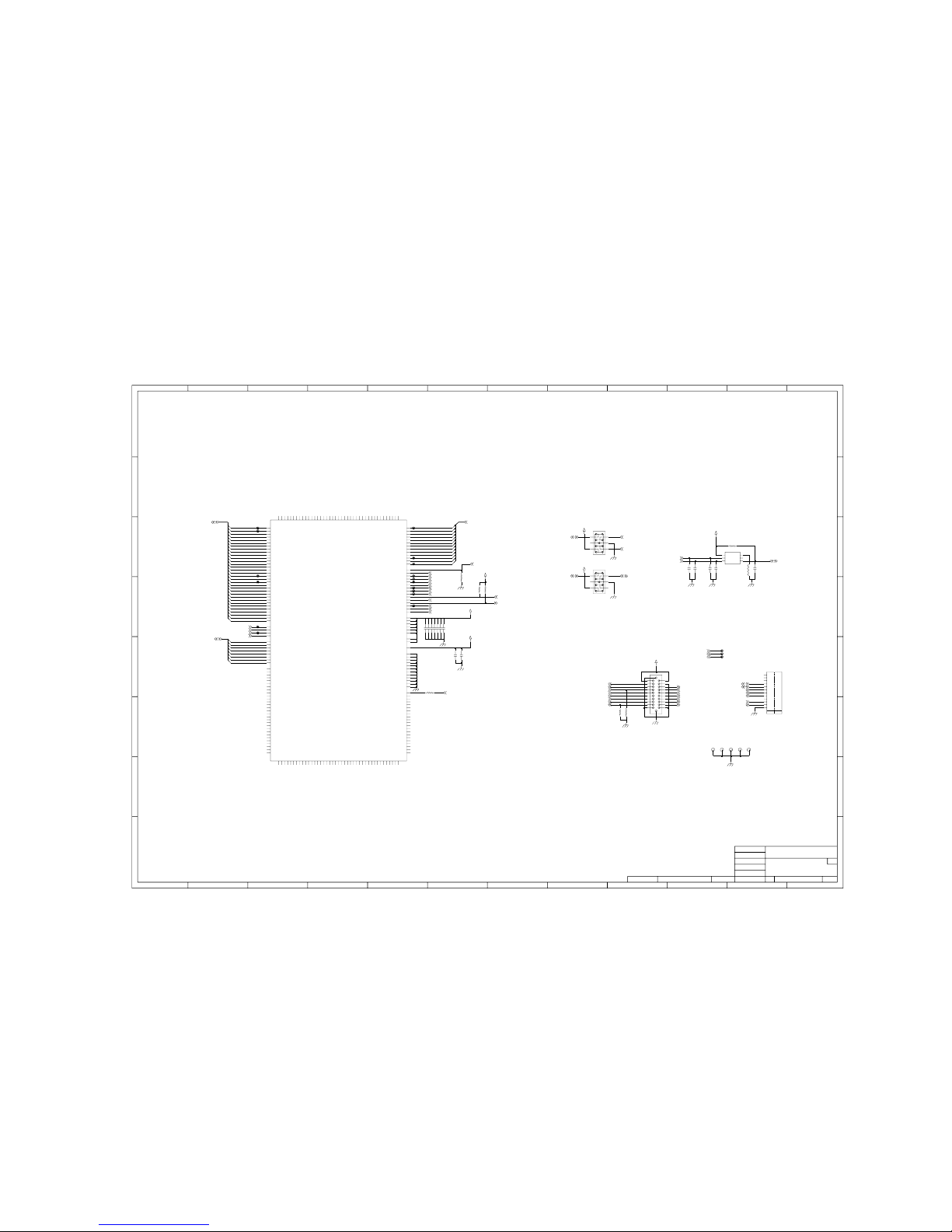

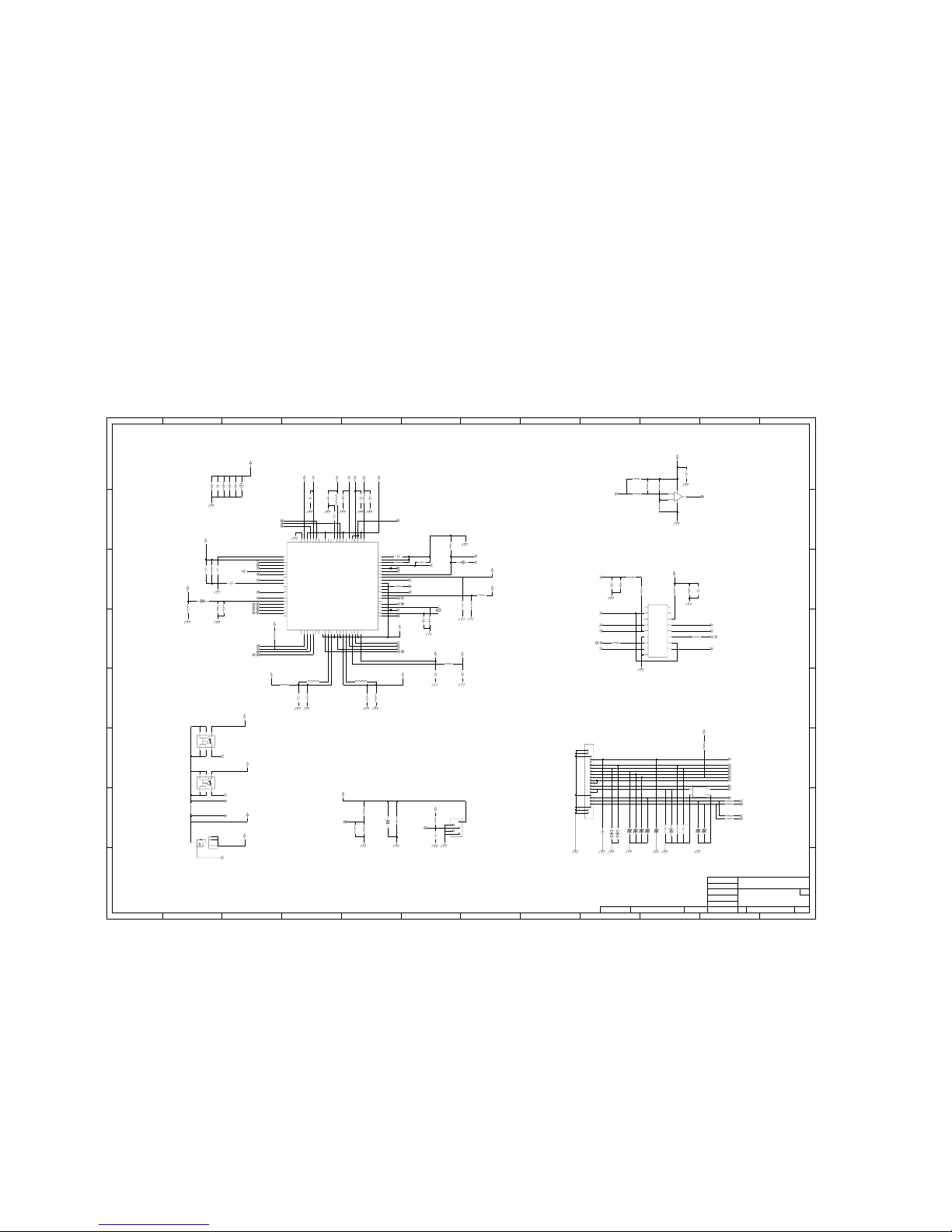

KU950 Main 1.1

HKADC[0] - AMUX_OUT

HKADC[1] - VBATT_SENSE

HKADC[2] - HDET1

HKADC[3] - REMOTE_ADC

E

6

A

ADC

HKADC[4] - PCB_Rev_ADC

3

Time Changed:

C

G

2 10

2200p cap => place between

7

( Default Pull-Down)

A

Date Changed: QA CHK:

(PLLOUT_TEST)

H

Drawn by:

1 1

12

12

Native, ARM JTAG

11

0 1 0

B

6

A

Page:

BOOT_MODE2 BOOT_MODE

0 1

150K : 68K : 0.81V

A

11

Drawn by:

DOC CTRL CHK:

G

R&D CHK:

0 0 0

F

B

D

A2

Native, MSM JTAG

4

X 0

H

D

MODE2 MODE1 MODE0

4

REV:

Trusted boot

Drawing Number:

109

NOR boot

Near to MSM

TITLE:

7

REV: Drawing Number:

2 129

12

R&D CHK:

8

E

FF

2006, Sep 08

3/9

A2

JH Park 10:49:00 am

0R316

C336

2200p

0.1u

C348

1000p

C337

VREG_MSMP_2.7V

R304

51K

TP303

NA

R320

100KR313

C339

1000p

C341

0.01u

R317 0

1000p

VREG_MSME_1.8V

C338

C333

0.01u

0.01u

C315

100KR310

C345

0.1u

C344

1000p

C322

0.01u

C323

0.01u

L300

100nH

180K

R308

C303 22n

R321

NA

0.1uC311

C310 0.1u

R324

2.2K

0.1u

C347C346

0.1u

C342

1000p

R311

0.01u

NA

C330

R319

100K

R303

180K

R309 100K

100K

R322

R302

150K

C332

0.01u

C343

VREG_MSMP_2.7V

VREG_MSMP_2.7V

TP302

1000p

C340

1000p

C306 0.015u

R307

10K

0.1u

C350

NA

C309

C301 0.1u

1000p

VREG_MSMP_2.7V

10K

R305

C327

2.2K

R323

470KR306

C302 0.1u

VREG_MSMA_2.6V

TP306

0.1u

C335

A24

F1 VSS_PAD1_0

K1 VSS_PAD1_1

M1 VSS_PAD1_2

VSS_PAD1_3

R1

VSS_PAD1_4

U1

AF6 VSS_PAD2_0

VSS_PAD2_1

AF11

VSS_PAD2_2

AF15

R26 VSS_PAD3_0

B17 VSS_PAD3_1

A15 VSS_PAD3_2

A9 VSS_PAD3_3

VREG_MSME_1.8VVREG_MSMC_1.375V

VSSA6

V26 VSSA7

VSSA8

W16

W18 VSSA9

C1

VSS_DIG_0 H1

VSS_DIG_1

VSS_DIG_10 A14

A11

VSS_DIG_11 A5

VSS_DIG_12

VSS_DIG_2 W1

VSS_DIG_3 AC1

AF8

VSS_DIG_4 AF16

VSS_DIG_5 T26

VSS_DIG_6

VSS_DIG_7 G26

VSS_DIG_8 D26

VSS_DIG_9

B2

B25 VSS7

VSS8

B26

VSS9

D4

VSSA1

A18

W26 VSSA10

AB26 VSSA11

VSSA12

AC16

AC26 VSSA13

VSSA14

AD25

VSSA15

AF23

AF24 VSSA16

A21 VSSA2

VSSA3

D13

VSSA4

D19

P26 VSSA5

U19

W8

W19 VSS39

VSS4

A26

VSS40 AA6

VSS41 AA21

VSS42 AC4

AC23

VSS43

VSS44 AE1

AE2

VSS45

VSS46 AE25

AE26

VSS47

VSS48 AF1

AF2

VSS49

B1 VSS5

VSS50 AF25

AF26

VSS51

VSS6

N12

N13 VSS24

VSS25

N14

VSS26

N15

VSS27

P12

P13 VSS28

VSS29

P14

A25 VSS3

P15 VSS30

VSS31

R12

R13 VSS32

VSS33

R14

R15 VSS34

VSS35

R16

T11 VSS36

VSS37

T16

VSS38

B18

A1 VSS1

VSS10

D23

F6 VSS11

F21 VSS12

H8 VSS13

VSS14

H19

VSS15

K10

L11 VSS16

VSS17

L16

M11 VSS18

VSS19

M12

VSS2

A2

M13 VSS20

VSS21

M14

M15 VSS22

VSS23

VDD_DIG_8

VDD_DIG_9 B24

B21

VDD_MDDI

F2

VDD_PAD1_0

VDD_PAD1_1 K2

M2

VDD_PAD1_2 R2

VDD_PAD1_3 U2

VDD_PAD1_4

AE6

VDD_PAD2_0

VDD_PAD2_1 AE11

VDD_PAD2_2 AE15

VDD_PAD3_0 R25

VDD_PAD3_1 K25

B15

VDD_PAD3_2 B9

VDD_PAD3_3

A3

VDD_PAD4_0

VDD_PLL

VDDA5 AA26

VDDA6

VDDA7 AE23

VDDA8 AE24

AA16

VDDA9

VDD_DIG_0 C2

VDD_DIG_1 H2

VDD_DIG_10 B14

B11

VDD_DIG_11 B5

VDD_DIG_12

W2

VDD_DIG_2 AC2

VDD_DIG_3 AE8

VDD_DIG_4 AE16

VDD_DIG_5

VDD_DIG_6 T25

G25

VDD_DIG_7 D25

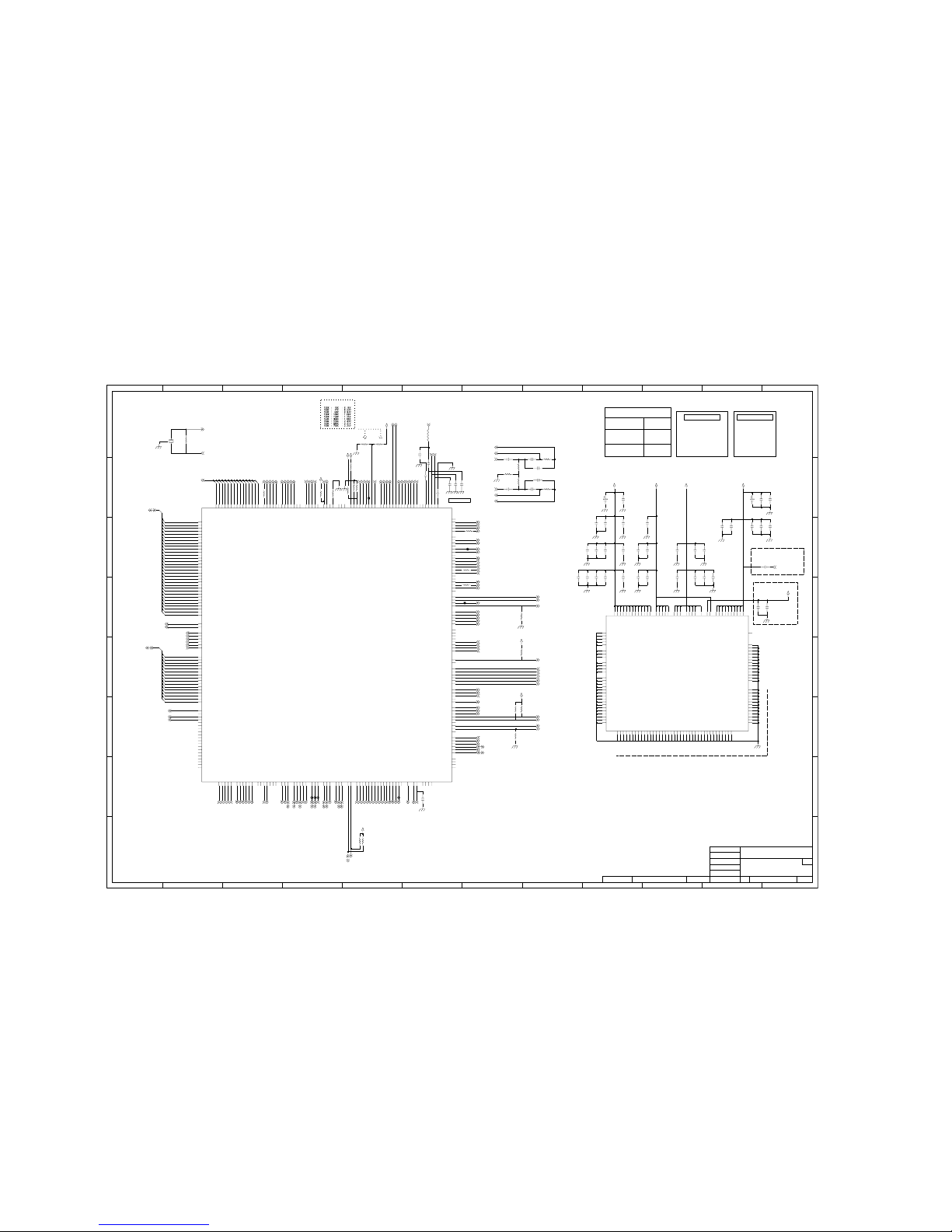

MSM6275_B

U300-2

RESERVED C26

D12

VDDA1

VDDA10 AF17

P23

VDDA2

VDDA3 U25

U26

VDDA4 Y26

TP301

C325

0.1u

10p

C300

C317

0.1u

C316

C320

0.1u

TP305

0.01u

C307

C319

NA

0.01u

C328

1000p

C321

0.1u

VREG_MSMP_2.7V

C313

10u

0.015uC305

C334

51R312

0.1u

R314 NA

TP304

NAR315

2

48MHz

ICRT20S48M0X514CR X300

13

R300

1M

XMEM2_CS_N2_GPIO35

XMEM2_CS_N3_GPIO36 AA15

0.01u

C318

USB_RX_DATA_GPIO29

N23 USB_SE0_VM

USB_XTAL48_IN A10

USB_XTAL48_OUT B10

WDOG_EN AE17

H25

WDOG_STB_SBCK1_GPIO0

WE1_N_SDRAM1_WE_N U8

AF4 WE2_N

W6

XMEM1_CS_N0

XMEM1_CS_N1_GPIO76 AA1

XMEM1_CS_N2_SDRAM1_CS_N0 Y4

Y6

XMEM1_CS_N3_SDRAM1_CS_N1_GPIO77

AA2

XMEM1_HWAIT_N

K8

XMEM1_LWAIT_N_SDRAM1_CAS_N

XMEM2_CS_N0

W14

AC15 XMEM2_CS_N1

W15

P16

M23 UART1_DP_RX_DATA_GPIO96

L26 UART1_DP_TX_DATA_GPIO95

UART1_RFR_N_PA_POWER_CTL_M_GPIO98

P21

UART2_CTS_N_GPIO90

G6

UART2_DP_RX_DATA_GPIO89 H6

E4 UART2_DP_TX_DATA_GPIO88

F4 UART2_RFR_N_GPIO91

L23 UART3_CTS_N_GPIO86

UART3_DP_RX_DATA_GPIO85

M21

M19 UART3_DP_TX_DATA_GPIO84

UART3_RFR_N_GPIO87 L25

M6

UB1_N_SDRAM1_DQM1

AF10 UB2_N

N26 USB_DAT_VP

USB_OE_TP_N

N25

N19

SDRAM1_D9

SLEEP_XTAL_IN A16

SLEEP_XTAL_OUT B16

SYNTH0_GP_PDM0_GPIO92 F18

SYNTH1_GPIO41

H23

SYNTH2_GPIO65 B6

D16

TCK

D18

TCXO

F19

TCXO_EN_GPIO94

TDI D15

A17

TDO

F15

TMS

L13

TRK_LO_ADJ

TRST_N H15

TX_AGC_ADJ H13

H12

TX_ON_GRFC10

UART1_CTS_N_GPIO97

SDRAM1_D22

SDRAM1_D23

W4 SDRAM1_D24

R4

R6 SDRAM1_D25

SDRAM1_D26

T1

T2 SDRAM1_D27

SDRAM1_D28

R8 SDRAM1_D29

T4

D1 SDRAM1_D3

T6 SDRAM1_D30

SDRAM1_D31

T8

SDRAM1_D4

AB4 SDRAM1_D5

J6 SDRAM1_D6

G2

H4 SDRAM1_D7

SDRAM1_D8

P4

J4

N4

SDRAM1_D0

E2 SDRAM1_D1

D2

SDRAM1_D10

J2 SDRAM1_D11

K6

J1 SDRAM1_D12

K4 SDRAM1_D13

SDRAM1_D14

L8

L6 SDRAM1_D15

U6 SDRAM1_D16

SDRAM1_D17

V4

R11 SDRAM1_D18

E1 SDRAM1_D19

AB2 SDRAM1_D2

SDRAM1_D20

Y1

Y2 SDRAM1_D21

V6

A12

F13

RESIN_N F11

RESOUT_N

RESOUT_N_EBI1 AA4

L19 RINGER_GPIO18

G1

ROM1_ADV_N_SDRAM1_RAS_N

ROM1_CLK_SDRAM1_CLK AB1

H16

RTCK

SBCK

L21 SBDT

J23

SBDT1_GPIO1 F26

SBST

H26

H18

SBST1_GPIO93

F25

SDCC_DAT1_GPIO99

SDCC_DAT2_GPIO100 M25

M26

SDCC_DAT3_GPIO101

SDRAM1_CLK_EN

MMC_CMD_GPIO30

MMC_DATA_SDCC_DAT0_GPIO32

L14

Y23

MODE0

U23

MODE1

MODE2 T21

NAND2_FLASH_READY_GPIO33

T14

V2

OE1_N

OE2_N

AF7

F17

PA_ON0

PA_ON1_GPIO2 H11

PA_POWER_CTL

P25

Q_IM_CH0 AA25

W23

Q_IM_CH1

Q_IP_CH0 Y25

V23

Q_IP_CH1

Q_OUT B12

Q_OUT_N

MDDIH_STBN

MDDIH_STBP

A20

AD2

MDP_VSYNC_PRIMARY_GPIO105

MDP_VSYNC_SECONDA_GPIO104 AE3

AF20

MIC1N AE20

MIC1P

MIC2N AF21

AF22

MIC2P

T15

MICBIAS

MICFBN AC22

AC21

MICFBP AC19

MICINN

MICINP AC20

AA18

MICOUTN

MICOUTP AA19

MMC_CLK_SDCC_CLK_GPIO31

M16

H14

I_OUT_N

KEYSENSE0_N_GPIO62

R21

P19 KEYSENSE1_N_GPIO63

D14 KEYSENSE2_N_GPIO46

R23 KEYSENSE3_N_GPIO47

KEYSENSE4_N_GPIO48

U21

L2

LB1_N_SDRAM1_DQM0

AE10 LB2_N_A2_0

AF14 LCD_CS_N_GPIO38

LCD_EN_GPIO37 AE13

A23

MDDIC_DATN

MDDIC_DATP A22

B23

MDDIC_STBN

MDDIC_STBP B22

B19 MDDIH_DATN

MDDIH_DATP

B20

A19

GSM_PA_DAC_REF

HKAIN0 V21

AA23

HKAIN1

HKAIN2 W21

V19

HKAIN3

HKAIN4 Y21

AB23

HKAIN5

W17

HPH_L

HPH_R AA17

I2C_SCL_GPIO27

N16 I2C_SDA_GPIO26

K21

I_IM_CH0 AB25

I_IM_CH1 V25

I_IP_CH0 AC25

I_IP_CH1 W25

B13

I_OUT

A13

GPIO52

GPIO53

L12

GPIO64

F14

GPIO66 F8

GP_PDM1_PA_RANGE0 H17

GP_PDM2_PA_RANGE1 D17

GRFC0_GPIO3 B8

GRFC1_AUX_SBDT_GPIO4 A8

GRFC2_GPIO5 D9

GRFC3_GPIO6 F10

H10

GRFC4_AUX_SBCK_GPIO7

GRFC5_AUX_SBST_GPIO8 D11

T23

GRFC7_GPIO10

GRFC8_GPIO11 B4

GRFC9_GPIO12 D5

T19

GRFX6_GPIO9

AD26

D2_9

DAC_REF F12

AE18

EAR1ON AF18

EAR1OP

K26 GPIO17

G21 GPIO19

GPIO28 A6

F7 GPIO39

D6 GPIO40

GPIO42

D7

GPIO43 H9

D8 GPIO44

GPIO45

A4

F9 GPIO49

B7 GPIO50

A7 GPIO51

D10

CCOMP

AC5 D2_0

D2_1

AF3

D2_10

AC8 D2_11

AE7 D2_12

AA9 D2_13

W10

AC9 D2_14

AA10 D2_15

AE4 D2_2

D2_3

AC6 D2_4

AE5 D2_5

AA7 D2_6

AF5

AC7 D2_7

AA8 D2_8

W9

F23

H21

BT_TX_RX_N_GPIO21

J21

CAMCLK_PO_GP_MN_GPIO13

J25 CAMIF_DATA0_GPIO83

CAMIF_DATA1_GPIO81

J26

CAMIF_DATA2_AUX_TRST_N_GPIO54

D21

C25 CAMIF_DATA3_AUX_TCK_GPIO55

D22 CAMIF_DATA4_AUX_TMS_GPIO56

CAMIF_DATA5_AUX_TDI_GPIO57

J19

L15 CAMIF_DATA6_AUX_TDO_GPIO58

D20 CAMIF_DATA7_GPIO59

CAMIF_DATA8_GPIO60

F16 CAMIF_DATA9_GPIO61

F20

CAMIF_HSYNC_GPIO15

E23

K23 CAMIF_PCLK_GPIO82

B3 CAMIF_VSYNC_GPIO16

AA20

A2_9

AUXIN AF19

AUXIP AE19

AUXON_AUXOR AC18

AC17

AUXOP_AUXOL

K19

AUX_PCM_CLK_GRFC14_GPIO80

AUX_PCM_DIN_GRFC13_GPIO14 N21

G4

AUX_PCM_DOUT_GRFC12_GPIO103 J8

AUX_PCM_SYNC_GRFC11_GPIO102

BOOT_MODE AE21

AE22

BOOT_MODE2

BOOT_MODE3 AD1

BT_CLK_GPIO25 G23

R19

BT_DATA_GPIO20

BT_SBCK_GPIO23 E26

E25

BT_SBDT_GPIO22

BT_SBST_GPIO24

A2_12

A2_13

AA13

AC13 A2_14

W13 A2_15

AE14 A2_16

A2_17

AC14

T13 A2_18

AA14 A2_19

A2_2

AF9

A2_20_GPIO34

AF13

W11 A2_3

A2_4

AC10 A2_5

AA11

AC11 A2_6

A2_7

T12 A2_8

W12

AA12

P8

P11

A1_14

A1_2 L4

A1_23_SDRAM1_DQM2_GPIO78 U4

A1_24_GPIO79 V1

A1_25_SDRAM1_DQM3_GPIO75 V8

A1_3 M8

A1_4 M4

N11

A1_5

A1_6 N8

N6

A1_7 N2

A1_8

A1_9 N1

A2_1

AE9

A2_10

AC12

AE12 A2_11

AF12

MSM6275_A

U300-1

A1_1 L1

A1_10 P1

P2

A1_11 P6

A1_12

A1_13

VREG_MSMA_2.6V

NA

C308

1000p

C329

0.1u

C324

VREG_MSMP_2.7V

C349

0.01u

VREG_MSMP_2.7V

0.1u

C326

0.1u

C314

NA

R318

TP300

R301

300K

4.7u

C312

C304 22n

RMT_INT_MSM

MM_LCD_VSYNC

HOOK_SENSE_H

LCD_IF_MODE_1

FLASH_LED_CTRL

CAM_SYSCLK C331

0.01u

SPK_AMP_EN

USB_XTAL_OUT

USB_XTAL_IN

MC_IO_OFF

LCD_IF_MODE_0

AV_SENSE_N

UART_TXD

DAC_REF

RMT_ADC_MSM

EAR_MIC_P_MSM

RECEIVER+

RECEIVER-

TCC_RESET_N

JTAG_TDO

I2C_SDA

I2C_SCL

VGA_I2C_EN

USB_XTAL_IN

GSM_PA_PWR_CTL_REF

EBI2_ADDR[2]

EBI2_ADDR[1]

CAM_DUAL_LDO_EN

SDRAM_CLK

GSM_TX_VCO_1_EN_N

GSM_TX_VCO_0_EN_N

GSM_PA_EN

MMC_CMD

OPT_R

OPT_L

MIC1P

MIC1N

EBI2_DATA[0:15]

EBI2_DATA[15]

SDRAM_DATA[0:31]

SDRAM_DATA[31]

TCC_HOST_CS_N

MSM_LCD_ADS_N

UART_RXD

VC_IO_OFF

DAC_REF

LCD_BL_CTRL

LCD_BYPASS_ENABLE

PA_R0

MSM_LCD_RESET_N

NAND_CLE

MICBIAS

MICINN

NAND_READY

EBI2_DATA[1]

EBI2_DATA[12]

EBI2_DATA[7]

EBI2_DATA[5]

NAND_ALE

MICFBN

MICFBP

V_CAM_RESET_N

EBI2_DATA[0]

VBAT_SENSE

VBAT_TEMP

EBI2_DATA[10]

EBI2_DATA[8]

EBI2_DATA[3]

AMUX_OUT

MICOUTP

KEY_COL[2]

KEY_COL[5]

CAM_VSYNC

CAM_DATA[2]

CAM_DATA[6]

TCC_PWR_EN

BUFF_TCXO

SLEEP_CLK

TX_IM

TX_QM

GSM_PA_BAND

PS_HOLD

PM_INT_N

BT_DATA

CAM_PCLK

CAM_DATA[0]

CAM_DATA[5]

CAM_DATA[7]

JTAG_TCK

JTAG_TDI

MMC_CLK

KEY_COL[1]

USIM_DATA

KEY_COL[3]

ANT_SEL2

CAM_DATA[1]

CAM_DATA[4]

PA_ON

TX_IP

TX_QP

USB_XTAL_OUT

EBI2_DATA[14]

EBI2_OE_N

EBI2_DATA[6]

EBI2_WE_N

EBI2_DATA[2]

MICINP

TCC_CS_N

EBI2_DATA[13]

EBI2_DATA[11]

EBI2_DATA[4]

SWIVEL_DETECT

SDRAM_DATA[3]

SDRAM_DATA[7]

SBST

SDRAM_CLK_EN

JTAG_RTCK

JTAG_TRST_N

TRK_LO_ADJ

MMC_DATA

RF_ON_TX_ON

KEY_COL[0]

SDRAM_DATA[8]

USIM_RST_N

SDRAM_DATA[2]

BT_CLK

BT_TX_RX_N

SDRAM_DATA[6]

SDRAM_RAS_N

KEY_COL[4]

SDRAM_DATA[0]

BT_SBST

CAM_DATA[3]

TCXO_EN

JTAG_TMS

RESET_IN_N

RESOUT_N

USIM_CLK

BT_SBCK

BT_SBDT

CAM_HSYNC

SDRAM_DATA[1]

M_CAM_RESET_N

USB_OE_N

USB_DAT

SDRAM_ADDR[8]

USB_SE0

SDRAM_ADDR[5]

SDRAM_ADDR[9]

SDRAM_ADDR[3]

SDRAM_DQM[1]

SDRAM_ADDR[4]

PM_SBCK

SDRAM_DATA[14]

SDRAM_DATA[15]

SDRAM_ADDR[2]

HP_AMP_EN

PM_SBDT

PM_SBST

SDRAM_DQM[0]

TX_AGC_ADJ

SDRAM_ADDR[1]

SDRAM_CAS_N

SDRAM_DATA[11]

SDRAM_DATA[13]

MMC_CD

SBCK

SDRAM_DATA[4]

SDRAM_DATA[5]

SDRAM_DATA[9]

TCC_INT

SBDT

SDRAM_DATA[10]

SDRAM_DATA[12]

SDRAM_DATA[18]

SDRAM_DQM[3]

SDRAM_DATA[22]

SDRAM_DATA[17]

RX_IM

SDRAM_ADDR[0]

SDRAM_WE_N

SDRAM_DATA[16]

SDRAM_DQM[2]

SDRAM_DATA[30]

SDRAM_DATA[29]

ANT_SEL1

SDRAM_DATA[27]

EAR_SENSE_N

SDRAM_DATA[26]

SDRAM_DATA[28]

SDRAM_DATA[25]

SDRAM_DATA[24]

KEY_ROW[3]

KEY_ROW[4]

ANT_SEL0

SDRAM_ADDR[13]

SDRAM_ADDR[12]

GSM_PA_RAMP

KEY_ROW[0]

SDRAM_ADDR[11]

KEY_ROW[1]

KEY_ROW[2]

SDRAM_ADDR[14]

SDRAM_ADDR[10]

SDRAM_ADDR[6]

SDRAM_ADDR[7]

SDRAM_ADDR[0:14]

MICOUTN

MICOUTP

MICINP

MICFBN

MICINN

MICFBP

SDRAM_CS_N

RX_QP

RX_QM

HDET1

SDRAM_DATA[21]

SDRAM_DATA[20]

EBI2_DATA[9]

SDRAM_DATA[23]

RX_IP

SDRAM_DATA[19]

MICOUTN

HEADSET_L

HEADSET_R

NAND_CS_N