NAT-MCH HUB-Module PCIe –Technical Reference Manual

Version 1.2 © N.A.T. GmbH 4

Table of Contents

DISCLAIMER ....................................................................................................... 3

TABLE OF CONTENTS .......................................................................................... 4

LIST OF TABLES .................................................................................................. 5

LIST OF FIGURES................................................................................................ 5

CONVENTIONS.................................................................................................... 6

1INTRODUCTION ........................................................................................... 7

2OVERVIEW ................................................................................................... 8

2.1 MAJOR FEATURES......................................................................................... 8

2.2 BLOCK DIAGRAM ......................................................................................... 9

2.3 LOCATION DIAGRAM ....................................................................................10

3BOARD FEATURES ...................................................................................... 11

3.1 PCI EXPRESS SWITCH PLX PEX8748 ...............................................................11

3.2 MICROCONTROLLER .....................................................................................13

3.3 FPGA .....................................................................................................13

3.4 MULTIPLEXING UNITS ...................................................................................13

3.5 PCIE INTERFACES .......................................................................................13

3.6 INTERFACE TO NAT-MCH BASE-MODULE ..........................................................13

3.7 INTERFACE TO NAT-MCH CLK-MODULE ............................................................13

4HARDWARE ................................................................................................ 14

4.1 LEDS......................................................................................................14

4.2 CONNECTORS ............................................................................................15

4.2.1 CON1: AMC Connector to 3rd tongue ...................................................16

4.2.2 CON2: AMC Connector to 4th tongue ...................................................18

4.2.3 CON3: Connector to NAT-MCH CLK/BASE-Module .................................20

4.2.4 JP1: JTAG programming interface .......................................................20

4.2.5 J1: Connector to optional Root-Complex..............................................21

5PROGRAMMING NOTES .............................................................................. 22

5.1 SPI INTERFACE ..........................................................................................22

5.1.1 SPI-Interface –Default mode.............................................................22

5.1.2 SPI-Interface –Update mode .............................................................22

5.2 I²C INTERFACE ..........................................................................................22

5.3 REGISTER.................................................................................................22

5.3.1 Board Identifier Register ...................................................................22

5.3.2 PCB Revision Register .......................................................................23

5.3.3 Atmel Version ..................................................................................23

6BOARD SPECIFICATION ............................................................................. 24

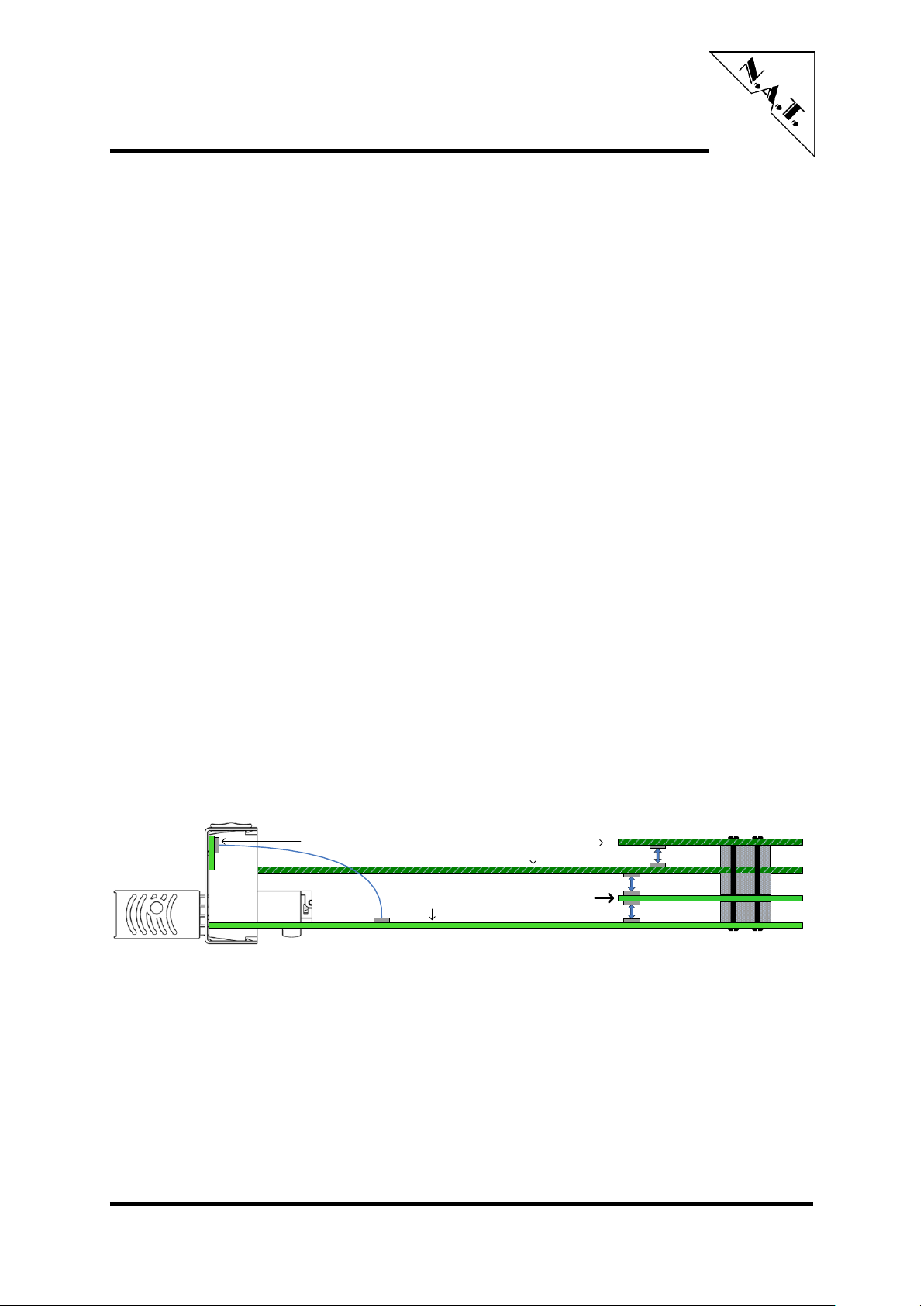

7INSTALLATION .......................................................................................... 25

7.1 SAFETY NOTE ............................................................................................25