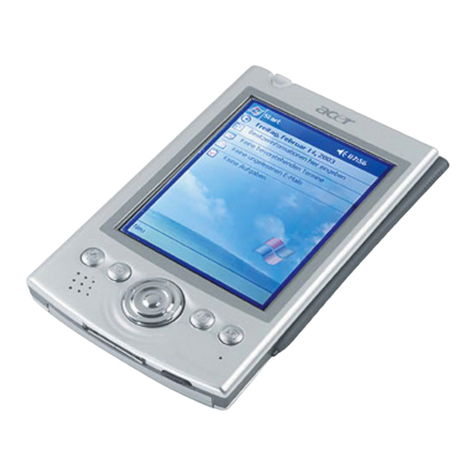

Barracuda PDA Maintenance

8

The SA-1110 consists of the following functional blocks:

• Processing Core

The processor is the ARM * SA-1 core with a 16 Kbyte instruction cache (Icache) and 8 Kbyte data cache

(Dcache). The instruction (I) and data (D) streams are translated through independent

memory-management units (MMUs). Stores are made using a four-line write buffer. The performance of

specialized load routines is enhanced with the four-entry read buffer that can be used to prefetch data for

use at a later time. A 16-entry minicache provides a smaller and logically separate data cache that can be

used to enhance caching performance when dealing with large data structures.

• Memory and PCMCIA Control Module

The memory and PCMCIA control module (MPCM) supports four banks of fast-page-mode (FPM),

extended-data-out (EDO), and/or synchronous DRAM (SDRAM). It also supports up to six banks of static

memory: all six banks allow ROM or Flash memory, each with non-burst or burst read timings.

Additionally, the lower three static banks support SRAM, the upper three static banks support variable

latency I/O devices (with the variable data latency controlled by a shared data ready input), and the lower

four static banks support synchronous mask ROM (SMROM). SMROM is supported only on 32-bit data

busses. All other dynamic and static memory types and variable latency I/O devices are supported on eithe

16-bit or 32-bit data busses. Expansion devices are supported through PCMCIA control signals that share

the memory bus data and address lines to complete the card interface. Some external glue logic (buffers and

transceivers) is necessary to implement the interface. Control is provided to permit two card slots with

hot-swap capability.

• Peripheral Control Module

The peripheral control module (PCM) contains a number of serial control devices, an LCD controller as

well as a six-channel DMA controller to provide service to these devices:

An LCD controller with support for passive or active displays

A universal serial bus (USB) endpoint controller

A serial controller with supporting 115 Kbps and 4 Mbps IrDA protocols

A 16550-like UART supporting 230 Kbps

A CODEC interface supporting Motorola SPI,National Microwire, TI Synchronous Serial, or the

Philli

s UCB1100 and UCB1200

rotocol