Page 2 of 59

nRF51822 Development Kit User Guide v1.0

Contents

1 Introduction............................................................................................................................................... 4

1.1 Minimum requirements................................................................................................................................. 4

1.2 External resources ............................................................................................................................................ 4

1.3 Writing conventions........................................................................................................................................ 4

1.4 Development kit release notes.................................................................................................................... 4

2 Quick start.................................................................................................................................................. 5

2.1 Bluetooth low energy heart rate monitor demo .................................................................................. 9

3 Kit content................................................................................................................................................ 11

3.1 nRF51822 Development kit hardware content...................................................................................11

3.2 Downloadable content ................................................................................................................................12

3.2.1 nRF51822 DK software content..........................................................................................................12

3.2.2 nRF51822 DK documentation.............................................................................................................12

3.2.3 Schematics, Bill of Materials, PCB layout files, and production files......................................12

4 Development kit configuration ........................................................................................................... 13

4.1 Development environment........................................................................................................................13

4.1.1 Programming the nRF51822 device .................................................................................................13

4.2 Kit set up ............................................................................................................................................................16

4.2.1 nRFgo nRF51822 DK modules.............................................................................................................16

4.2.2 nRF51822 development dongle (PCA10000) ................................................................................17

4.2.3 J-Link Lite CortexM-9 JTAG/SWD Emulator....................................................................................17

5 Hardware description ............................................................................................................................ 18

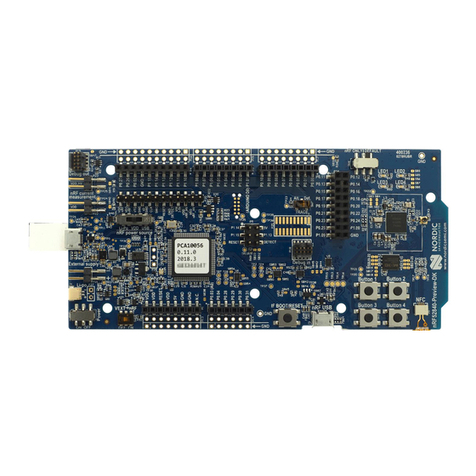

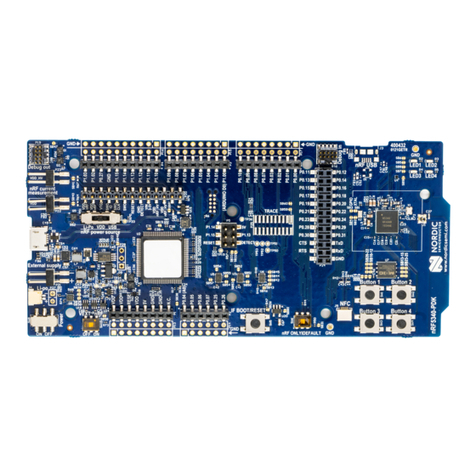

5.1 nRFgo nRF51822 DK modules ...................................................................................................................18

5.1.1 Key features................................................................................................................................................18

5.1.2 Hardware pictures ...................................................................................................................................18

5.1.3 Block diagram ...........................................................................................................................................20

5.1.4 nRFgo nRF51822 DK module extension..........................................................................................21

5.1.5 Analog Inputs............................................................................................................................................22

5.1.6 SWD interface............................................................................................................................................22

5.1.7 32.768 kHz crystal ....................................................................................................................................23

5.1.8 Current measurements..........................................................................................................................24

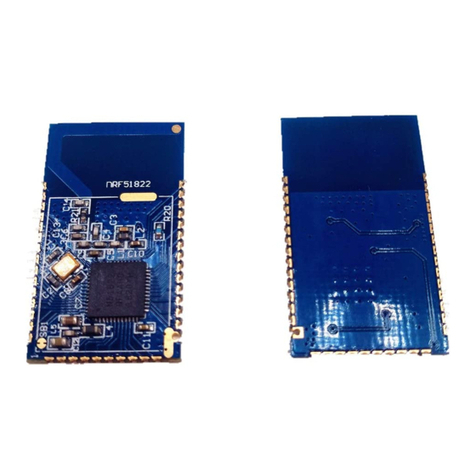

5.2 nRF51822 development dongle(PCA10000)........................................................................................25

5.2.1 Key features................................................................................................................................................25

5.2.2 Hardware pictures ...................................................................................................................................25

5.2.3 Block diagram ...........................................................................................................................................26

6 Flash programming and application development......................................................................... 27

6.1 Programming and erasing flash using nRFgo Studio .......................................................................27

6.1.1 Selecting a board to program .............................................................................................................27

6.1.2 Identifying the nRF51 chip and chip content................................................................................27

6.1.3 Erasing All ...................................................................................................................................................29

6.1.4 Programming a SoftDevice ..................................................................................................................30

6.1.5 Programming an application ..............................................................................................................31

6.2 Application development ...........................................................................................................................32

6.2.1 Configuring memory layout ................................................................................................................32

6.2.2 Shared call stack.......................................................................................................................................35

6.2.3 Debugger configuration .......................................................................................................................36

6.2.4 Limitation when debugging on a chip with a SoftDevice ........................................................38