5

4. OPERATING INSTRUCTIONS

4.1 introduction to Fast Timing with Linear Signals

The precise determination of the time of a nuclear event,

simultaneous with the mea~uramant of its energy, hasbeen

restricted in the past to two timing techniques - zero

crossing and level discrimination. In the zero-crossing

method the timing SCA simply detects the time at which

a bipolar linear signal crosses the baseline. For a double-

delay-line shaped signal the zero-crossing phase point con-

tains the same information as the 50% charge collection

time on the leading edge of the signal. For some signals the

zero-crossing point provides excellent time resolution.

There are two rather savera limitations to~the zero-crossing

technique. First, the amplitude n&e of a bipolar signal is

normally worse than a similarly shaped unipolar signal.

Consequently, the edges of the energy window set by the

SCA are not as precise as they would be for a unipolar signal.

The second limitation of the zero-crossing technique is

that the time information cannot be obtained until the

signal crosses the baseline. The added time delay before

getting the time information is not a savera limitation in

DDL applications, but for simulated Gaussian-shaped signals

the added delay may be several microseconds.

A simple level discriminator is used to obtain time infor-

mation by the second technique. The usual mode of

operation allows the level discriminator to trigger on the

leading edge of the signal and to then reset when the signal

falls below the discrimi,nator level. Either of these trigger

points can be used for the timing information. If the

leadingedge trigger point is used, it must be delayed beyond

the peak of the input signal for the single-channel ampli-

tude decision to bemade. The basic limitation of this system

is that it introduces a time walk due to changing signal

amplitudes, and the magnitude of the walk is usuallyequal

to approximately the rise time of the signal. For different

types of signals this walk will range from tens of nano-

seconds to microseconds.

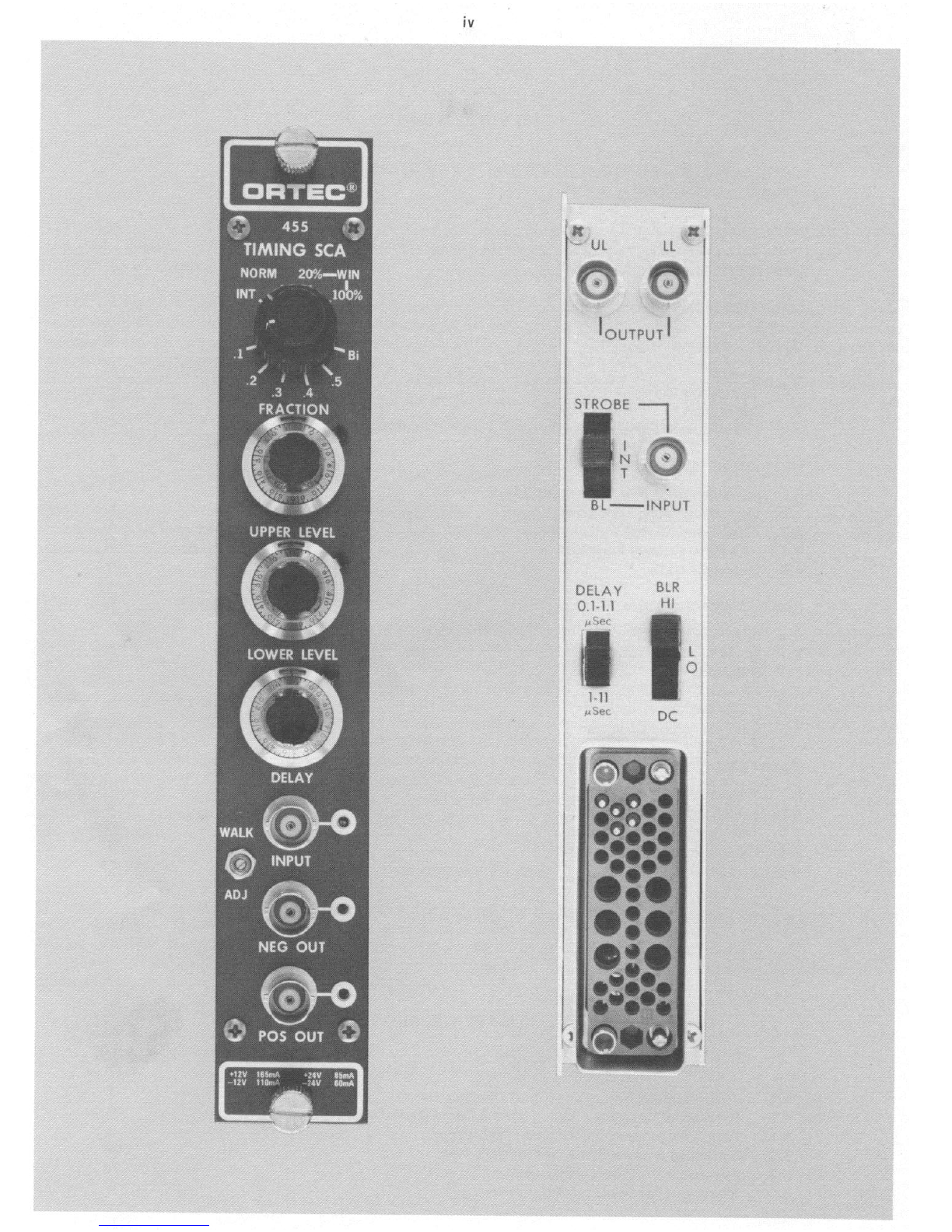

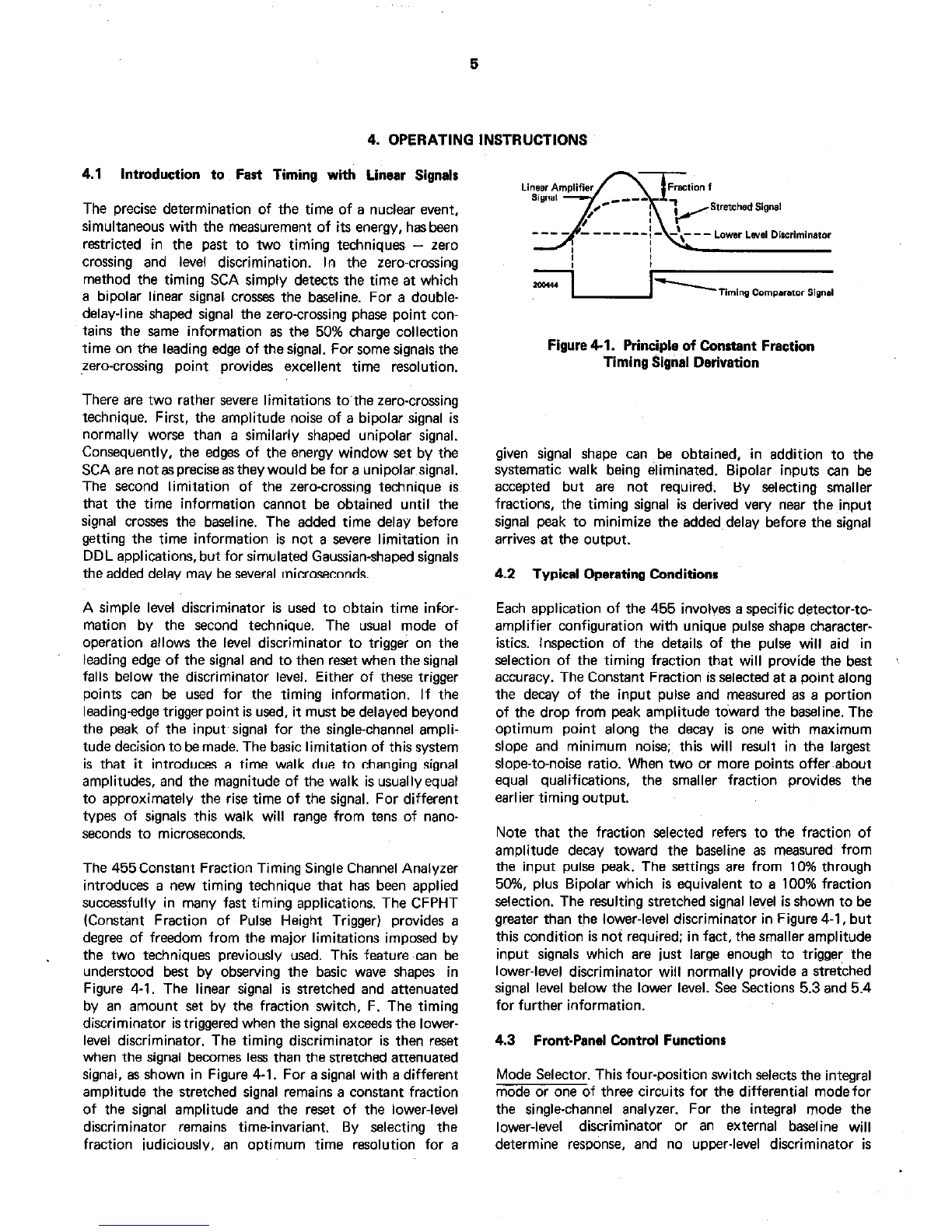

The 455Constant Fraction Timing Single Channel Analyzer

introduces a new timing technique that has been applied

successfully in many fast timing applications. The CFPHT

(Constant Fraction of Pulse Height Trigger) provides a

degree of freedom from the major limitations imposed by

the two techniques previously used. This feature can be

understood best by observing the basic wave shapes in

Figure 4-1. The linear signal is stretched and attenuated

by an amount set by the fraction switch, F. The timing

discriminator is triggered when the signal exceeds the lower-

level discriminator. The timing discriminator is then rasat

when the signal becomes less than the stretched attenuated

signal, as shown in Figure 4-1. For a signal with a different

amplitude the stretched signal remains a cowsent fraction

of the signal amplitude and the re%et of the lower-level

discriminator remains timeinvariant. By selecting the

fraction judiciously, en optimum time rasolution for a

Figure 41. Principle of Constant Fraction

Timing Signal Derivation

given signal shape can be obtained, in addition to the

systematic walk being eliminated. Bipolar inputs can be

accepted but era not required. By selecting smaller

fractions, the timing signal is derived very near the input

signal peak to minimize the added~delay before the signal

arrives at the output.

4.2 Typical Operating Conditions

Each application of the 455 involves a specific datector-to-

amplifier configuration with unique pulse shape character-

istics. inspection of the details of the pulse will aid in

Selection of the timing fraction that will provide the best

accuracy. The Constant Fraction is selected at a point along

the decay of the input pulse and measured as a portion

of the drop from peak amplitude toward the baseline. The

optimum point along the decay is one with maximum

slope and minimum noise; this will rasult in the largest

slope-to-noise ratio. When two or more points offer~about

equal qualifications, the smaller fraction provides the

earlier timing output.

Note that the fraction selected refers to the fraction of

amplitude decay toward the baseline as measured from

the input pulse peak. The settings are from 10% through

50%. plus Bipolar which is equivalent to a 100% fraction

selection. The resulting stretched signal level is shown to be

greater than the lower-level discriminator in Figure 4-1, but

this condition is not required; in fact, the smaller amplitude

input signals which are just large enough to trigger the

lower-level discriminator will normally provide a stretched

signal level below the lower level. See Sections 5.3 and 5.4

for further information.

4.3 Front-Panel Control Functions

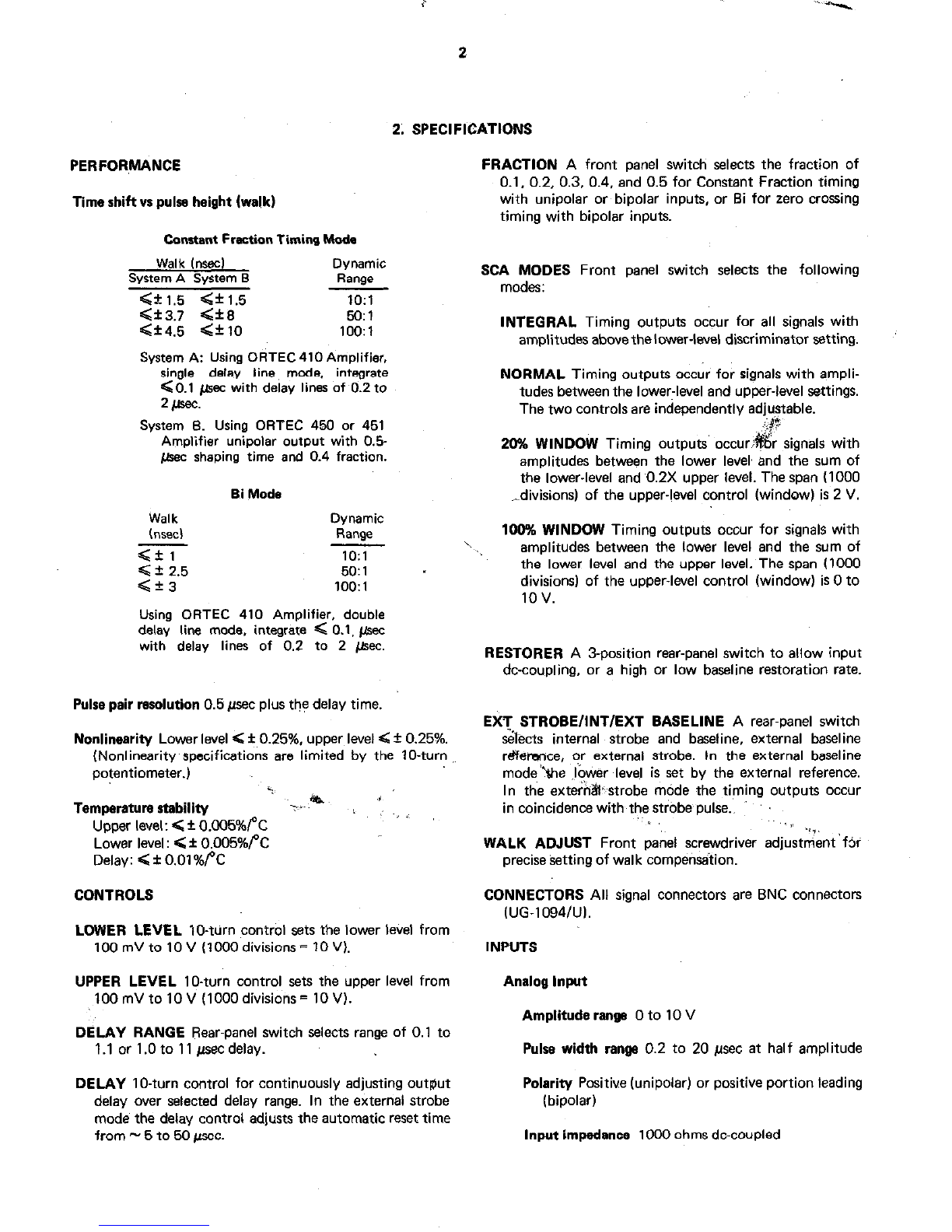

Mode Selector. This four-position switch ?elects the integral

mode or one of three circuits for the differential modefor

the single-channel analyzer. For the integral mode the

lower-level discriminator or an external baseline will

determine response, and no upper-level discriminator is