Contents

PHYTEC Messtechnik GmbH 2020 L-807e.A2 i

List of Figures..................................................................................................iii

List of Tables ................................................................................................... iv

Conventions, Abbreviations and Acronyms .............................................................. v

Preface ........................................................................................................ viii

1Introduction............................................................................................ 11

1.1 Features of the phyCORE-MPC5676/57x ............................................................11

1.1.1 Internal Features of the MPC5676R.......................................................12

1.2 Memory Configuration of the phyCORE-MPC5676/57xx .......................................12

1.3 Other Board-Level Features............................................................................12

1.4 Block Diagram.............................................................................................13

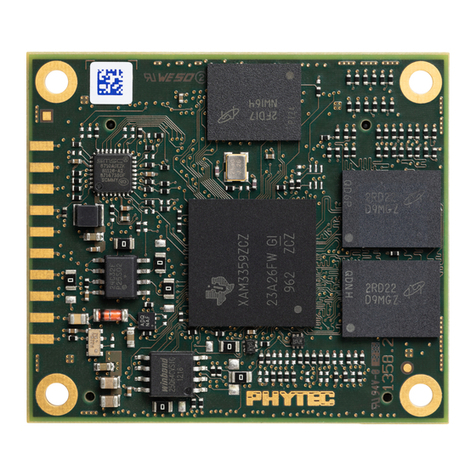

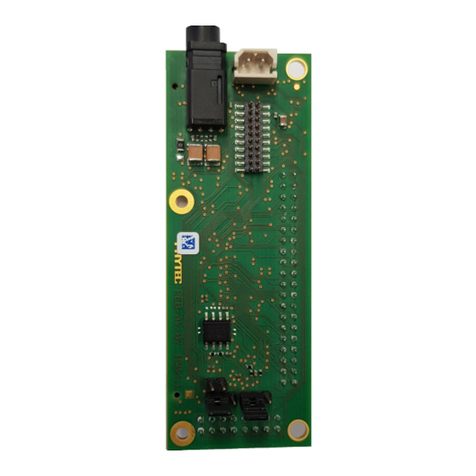

1.5 phyCORE-MPC5676/57xx Component Placement ................................................14

1.6 Minimum Requirements to operate the phyCORE-MPC5676/57xx ...........................16

1.6.1 phyCORE-MPC5676/57xx without FPGA .................................................16

1.6.2 phyCORE-MPC5676/57xx with FPGA ......................................................16

2Pin Description......................................................................................... 17

3Jumpers ................................................................................................. 34

4Power Requirements.................................................................................. 44

4.1 Voltage Supervisor and Reset .........................................................................45

5System Configuration and Booting................................................................ 46

6System Memory ........................................................................................ 47

6.1 External Standard Flash Memory (U100,U101)...................................................47

6.2 Synchronous Burst SRAM(U102,U103) .............................................................48

6.3 SPI EEPROM (U6) .........................................................................................49

6.3.1 EEPROM Write Protection Control (J30) .................................................49

6.4 SPI Flash Memory (U19) ................................................................................49

7FPGA System Logic Device U18 ..................................................................... 50

7.1 Addressing the FPGA from MPC .......................................................................50

7.2 Configuration of the FPGA..............................................................................50

7.3 FPGA connector X3 .......................................................................................50

8Serial Interfaces....................................................................................... 51

8.1 Universal Asynchronous Interface ...................................................................51

8.2 CAN Interface..............................................................................................52

8.3 SPI Interface...............................................................................................52

9LAN9221I Ethernet Controller...................................................................... 53

9.1 Ethernet Transformer....................................................................................53

9.2 Addressing the Ethernet Controller..................................................................54

9.2.1 Software Reset of the Ethernet Controller ..............................................54

9.3 MAC Address ...............................................................................................54

10 Real-Time Clock M41T93 (U7) ...................................................................... 55

11 JTAG/OnCE/Nexus Debufg Interface .............................................................. 56

12 Technical Specifications ............................................................................. 57

13 Hints for Integrating and Handling the phyCORE-MPC5676/57xx ......................... 60

13.1 Integrating the phyCORE-MPC5676/57xx..........................................................60

13.2 Handling the phyCORE-MPC5676/57xx.............................................................60

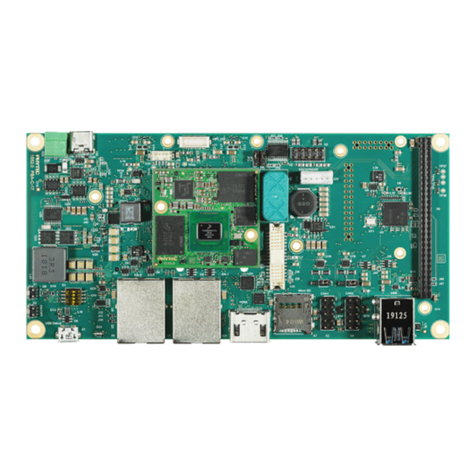

14 The phyCORE- MPC5676R on the phyCORE Carrier Board ..................................... 61