Contents

PHYTEC Messtechnik GmbH 2006 L-672e_0

Preface...........................................................................................................1

1Introduction.........................................................................................3

1.1 Block Diagram .............................................................................6

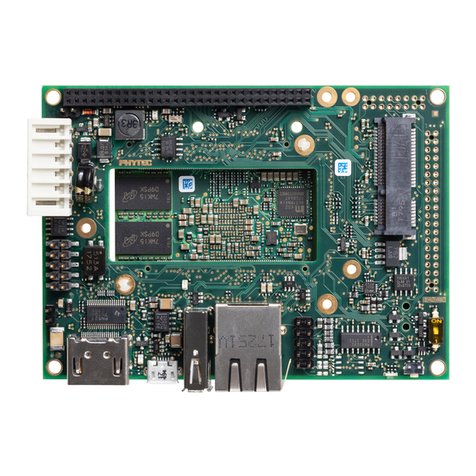

1.2 View of the phyCORE-MPC5200B.............................................7

1.3 Minimum Requirements to Operate the

phyCORE-MPC5200B.................................................................9

2Pin Description..................................................................................11

3Jumpers..............................................................................................23

4Power Requirements.........................................................................27

4.1 Voltage Supervision and Reset ..................................................29

5System Start-Up Configuration.......................................................31

6System Memory.................................................................................33

6.1 Flash Memory ............................................................................35

6.2 DDR SDRAM ............................................................................38

6.3 SRAM (U15)..............................................................................39

6.4 Serial Memory............................................................................40

6.5 NAND-Flash (U28)....................................................................41

6.6 Video-RAM (U20).....................................................................41

7Altera Cyclone II FPGA...................................................................43

8Serial Interfaces.................................................................................45

8.1 RS-232 Interface ........................................................................45

8.2 CAN Interface ............................................................................46

8.3 COP Debug Interface .................................................................47

8.4 Ethernet Interface.......................................................................49

8.4.1 PHY Physical Layer Transceiver..................................49

8.4.2 MAC Address................................................................50

8.5 USB 1.1 Host Interface ..............................................................51

9Real-Time Clock RTC-8564 (U7)....................................................53

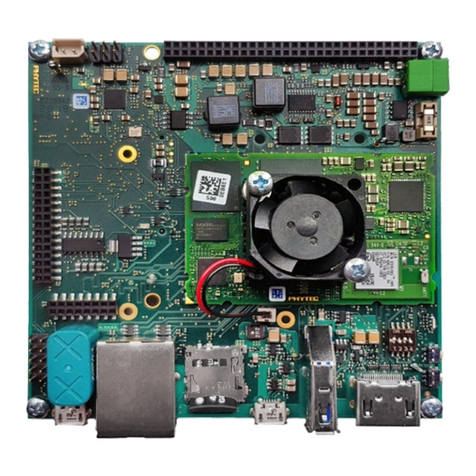

10 phyCORE Carrier Board PCM-980 ...............................................55

10.1 Concept of the phyCORE Carrier Board PCM-980...................55

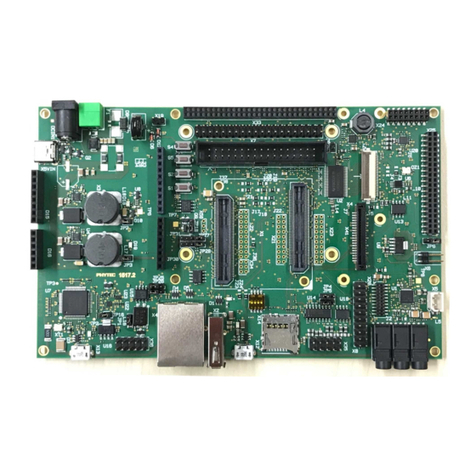

10.2 Carrier Board PCM-980 Overview............................................56

10.2.1 Connectors, Buttons, LEDs...........................................56

10.2.2 Jumpers on the phyCORE Carrier Board PCM-980.....59