Contents

PHYTEC Messtechnik GmbH 2005 L-645e_1

Preface...........................................................................................................1

1 Introduction .........................................................................................3

1.1 Block Diagram..............................................................................6

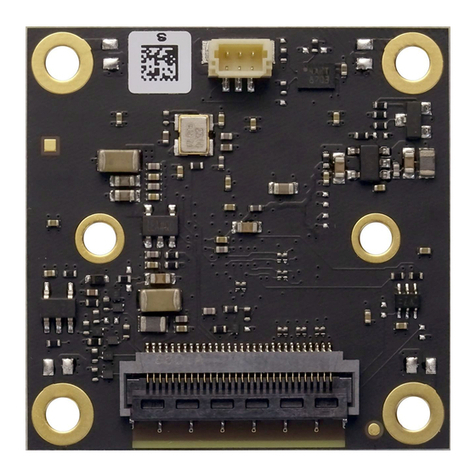

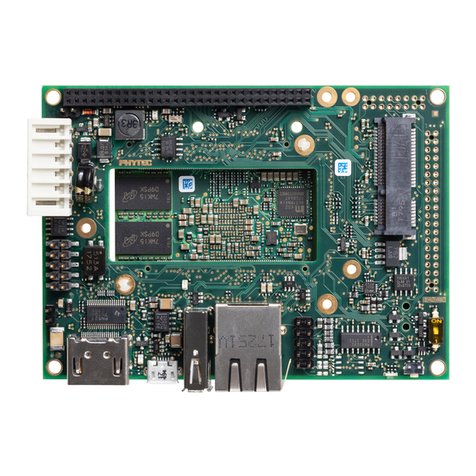

1.2 View of the phyCORE-MCF548x................................................7

1.3 Minimum Requirements to Operate the phyCORE-MCF548x....8

2 Pin Description ....................................................................................9

3 Jumpers..............................................................................................23

4 Power Requirements.........................................................................33

4.1 Voltage Supervision and Reset...................................................35

5 System Start-Up Configuration .......................................................37

6 System Memory.................................................................................39

6.1 Flash Memory.............................................................................40

6.2 DDR SDRAM.............................................................................42

6.3 Serial Memory............................................................................43

7 XPLD System Logic Device..............................................................45

7.1 XPLD Firmware Development...................................................46

8 Serial Interfaces.................................................................................47

8.1 RS-232 Interface.........................................................................47

8.2 CAN Interface.............................................................................48

8.3 BDM Debug Interface ................................................................50

8.4 Ethernet Interface .......................................................................52

8.4.1 PHY Physical Layer Transceiver ..................................52

8.4.2 MAC Address................................................................54

8.5 USB 2.0 Interface.......................................................................54

9 Real-Time Clock RTC-8564 (U16)...................................................55

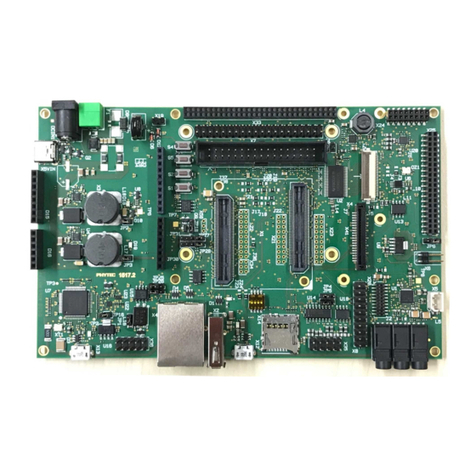

10 phyCORE Development Board PCM-982 ......................................57

10.1 Concept of the phyCORE Development Board PCM-982.........57

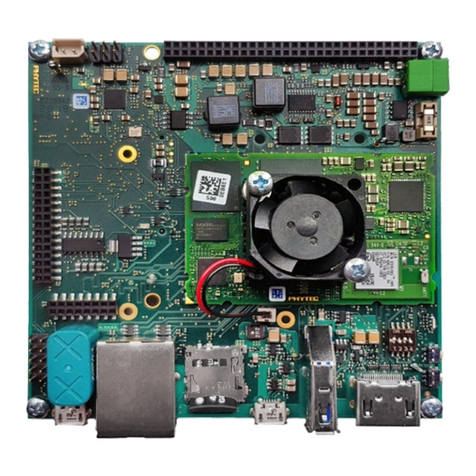

10.2 Development Board PCM-982 Overview ..................................58

10.2.1 Connectors, Buttons, LEDs...........................................58

10.2.2 Jumpers on the phyCORE Development Board

PCM-982 .......................................................................61