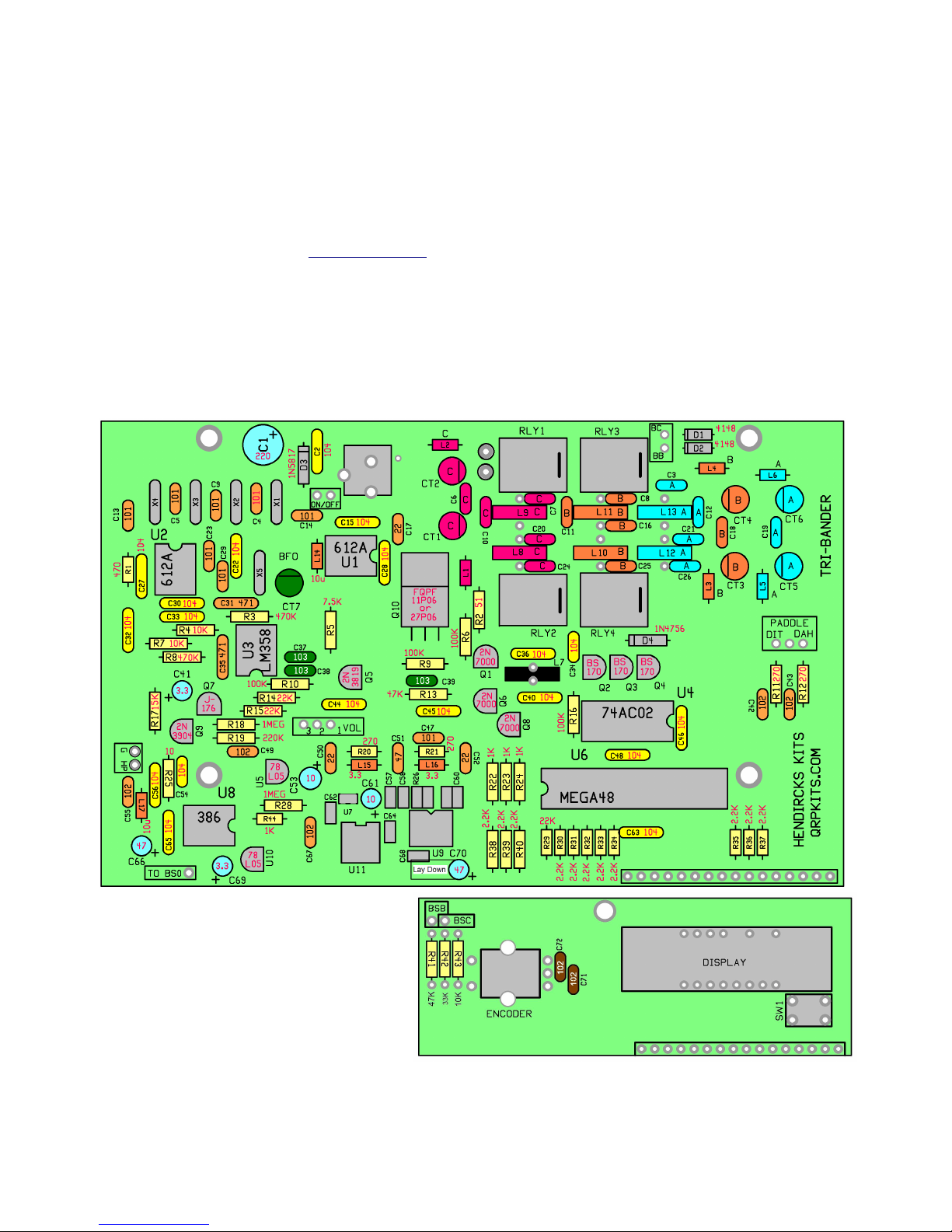

receive switching and prod ces the side tone. An Analog Devices AD9834 DDS chip is sed for the VFO. Using a 60 MHz

clock, direct freq ency o tp t to 21 MHz is possible.

Receiver:

The receiver is a classic SA612 circ it, widely sed in QRP rigs. The 1st mixer inp t is do ble t ned for good image and o t

of band signal rejection. A fo r crystal IF filter sing matched crystals provides good selectivity and opposite side band

rejection. The se of fo r crystals and low profile HU-49US crystals res lts in noticeably better performance than three

crystal filters sing the tall, HU-49U crystals.

The o tp t of the prod ct detector, U2 is first amplified by a differential inp t amplifier, U3b. The second section of U3a is

sed as an a dio band pass filter with a pass band centered at 600 Hz. This a dio filter, in addition to removing high

freq ency hiss, adds some gain. The a dio is m ted d ring transmit by the series connected N-channel JFET Q5.

U8, a LM386 a dio amp provides final gain. In addition to headphones, it is able to drive a small, 8 ohm speaker. An a dio

AGC circ it is b ilt aro nd the a dio amp to limit the o tp t vol me to help protect yo r ears if the vol me is t rned all

the way p and yo t ne across a strong station. The o tp t level is limited to 800 mv p-p or abo t 10 mw rms.

AGC Circ it: The a dio o tp t of U8 is co pled to base of Q9. Q9 has a little bias voltage of abo t 400 mv applied to it via

the resistor divider R19/R17. This allows AGC action to start when the a dio level from U8 starts to exceed 400 mv instead

of 600 mv, the normal t rn on voltage for a NPN silicon transistor. Q7 is a P-channel JFET and is sed to atten ate the

a dio signal going into U8 from the vol me control. A 22K resistor, R15 is in series with the vol me control wiper and the

inp t to U8 so that Q7 has a dropping resistor to work against if the vol me control is t rned all the way p.

As the a dio o tp t level of U8 starts to exceed 400 mv, Q9 starts to t rn on, red cing the voltage at Q7's gate and

thereby starting to t rn Q7 on and atten ate the inp t signal to the amplifier. The gate voltage of Q7 will find a level at

which it will keep the o tp t voltage of U8 at 400 mv peak. C41 at Q7's gate holds the AGC voltage steady.

One common problem with a dio derived AGC circ its is “th mping” d e to the circ it being a little slow to act on the

leading edge of a signal and then “over shooting”, red cing the gain too m ch. The circ it sed here is remarkably free of

those ndesirable effects.

Transmitter:

The transmitter is as simple as it can get. The AD9834 DDS chip incl des a b ilt in comparator, which when enabled d ring

transmit, directly prod ces a sq are wave o tp t. This is then b ffered by three OR gates in parallel, sing a high speed

74AC02 logic chip, which in t rn drives three BS-170 MOSFET's in parallel.

The sq are wave drive to the MOSFETs prod ces fast t rn on and t rn off times. This, combined with the low “ON”

resistance and impedance matching achieved by the Low Pass o tp t filter, res lts in a reasonably high PA efficiency of

abo t 75%. This makes it possible to prod ce 5 watts of o tp t power sing three plastic TO-92 devices with no heat

sinking. Something not easily achieved with a traditional analog amplifier chain sing bi-polar transistors. The se of a

high speed logic gate to drive the PA also res lts in a constant drive level, independent of freq ency, allowing a f ll 5 watt

o tp t on the higher bands with o t complicated freq ency compensation or drive adj stment controls.

The PA is keyed on and off with a P-channel MOSFET. A 0.01 fd cap between the Gate and Drain o tp t prod ces a 5 ms

rise and fall time to the keyed voltage for key click s ppression. The se of a MOSFET here instead of a PNP transistor

res lts in less voltage drop, easier control of the rise and fall times d e to the high impedance gate inp t.

5