1Overview................................................................1

1.1 Additional Support Documentation.......................1

1.2 Sightline Software Requirements ..........................1

2Safe Device Handling..............................................1

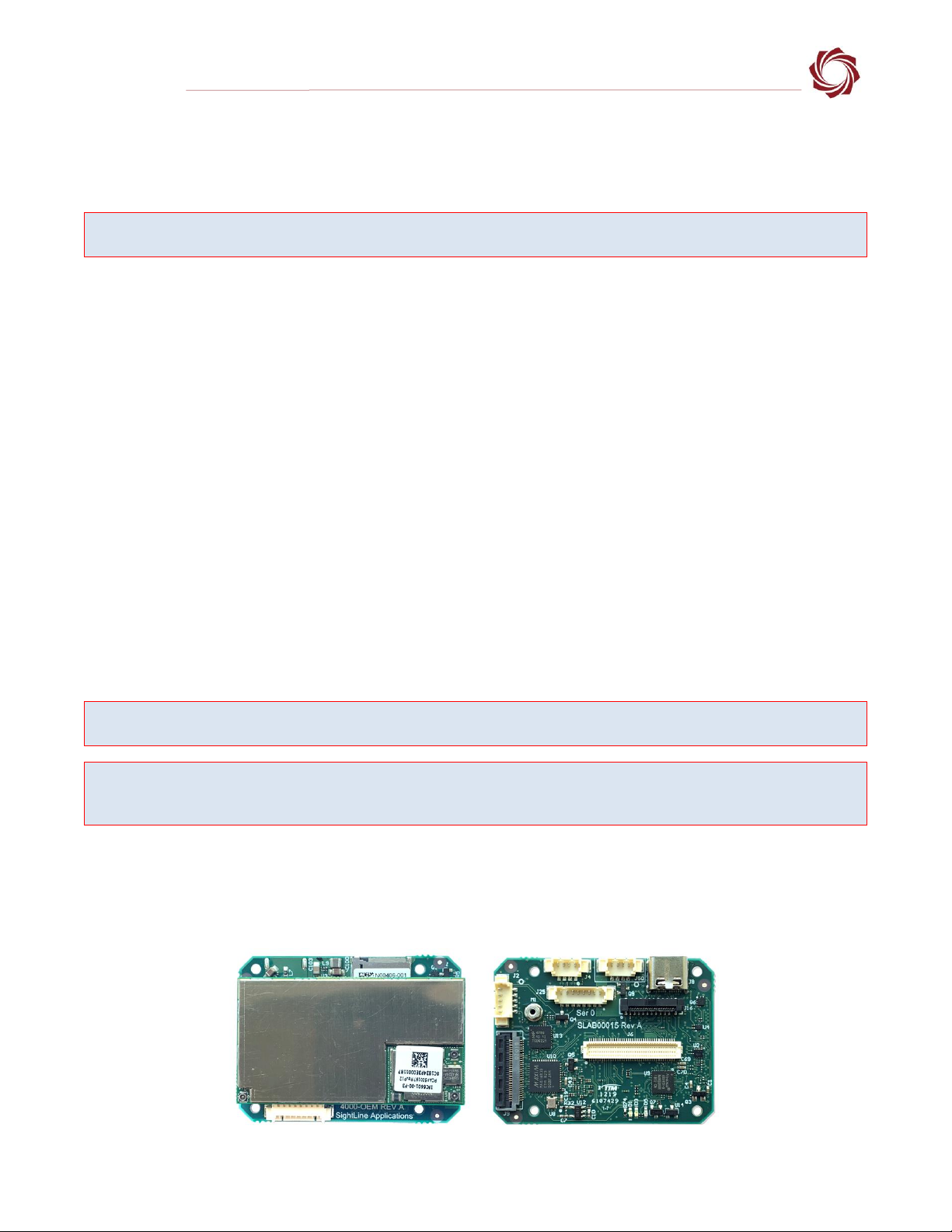

34000-OEM Overview..............................................1

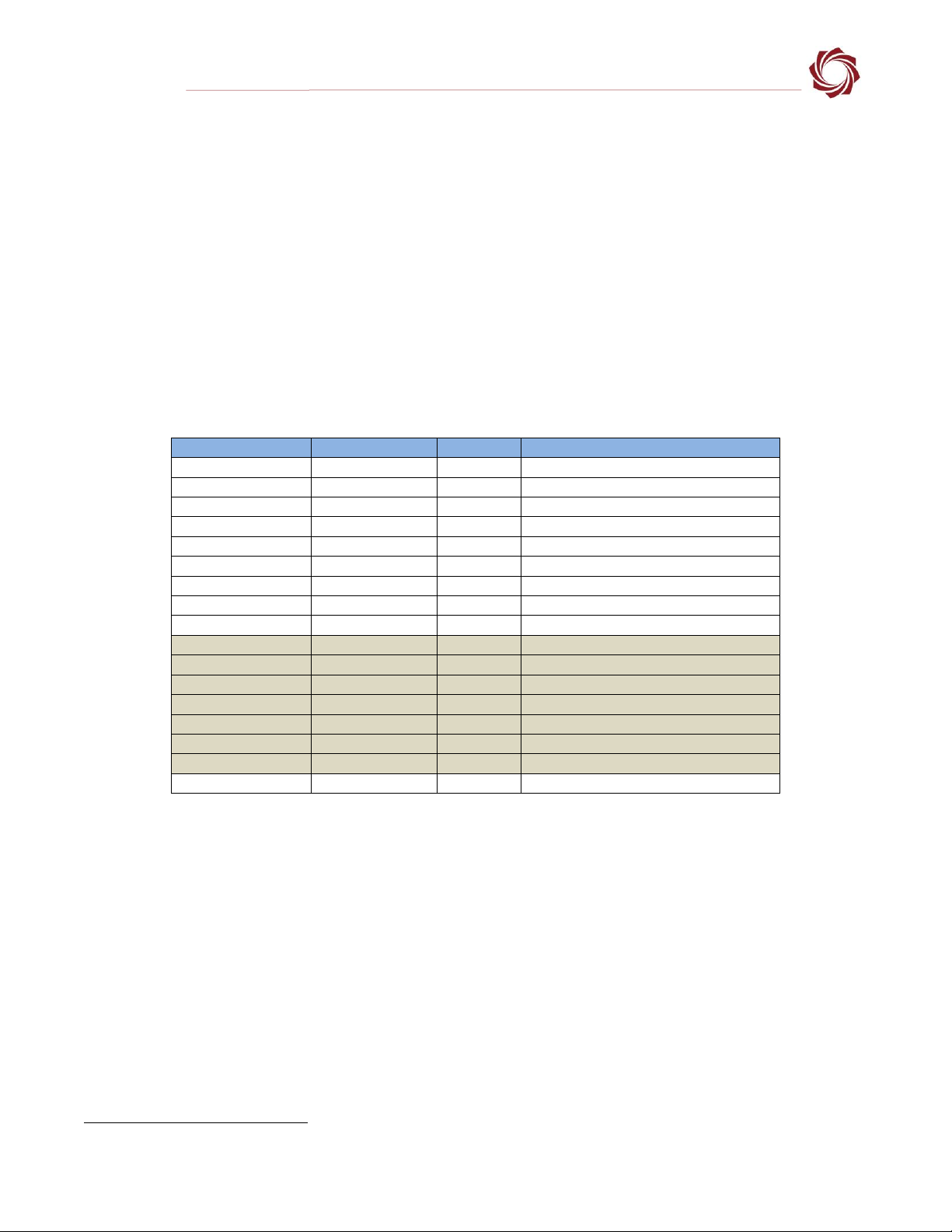

3.1 4000-OEM Specifications.......................................2

3.2 Interface Protocol ..................................................2

3.3 Functional Block Diagram ......................................2

3.4 Customer Integration - Key Points.........................3

4Thermal Management ...........................................3

4.1 Heatsink Guidelines ...............................................3

4.2 Gap Pads ................................................................3

4.2.1 Gap Pads SOM Cover .............................................3

4.2.2 Gap Pads Without SOM Cover...............................4

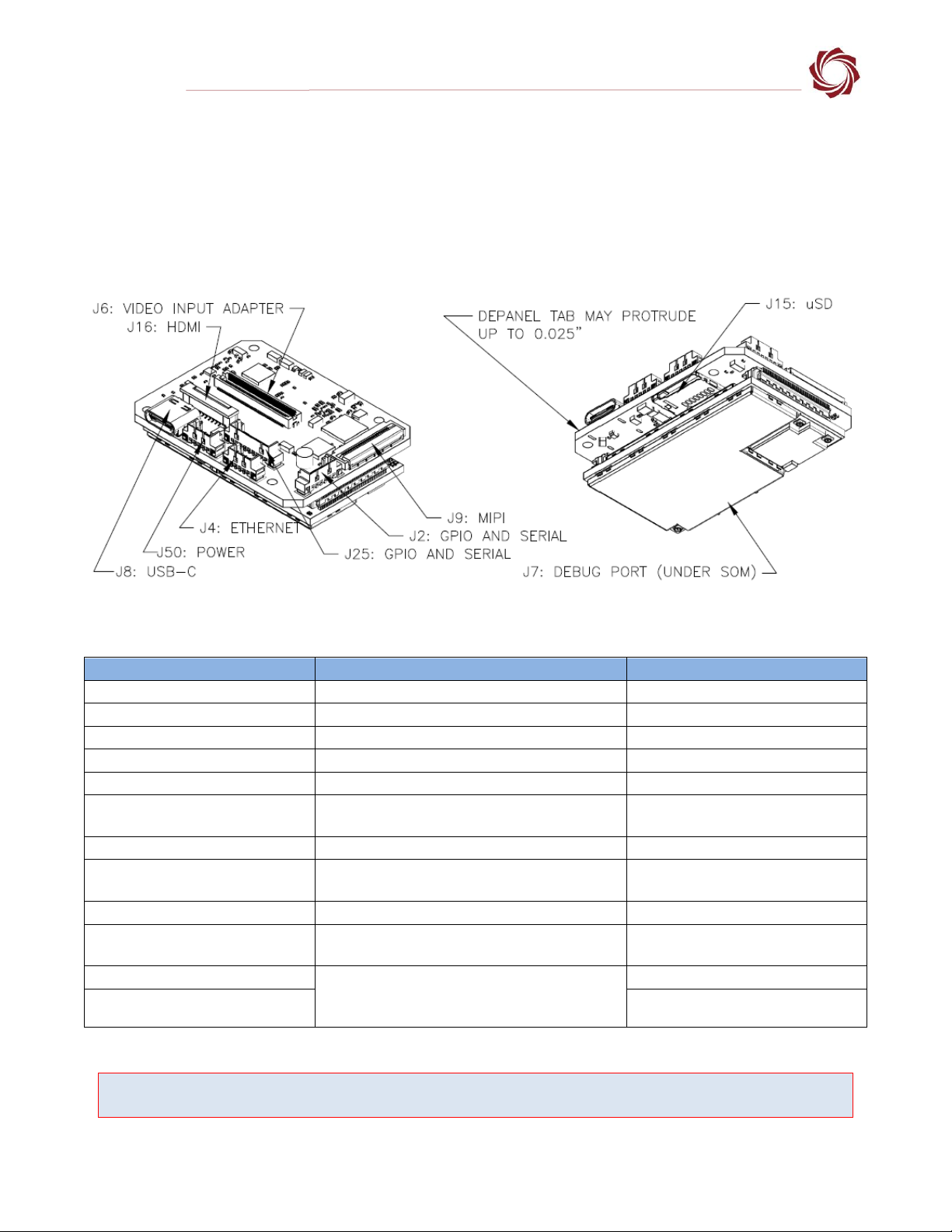

5Connector Descriptions..........................................4

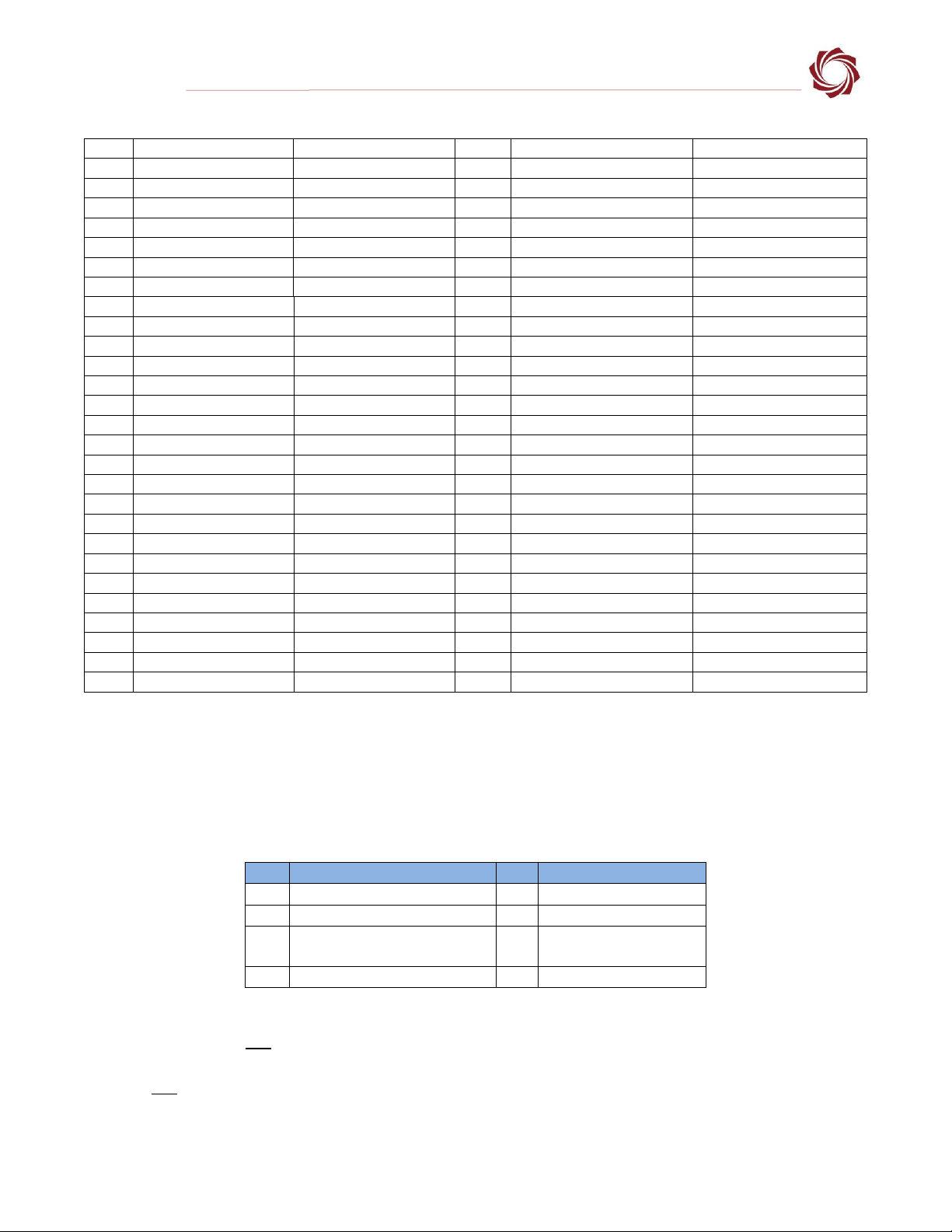

5.1 Connector J2: Serial Port / GPIO ...........................5

5.2 Connector J4: Ethernet 10/100..............................5

5.3 Connector J6: 3000/4000 Video Adapter Input ....5

5.4 Connector J7: 4000-DEBUG / Recovery ................6

5.5 Connector J8: USB 3.0 (Type-C)..............................7

5.6 Connector J9: MIPI Port (FFC connector)...............7

5.7 Connector J15: MicroSD.........................................8

5.8 Connector J16: HDMI Output Video (FFC

connector)..............................................................8

5.9 Connector J25: Additional Serial / GPIO................8

5.10 Connector J50: Power Connector ..........................9

6Additional I/O.........................................................9

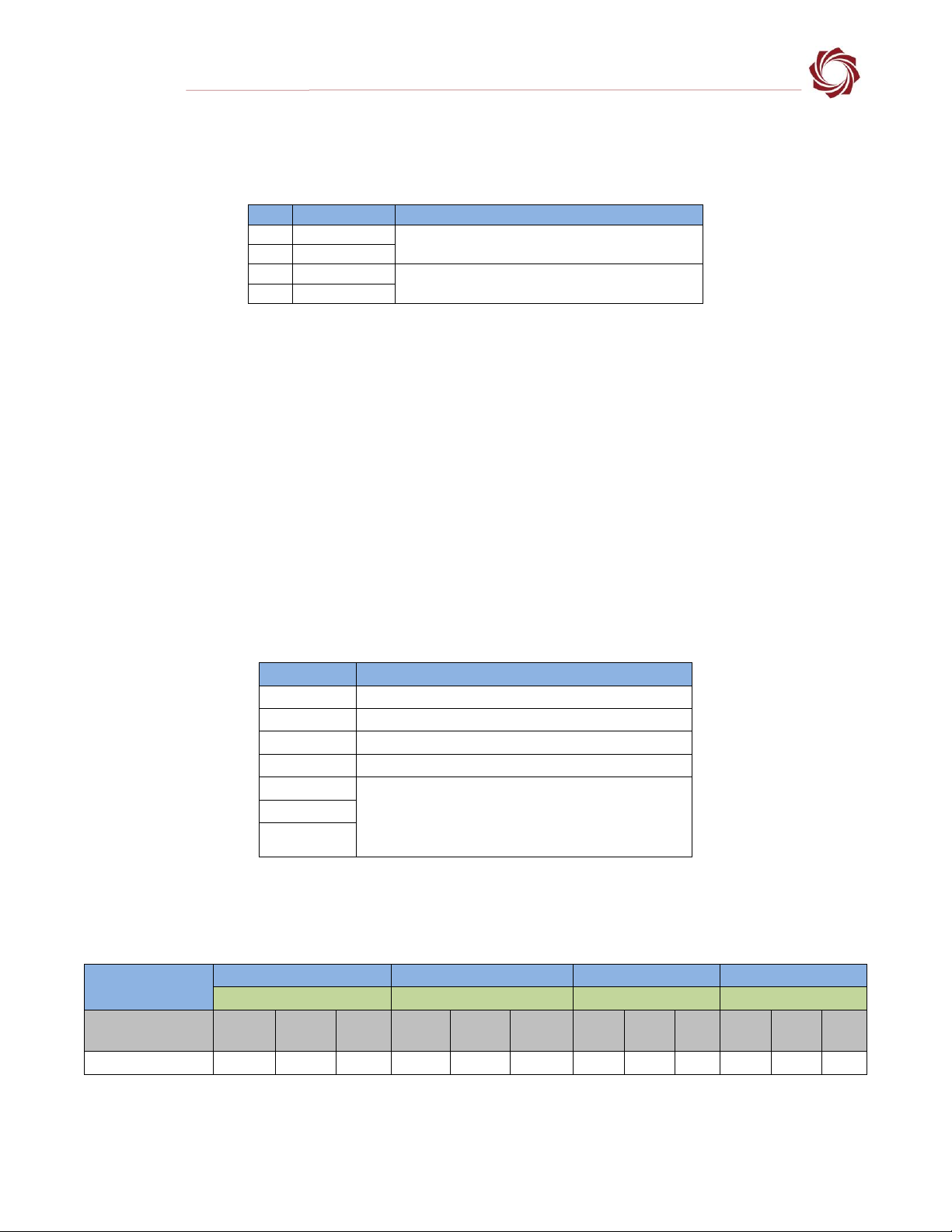

6.1 LED Summary .........................................................9

6.2 Serial Ports .............................................................9

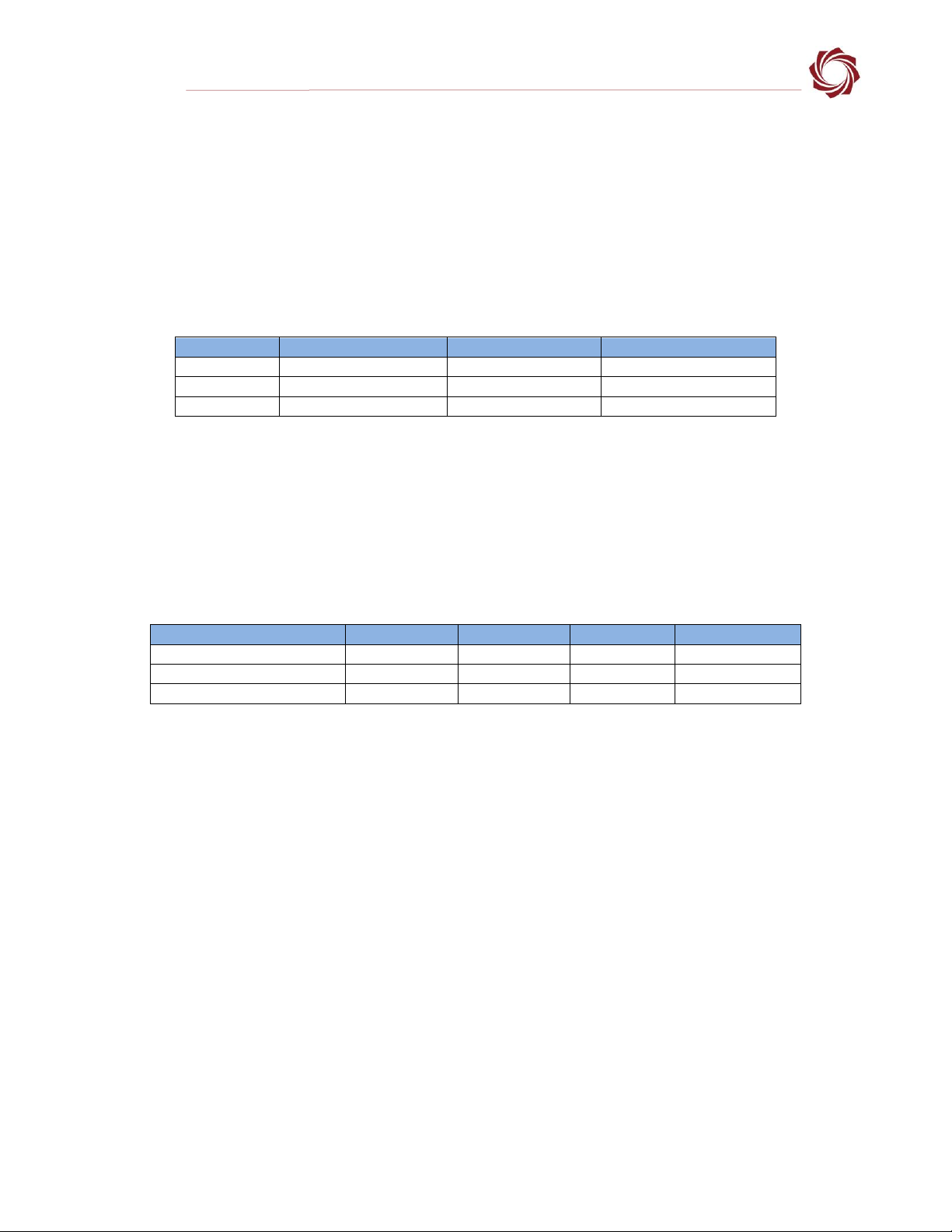

6.2.1 Serial Port Speed and Data Limits........................10

6.3 GPIO.....................................................................11

7Camera Naming Convention................................11

8Video Input Port J6 Details (Cam 0).....................12

8.1 Adapter boards ....................................................12

8.2 Camera Power Considerations.............................12

8.3 Signal Levels and Lattice Crosslink FPGA .............12

8.4 Supported Standards ...........................................12

8.5 Grayscale Camera Data........................................13

8.6 Synchronization Signals .......................................14

8.7 Camera Resolution and Pixel Clock

Requirements.......................................................14

8.8 Camera Pixel Clock Rate and MIPI Conversion ....14

8.9 Horizontal Blanking Requirements ......................15

8.9.1 Width and Height Requirements .........................16

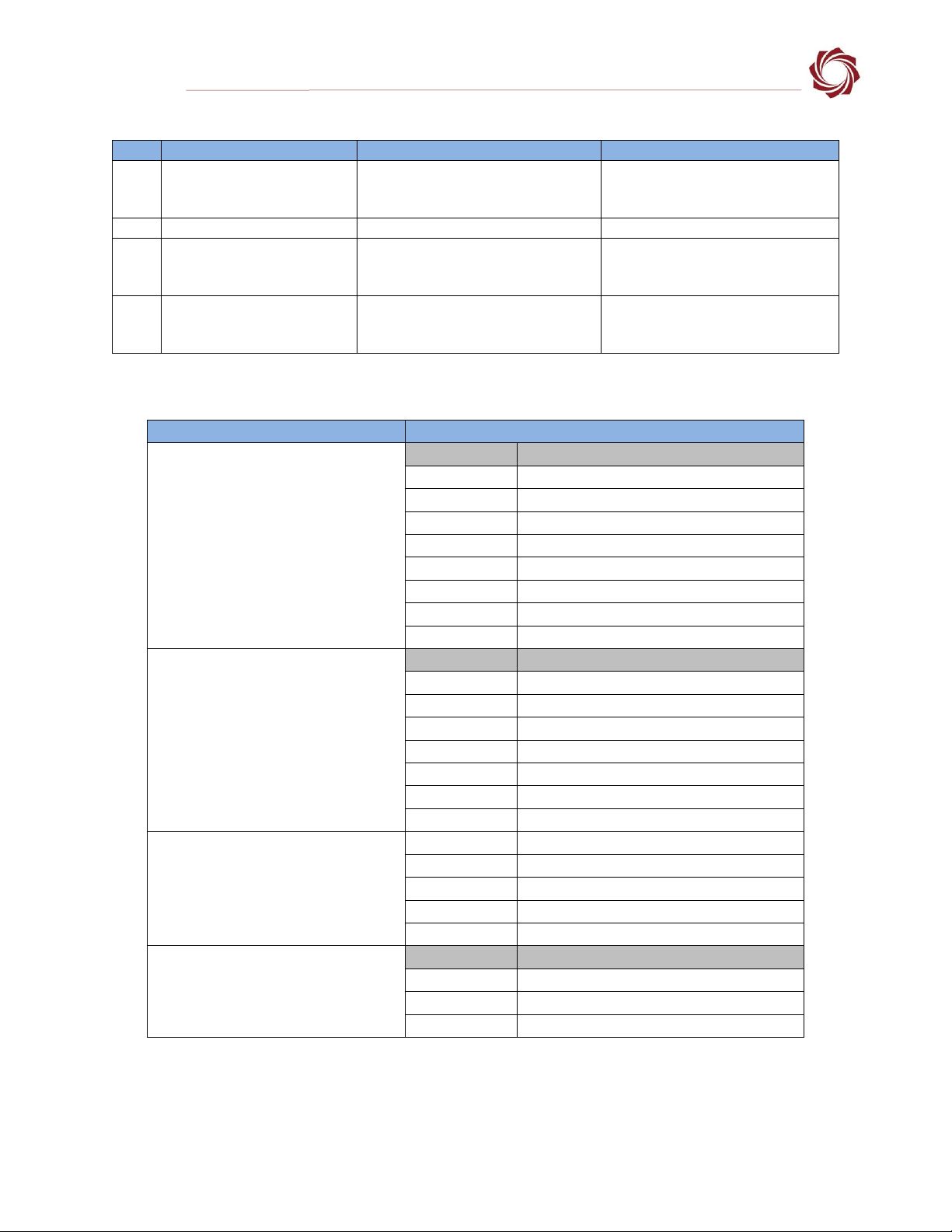

8.10 Additional FPGA Versions and naming ................16

8.11 Maximum Width and Height................................16

9MIPI Port J9 (Cam 1) ............................................16

10 Camera Input Adapter Board IDs.........................16

11 4000-DEBUG ........................................................17

11.1 Debug Board Specifications .................................17

12 Customer Designed 4000-OEM Boards and Camera

Interface Options .................................................19

12.1 Using the Lattice FPGA.........................................19

12.2 Not Using the Lattice FPGA..................................19

12.3 MIPI Camera Data Acquisition .............................19

13 Questions and Additional Support.......................19

CAUTION: Alerts to a potential hazard that may result in personal injury, or an unsafe practice that causes damage to the equipment

if not avoided

IMPORTANT: Identifies crucial information that is important to setup and configuration procedures.

Used to emphasize points or reminds the user of something. Supplementary information that aids in the use or understanding of the

equipment or subject that is not critical to system use.